概述

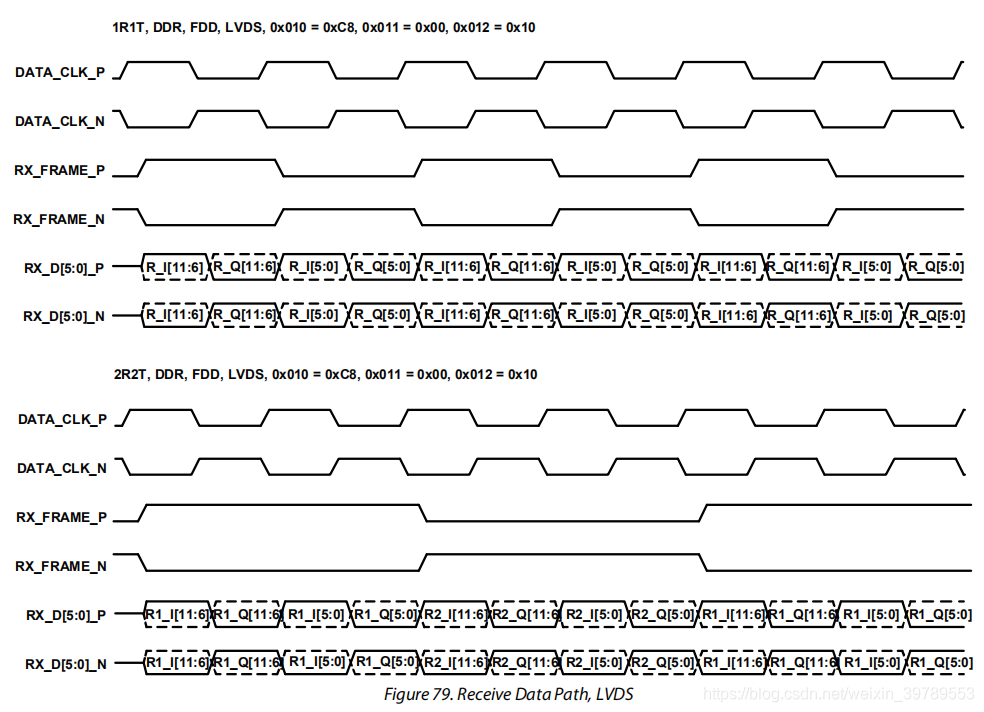

AD9361数据接口采用了DDR双沿采样模式,如下所示,AD9361与Xilinx FPGA通信需要用到其IDDR和ODDR原语,为加深记忆,将IDDR及ODDR使用总结如下。

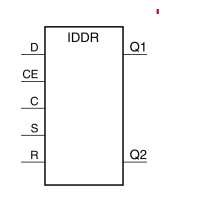

IDDR

IDDR是将1 bit的双沿采样输入转换为2bit的单沿采样输出,IDDR框图如下图所示,其中D为双沿采样输入端,C为时钟输入,CE为时钟使能,S为置位信号,R为复位信号,Q1和Q2单沿采样输出端。

IDDR #(

.DDR_CLK_EDGE ("SAME_EDGE_PIPELINED" ),

.INIT_Q1 (1'b0 ),

.INIT_Q2 (1'b0 ),

.SRTYPE ("ASYNC" ))

i_rx_frame_iddr (

.CE (1'b1 ),

.R (1'b0 ),

.S (1'b0 ),

.C (data_clk ),

.D (rx_frame_idelay ),

.Q1 (rx_frame_p_s ),

.Q2 (rx_frame_n_s ));

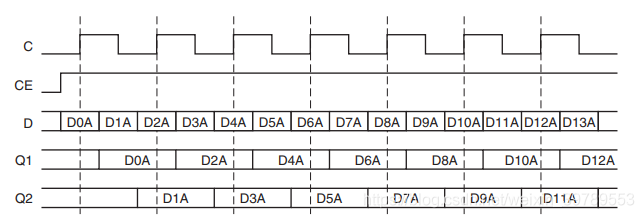

从上面例化的模块说明IDDR的参数,其中INIT_Q1和INIT_Q1为输出初始值,SRTYPE表示同步或异步复位,而DDR_CLK_EDGE有以下三种模式:

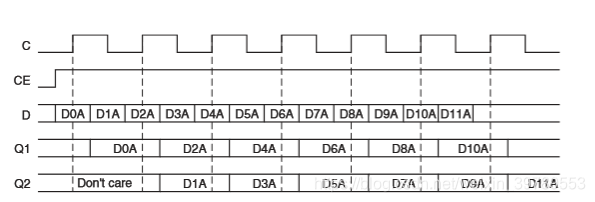

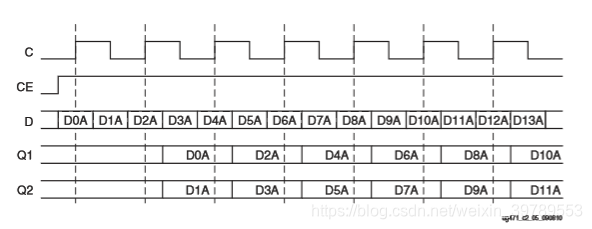

1、OPPOSITE_EDGE模式

2、SAME_EDGE Mode

3、SAME_EDGE_PIPELINED模式

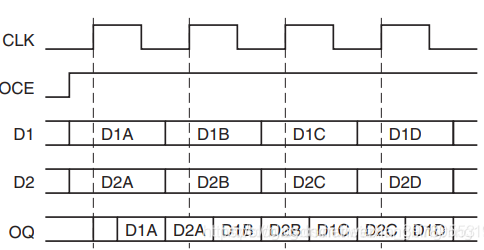

ODDR

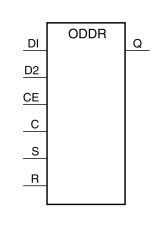

ODDR是将2bit单沿采样输入转换为1bit的双沿采样输出,ODDR框图如下图所示,其中D1和D1为单沿采样输入端,C为时钟输入,CE为时钟使能,S为置位信号,R为复位信号,Q为双沿采样输出端。

ODDR #(

.DDR_CLK_EDGE ("SAME_EDGE" ),

.INIT (1'b0 ),

.SRTYPE ("ASYNC" ))

i_tx_frame_oddr (

.CE (1'b1 ),

.R (1'b0 ),

.S (1'b0 ),

.C (data_clk ),

.D1 (tx_frame ),

.D2 (tx_frame ),

.Q (tx_frame_oddr_s ));

从上面例化的模块说明ODDR的参数,其中INIT为输出初始值,SRTYPE表示同步或异步复位,而DDR_CLK_EDGE有以下两种模式:

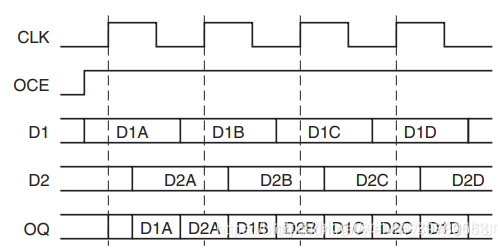

1、OPPOSITE_EDGE模式

2、SAME_EDGE模式