什么是数字IC设计?

数字集成电路设计是一个程序化的过程,包括将规格和特性转换成数字块,然后再进一步转换成逻辑电路。与数字集成电路设计相关的许多限制来自铸造工艺和技术限制。

在数字集成电路设计的更高层次阶段,以及确保设计尽可能高效地满足规格要求的系统和流程的开发阶段,设计技能和独创性是关键。

综合与验证:硬件描述语言和功能验证

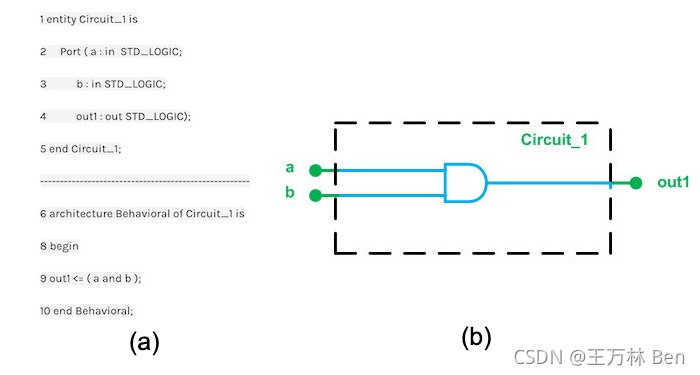

在数字设计的早期阶段开发的具有行为描述的数字块需要转换为硬件描述语言(HDL),如Verilog或VHDL。这个阶段通常被称为注册传输级别(Register Transfer Level, RTL)阶段,它通常包括功能验证,以确保逻辑实现在高层满足规范。

在这一步之后,硬件描述被转换成门级网络列表,在此期间,可以尝试各种实现和优化例程来更好地满足设计目标。这个阶段的重要考虑因素包括功率预算、速度、占地面积和可靠性。

物理IC布局:平面规划和IP核

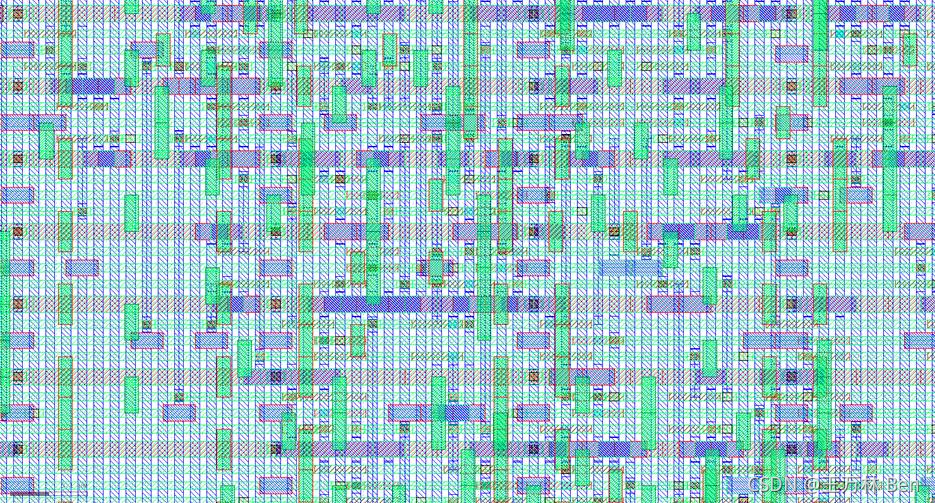

综合验证后,将门级网表转换为物理布局,物理布局是集成电路的层和物理结构的几何表示。采用平面规划方法,确保整个集成电路的块和垫的放置符合设计目标。

由于一些数字块(如内存和寄存器)的结构化和重复性,部分数字IC布局通常使用脚本和自动化软件过程来完成。外部IP核也放置在这个阶段,只有必要的接口部分的IP是由软件显示。在所有的块和门都被放置好之后——如果有必要的话,还会使用手动路由——路由自动化脚本和软件来连接每个元素。

验证与模拟:Tapeout与Testing

然后进行验证和仿真,两者都必须考虑布局和布局的物理特征。如果成功,结果是一个输出文件,如GDSII (GDS2),铸造厂使用内部软件和过程来制造集成电路,磁带输出阶段。在某些情况下,铸造厂发现设计问题,然后需要由设计团队进行纠正/确认。

在tape-out之后,一小批第一次运行或原型ic被生产出来,以便进行测试。这种测试可能导致重新设计或工艺更改,这取决于生产集成电路的性能和经济。

数字集成电路抽象等级

- 行为

- 寄存器传输级别(RTL)

- 功能

- 门

- 晶体管

- 物理布局

数字 IC 设计流程

以下列表概述了数字 IC 设计流程中的步骤,包括子步骤:

- 设计规范

- 规格

- 约束

- testbench开发

- 高级系统设计

- 设计分区

- 入门 Verilog 行为建模

- 模拟/功能验证

- 集成与验证

- 逻辑综合

- 寄存器传输级 (RTL) 转换为网表

- 设计划分为物理块

- 时序裕量和时序约束

- RTL和门级网表验证

- 静态时序分析

- 平面规划

- 分层 IC 块放置

- 电源和时钟规划

- 合成

- 时序约束和优化

- 静态时序分析

- 更新展示位置

- 更新电源和时钟规划

- 块级布局

- 完整的块布局和布线

- IC 级布局

- 所有模块的IC集成

- 单元格放置

- 扫描链/时钟树插入

- 信元路由

- 物理和电气设计规则检查 (DRC)

- 布局与原理图 (LVS)

- 寄生提取

- 布局后时序验证

- GDSII 创建

- 流片

参考资料

https://www.allaboutcircuits.com/technical-articles/what-is-digital-ic-design/

https://www.allaboutcircuits.com/technical-articles/what-is-analog-ic-design/

https://www.allaboutcircuits.com/technical-articles/what-is-rf-integrated-circuit-design/