前言

最近的项目中用到GD32F303Rx系列的单片机作为主控芯片。由于整个产品设计的功能比较复杂,IO几乎都用到了。在最初画原理图布线的时候,用到了一些特殊功能的GPIO。与通用IO相比,相同的软件配置在实际验证过程中,发现存在一定的问题。本文不能说从根本上解决了该问题,只能说从最终效果上实现了所设想的输出逻辑电平。

IO脚:PC13~PC15

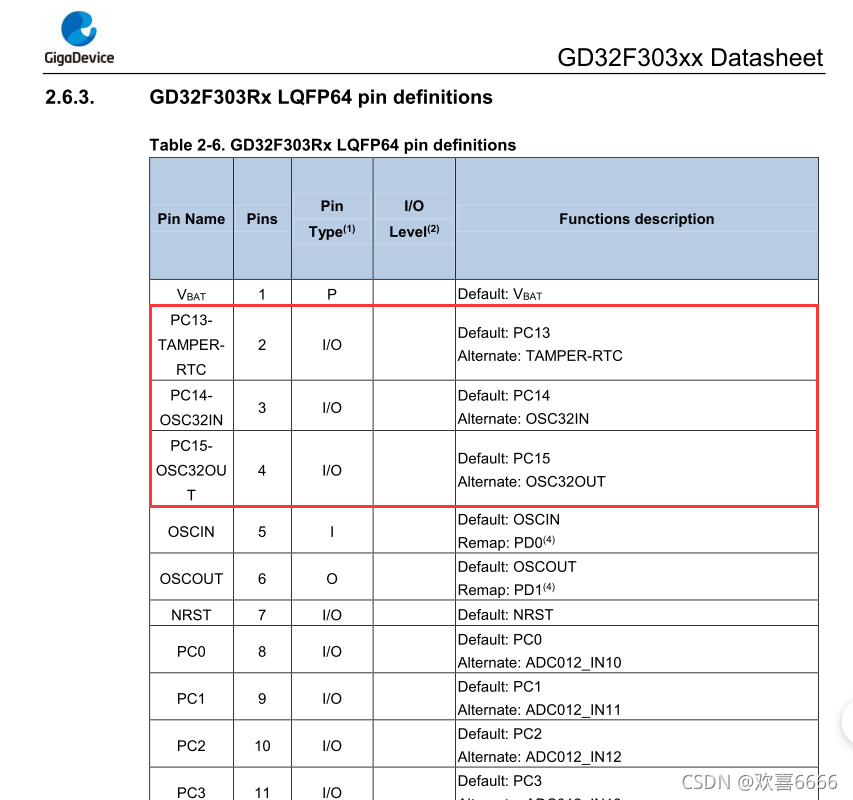

- 先看看PC13~PC15的引脚功能

- 在不使用外部低速时钟和内部RTC时钟的情况下,这三个脚默认都是GPIO。

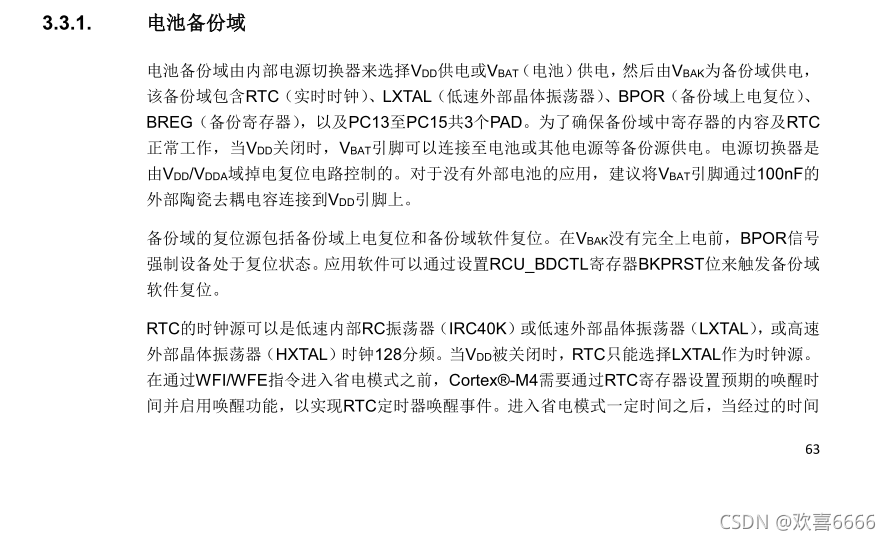

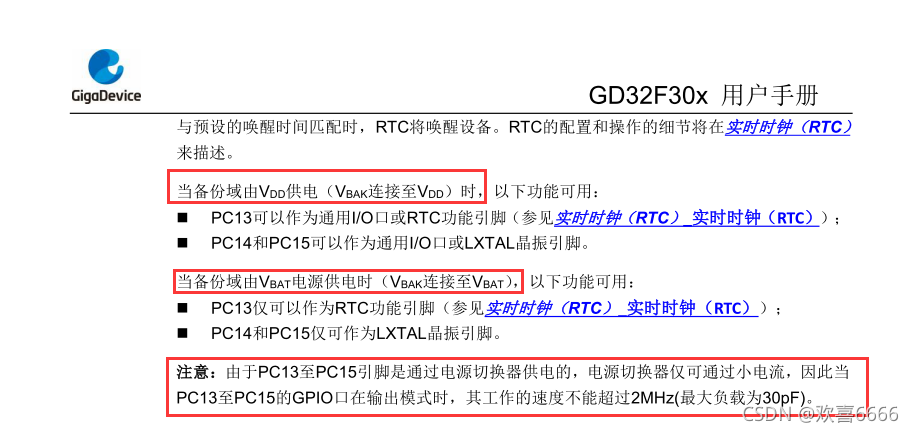

- 再看看手册中的说明

- 从上文总结来看,PC13~P15虽然能作为普通的GPIO,但在其输入输出特性上由于芯片内部设计的原因,与其他通用IO相比差了很多。首先工作速度最大2MHz,其次由于其内部由电源切换器供电,拉电流和灌电流的能力都大大减弱。所以在了解其描述后,我们就明白,即使在代码配置准确无误的情况下,这些IO的驱动能力也远远不及其他通用IO。所以用到时一定注意是否能驱动外围相关电路。

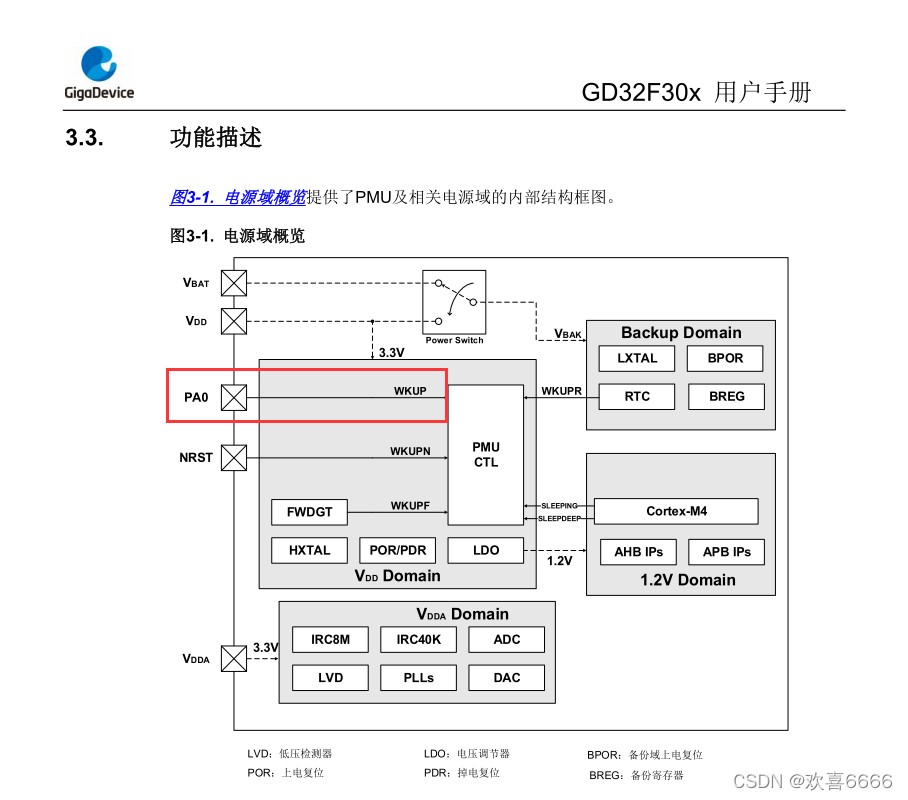

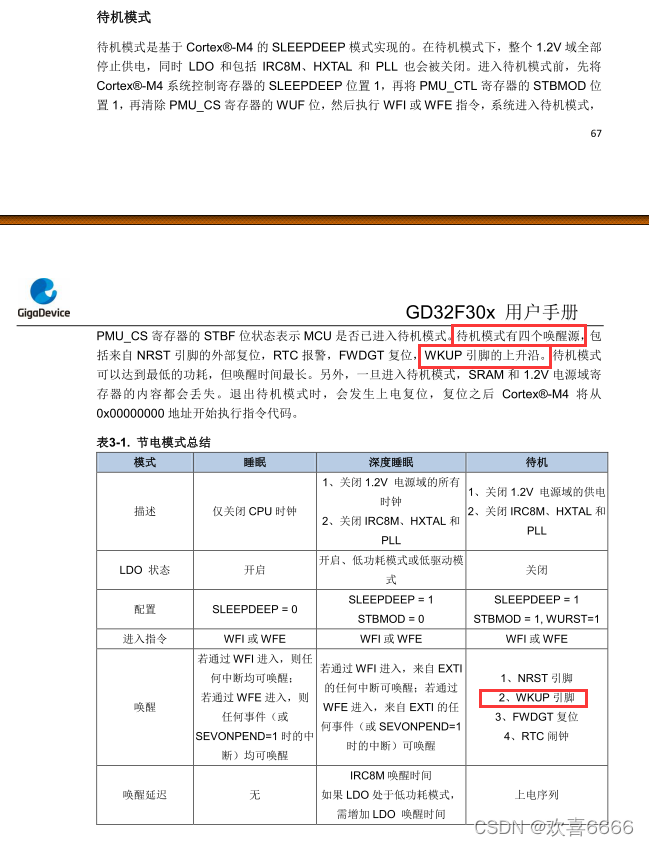

IO脚:PA0

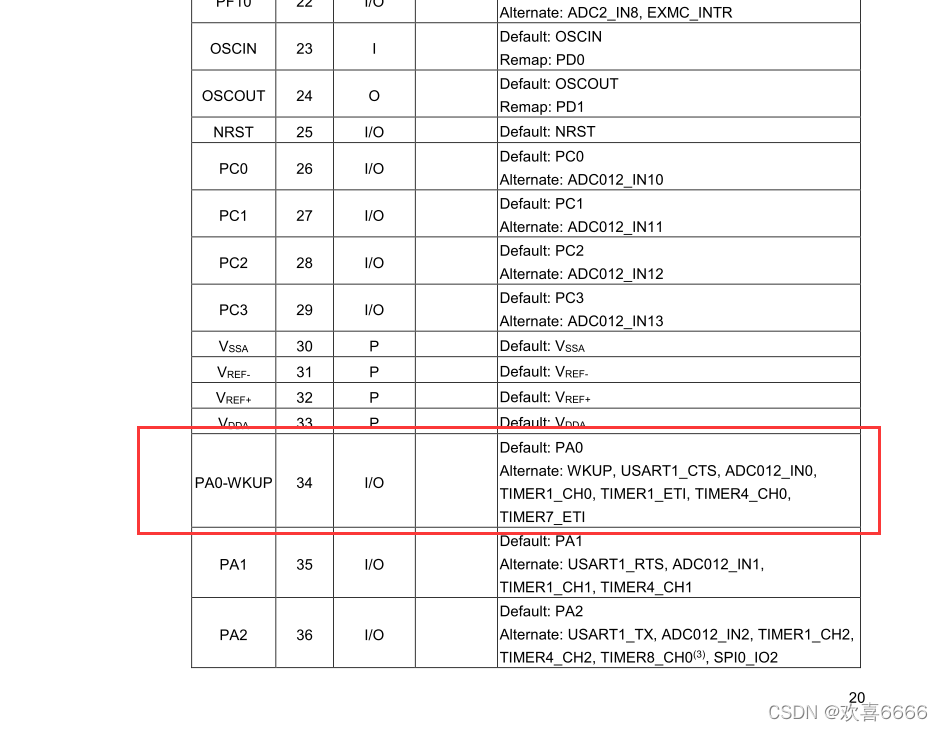

- 在不使用低功耗唤醒和其他映射的情况下,这个脚默认是GPIO。

- 再看看手册中的说明

- 上述仅描述了PA0作为退出休眠唤醒时的作用,其他似乎并没有什么,关键词搜索我也没找到其他关于PA0的特别介绍。

问题

- 这里不再抓波形演示IO的输出的现象,直接说出现的问题。

- 这四个IO我都是作为模拟通信数据口和驱动步进电机输出控制波形口的功能使用的,全部配置为推挽输出。在此情况下,并没有实现其他通用IO电平下的电平转换。在单片机3.3V供电的情况下,PC13~PC15配置输出为0时,输出为低(0V左右),配置为1时,输出还是低(0.6V左右),并不能完全拉到电源(3.3V)。而PA0与之有点相反,配置输出为1时,输出为高(3.3V左右),配置为0时,输出还是高(2.7V左右),并不能完全拉到地(0V)。

- 1.在排除自己的连锡和外围器件后,即使悬空输出,仍不能解决问题。

- 2.通过读相应IO寄存器的数据,也未发现异常。

解决办法(治标)

- 由于某些未知原因,在操作这些IO的时候改变代码配置并不能达成想要的输出控制的时候。这个时候我们可以稍稍修改下外围的器件。

- 我们将上述IO由推挽输出配置成开漏输出。既然只能保持一个电平,那么我们就让其控制一个电平,另一个电平由外部辅助电路(外部上拉)提供好了。

- 先验证配置成开漏输出后在没有外部上拉的情况下,IO是不是只能输出低电平。PC13~15在此情况下,配置输出为0时,输出为低(0V左右),配置为1时,输出还是低(0V左右)。PA0在此情况下,配置输出为0时,输出为低(0V左右),配置为1时,输出还是低(0.3V左右)。

- 均配置上外部上拉后,PC13~15在此情况下,配置输出为0时,输出为低(0V左右),配置为1时,输出是高(2.6V左右)。PA0在此情况下,配置输出为0时,输出为低(0.3V左右),配置为1时,输出是高(3.3V左右)。

- 根据上述的现象我们发现有了外部上拉后有了明显的效果,但跟我们所设想的还是有区别,高、低电平仍然不是理想的状态。

- 这个时候想想我们的数字电路,无论是高电平还是低电平都是有一个阈值范围的。并不是只有0V才算低,3.3V才算高。这个时候我们翻阅芯片手册,发现GD32的规格书中注明了:0.3VDD及以下是低电平,0.7及VDD以上是高电平。而外围的驱动芯片对高低电平的判断也有了范围定义。所以无论是2.6V还是0.3V都满足我这次的高、低电平要求范围。那么上述解决方法能解决面临的问题。

总结与疑问

- 上述问题虽然这次解决了,但不是根治方法。再次我有几个疑问:

- 针对这些特殊IO口,若想作为推挽输出,芯片PCB布局上有哪些需要注意的(供电连接等)。

- 代码配置中,是不是也有需要注意的点,若有的话能否指明出来。