目录

前言

AI时代,内存需求和I/O通信需求激增,传统架构在内存和I/O扩展方面的局限性愈发凸显,严重制约了系统性能的提升。CXL技术应运而生,凭借其高兼容性、低延迟和内存一致性等特性,成为解决这一问题的关键。CXL技术最初由英特尔、AMD等公司联合推出,并得到了微软等公司的支持。它的出现是为了解决CPU和设备、设备和设备之间的内存鸿沟问题,特别是在服务器环境中,内存分割已造成资源浪费、操作不便及性能下降。CXL技术旨在通过提供高带宽、低延迟的通信通道,实现CPU与加速器(如GPU、FPGA等)之间的高效互联,从而提升系统整体性能。那么本文就来详细聊聊相关的内容话题。

CXL的定义与背景

Compute Express Link(CXL)是一种高性能的互连标准,旨在解决现代计算需求中 CPU、内存、加速器(如 GPU、FPGA)和存储之间的数据传输瓶颈。CXL 基于 PCIe 物理层和协议层,提供低延迟、高带宽的通信能力,为高性能计算(HPC)、数据中心和人工智能等领域提供了重要支持。

核心特点

1. 基于 PCIe 的设计

CXL 架构利用 PCIe 的物理层,与现有硬件设备具有高度兼容性。相比 PCIe,CXL 专注于共享内存和一致性机制,为 CPU 和其他设备之间的数据传输提供优化。

2. 低延迟、高带宽

CXL 的协议通过减小数据传输延迟和提高带宽,实现高效的设备互联和资源共享。它支持 CPU 和加速器(如 GPU、FPGA)之间无缝协作,减少了传统互联中出现的通信开销。

3. 内存共享与一致性

CXL 提供多级一致性模型,支持多个设备同时访问共享内存。通过缓存一致性(Cache Coherence)技术,确保各设备间的数据操作保持同步。

CXL体系结构的原理解析

1、CXL协议的层次结构

CXL 协议横跨整个计算堆栈,涉及计算机科学的多个分支。CXL 在一致性、向后兼容性和开放性方面采用了非对称方法,以实现多样化和开放的生态系统。CXL 一致性与特定于主机的一致性协议细节脱钩,主机处理器负责协调缓存一致性,以简化设备一致性的实施。

2、CXL的实现与应用场景

CXL 提供多种复杂程度不同的协议,支持多种用例,设备只能实施协议的一个子集。CXL 利用 PCIe 物理层,设备插入 PCIe 插槽。CXL 的向后兼容演进及其与 PCIe 的互操作性,确保了公司对 CXL 的投资可以保证与上一代 CXL 设备以及任何 PCIe 设备的互操作性。

实践应用

1、CXL在数据中心的应用

CXL 为数据中心提供了高效的数据传输和资源共享能力。通过 CXL,数据中心可以实现更高效的扩展和通信,提升整体性能。

2、CXL在人工智能领域的应用

在人工智能领域,CXL 支持加速器和 CPU 之间的高效协作,加速模型训练和推理过程。CXL 的低延迟和高带宽特性使得大规模并行计算成为可能。

未来发展方向

1、CXL 3.1 的改进

CXL 3.1 的核心亮点在于其革命性的结构改进,使得数据中心能够实现更高效的扩展和通信。通过引入基于端口的路由(PBR)和全局集成内存(GIM),CXL 3.1 不仅提升了数据传输速度,还极大地增强了系统的灵活性和响应能力。

2、CXL技术的持续演进

CXL 技术的持续演进将推动高性能计算和数据中心的发展。CXL 的开放性和互操作性将促进更多设备和平台的集成,为未来的计算架构提供更强大的支持。

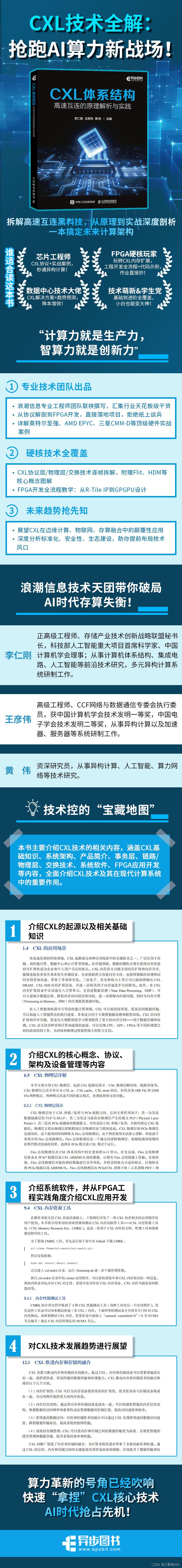

关于《CXL体系结构:高速互连的原理解析与实践》

接下来给大家推荐一本关于 CXL 体系结构的书籍——《CXL 体系结构:高速互连的原理解析与实践》。这是一本深入剖析 CXL 体系结构的原理与实践应用的专业书籍,一经出版便受到了相关领域专家和从业者的一致好评。本书从 CXL 体系结构的基本原理讲起,逐步深入到实际的系统设计与优化技巧,帮助读者全面掌握 CXL 技术在现代计算架构中的应用,为高性能计算和数据中心的建设提供有力支持!另外,关注本文博主,点赞 + 收藏本文,且在本文评论区评论“入手 CXL”,将选取三名幸运读者送出纸质版《CXL 体系结构:高速互连的原理解析与实践》一本,截止时间:2025.04.15。入手《CXL 体系结构:高速互连的原理解析与实践》传送门:https://item.jd.com/14975070.html或者《CXL体系结构:高速互连的原理解析与实践》(李仁刚、王彦伟、黄伟)【简介_书评_在线阅读】 - 当当图书。个人觉得这本书非常不错,是一本不可多得的专业书籍,值得相关领域的从业者和学习者拥有并深入学习。

编辑推荐

适读人群 :1. AI算力基础设施、存算一体芯片、绿色数据中心、Chiplet生态等方向的研究人员、工程师、技术开发者 2. 对CXL技术感兴趣的所有研究人员、工程师、技术开发者,以及对高速互连技术感兴趣的学生和专业人士 3.驱动程序研发工程师、FPGA/芯片研发工程师和异构计算领域的研究人员

CXL——存储方向新热点技术,浪潮信息技术团队出品

全面介绍CXL技术及其在现代计算系统中的重要作用

可满足智算中心、AI服务器、GPU互联、存内计算、云原生基础设施、内存处理、超融合系统等应用场景需求。

内容简介

本书主要介绍CXL技术的相关内容,涵盖CXL基础知识、系统架构、产品简介、事务层、链路/物理层、交换技术、系统软件、FPGA应用开发等内容,全面介绍CXL技术及其在现代计算系统中的重要作用。

本书分4篇:第一篇(第1~4章)介绍CXL的起源以及相关基础知识;第二篇(第5~8章)介绍CXL的核心概念、协议、架构及设备管理等内容;第三篇(第9、10章)介绍系统软件,并从FPGA工程实践角度介绍CXL应用开发;第四篇(第11、12章)对CXL技术发展趋势进行展望。

本书适合对CXL技术感兴趣的研究人员、工程师、技术开发者,以及对高速互连技术感兴趣的学生和专业人士阅读,尤其适合驱动程序研发工程师、FPGA/芯片研发工程师和异构计算领域的研究人员参考。

作者简介

李仁刚,正高级工程师,就职于浪潮电子信息产业股份有限公司。存储产业技术创新战略联盟秘书长,科技部科技创新2030——新一代人工智能重大项目首席科学家 / 项目负责人,中国计算机学会理事。主要从事计算机体系结构、集成电路、人工智能等前沿技术研究,以及多元异构计算系统研制工作。

王彦伟,高级工程师,就职于浪潮电子信息产业股份有限公司,CCF 网络与数据通信专委会执行委员。主要从事异构计算以及加速器、服务器等系统研制工作。曾获中国计算机学会技术发明一等奖,中国电子学会技术发明二等奖。

黄伟,资深研究员,就职于浪潮电子信息产业股份有限公司。主要从事异构计算、人工智能、算力网络等技术研究。获发明专利授权 9 项,发表论文 7 篇。

图书目录

第一篇 CXL概述

第 1章 CXL起源与发展 3

1.1 CXL的产生背景 3

1.1.1 新型应用需求飞速增长 3

1.1.2 多元化计算架构需求旺盛 4

1.1.3 PCIe鞭长莫及 4

1.2 相关互连协议的提出 6

1.3 CXL的提出与发展 7

1.4 CXL的应用场景 8

1.5 小结 9

第 2章 CXL基础知识 10

2.1 PCIe体系结构 10

2.1.1 PCIe架构 10

2.1.2 PCIe的层次结构 13

2.1.3 PCIe配置扩展 15

2.1.4 PCIe设备的初始化 19

2.2 缓存一致性 20

2.2.1 缓存一致性问题的诱因 20

2.2.2 MESI简介 21

2.3 小结 22

第3章 CXL系统架构 23

3.1 CXL互连架构简介 23

3.2 CXL子协议 24

3.2.1 CXL.io 24

3.2.2 CXL.cache 24

3.2.3 CXL.mem 26

3.3 CXL设备 27

3.3.1 Type 1设备 28

3.3.2 Type 2设备 28

3.3.3 Type 3设备 30

3.3.4 多逻辑设备 30

3.3.5 CXL设备扩展和CXL Fabric 30

3.4 CXL核心组件 31

3.4.1 Flex总线 31

3.4.2 Flit 33

3.4.3 DCOH 33

3.4.4 HDM 34

3.4.5 交换机 34

3.5 CXL总线层次结构总览 37

3.6 小结 38

第4章 CXL产品简介 39

4.1 CXL处理器 41

4.1.1 第四代英特尔至强可扩展处理器 41

4.1.2 AMD EPYC 9004处理器 41

4.2 内存 41

4.2.1 三星CMM-D 41

4.2.2 海力士CMM-DDR5 42

4.2.3 澜起科技CXL内存扩展控制器芯片M88MX5891 43

4.3 CXL SSD 43

4.4 CXL交换芯片 44

4.5 CXL FPGA板卡 45

4.5.1 Agilex 7 FPGA 45

4.5.2 Intel Agilex 7 FPGA开发套件 46

4.5.3 浪潮F26A 47

4.6 CXL控制器IP 48

4.7 浪潮G7系列服务器 49

4.8 小结 51

第二篇 CXL体系结构

第5章 CXL事务层 55

5.1 核心概念 55

5.1.1 内存 55

5.1.2 缓存行的归属 57

5.2 CXL事务层协议 58

5.2.1 CXL.io事务层 58

5.2.2 CXL.cache事务层 59

5.2.3 CXL.mem事务层 60

5.3 CXL事务层架构 60

5.3.1 CXL事务层概念映射关系 61

5.3.2 CXL事务层硬件逻辑架构 62

5.4 CXL.cache事务层详解 63

5.4.1 CXL.cache Read请求 63

5.4.2 CXL.cache Read0请求 64

5.4.3 CXL.cache Write请求 64

5.4.4 CXL.cache Read0-Write请求 65

5.4.5 CXL.cache H2D请求 65

5.5 CXL.mem事务层详解 66

5.5.1 CXL.mem M2S请求 66

5.5.2 反向无效机制 67

5.6 CXL Type 1/Type 2主机请求HDM流程 67

5.6.1 主机缓存读设备内存 68

5.6.2 主机独占读设备内存 69

5.6.3 主机无缓存读设备内存 69

5.6.4 主机独占设备内存(无数据) 70

5.6.5 主机刷新设备缓存 71

5.6.6 主机弱有序写设备 71

5.6.7 主机无效缓存写设备 72

5.6.8 主机缓存写设备 73

5.7 CXL Type 1/Type 2设备请求HDM流程 73

5.7.1 设备读HDM-D 73

5.7.2 设备读HDM-DB 74

5.7.3 设备写HDM-D(Host Bias) 75

5.7.4 设备写HDM-DB 77

5.7.5 设备写HDM(仅内部实现) 78

5.8 CXL Type 1/Type 2设备请求主机内存流程 79

5.8.1 设备读主机内存 79

5.8.2 设备写主机内存 79

5.9 CXL Type 3主机请求HDM流程 80

5.9.1 主机读HDM-H 80

5.9.2 主机写HDM-H 81

5.10 小结 82

第6章 CXL链路层/物理层 83

6.1 核心概念 84

6.1.1 Flit 84

6.1.2 流量控制 84

6.1.3 错误检查 85

6.2 CXL链路层/物理层架构 85

6.3 CXL链路层详解 86

6.3.1 CXL链路层简介 86

6.3.2 CXL.io链路层 86

6.3.3 CXL.cache/mem链路层 88

6.4 CXL仲裁/复用详解 95

6.5 CXL物理层详解 96

6.5.1 CXL物理层简介 96

6.5.2 有序集块和数据块 98

6.5.3 CXL物理层帧结构 99

6.5.4 链路训练 108

6.6 小结 108

第7章 CXL交换技术 110

7.1 CXL交换机分类 110

7.1.1 单VCS交换机 110

7.1.2 多VCS交换机 111

7.2 交换机的配置和组成 114

7.2.1 CXL交换机的初始化 114

7.2.2 CXL交换机端口的绑定和解绑 118

7.2.3 MLD端口的PPB和vPPB行为 123

7.3 CXL协议的解码和转发 123

7.3.1 CXL.io 123

7.3.2 CXL.cache 124

7.3.3 CXL.mem 124

7.4 Fabric管理器API 125

7.4.1 CXL Fabric管理 125

7.4.2 Fabric管理模型 125

7.4.3 CXL交换机管理 126

7.4.4 MLD组件管理 127

7.4.5 系统操作的管理要求 128

7.4.6 Fabric管理API 132

7.5 CXL Fabric架构 137

7.5.1 CXL Fabric架构应用示例 138

7.5.2 全局架构附加内存 141

7.5.3 HBR和PBR交换机之间的互操作性 150

7.5.4 跨越Fabric的虚拟层次 154

7.6 小结 155

第8章 CXL设备的复位、管理和初始化 156

8.1 CXL系统复位概述 156

8.1.1 CXL设备复位类型 156

8.1.2 对CXL与PCIe复位行为差异 157

8.2 CXL系统复位进入流程 158

8.3 CXL设备睡眠状态进入流程 159

8.4 功能级复位 160

8.5 缓存管理 161

8.6 CXL复位 161

8.6.1 对易失性HDM的影响 163

8.6.2 软件行为 163

8.6.3 CXL复位和请求重试 164

8.7 全局持久性刷新 164

8.7.1 主机和交换机职责 165

8.7.2 设备职责 165

8.7.3 能量预算 167

8.8 热插拔 168

8.9 软件枚举 170

8.10 小结 170

第三篇 CXL工程实践

第9章 CXL相关系统软件 173

9.1 BIOS 174

9.2 ACPI 176

9.2.1 ACPI简介 176

9.2.2 ACPI表访问工具IASL 178

9.3 Linux与CXL驱动程序 180

9.3.1 cxl/acpi 181

9.3.2 cxl/pci 183

9.3.3 cxl/mem 186

9.3.4 cxl/port 188

9.3.5 cxl/core 188

9.4 CXL内存资源工具 192

9.4.1 内存性能测试工具 192

9.4.2 设备管理工具mxcli 198

9.5 小结 199

第 10章 基于FPGA的CXL应用开发 200

10.1 R-Tile CXL IP 200

10.2 CXL BFM 201

10.3 CXL内存扩展 202

10.3.1 FPGA工程设计 202

10.3.2 功能仿真 203

10.3.3 性能测试 205

10.4 CXL GPGPU 209

10.4.1 Vortex GPGPU 209

10.4.2 FPGA工程设计 210

10.4.3 RTL功能仿真 211

10.5 小结 212

第四篇 CXL发展趋势和展望

第 11章 CXL的发展趋势 215

11.1 技术创新和性能提升 215

11.2 标准化和生态建设 216

11.3 安全性和可靠性 217

11.4 小结 218

第 12章 CXL的创新展望 219

12.1 CXL推进内存和存储的融合 219

12.2 CXL拓展边缘计算和物联网 220

12.3 CXL结合领域专用架构 220

12.4 小结 221

《CXL体系结构:高速互连的原理解析与实践》全书速览

结束语

通过上文的详细介绍,想必大家都对CXL 体系结构有了更深的了解,它作为一种高性能的互连标准,为现代计算需求提供了重要的解决方案。通过低延迟、高带宽的通信能力和内存共享与一致性机制,CXL 在数据中心和人工智能领域展现了巨大的应用潜力。随着技术的不断演进,CXL 将继续推动高性能计算的发展,为未来的计算架构提供更强大的支持。