目录

一、ILA介绍

Vivado中的ILA(Integrated Logic Analyzer)即集成逻辑分析仪,是一种在线调试工具。ILA允许用户在FPGA上执行系统内的调试,通过实时抓取FPGA内部数字信号的波形,帮助我们分析逻辑错误的原因,从而更有效地进行debug。类似于Quartus中的SignalTap II,也类似于片上的逻辑分析仪。

相较于编写testbench仿真文件仿真debug的方式,使用ILA调试的方法不写tb仿真文件从而节省时间,可直接上板调试并查看波形。

二、ILA使用步骤

ILA常以IP核的方式调用,可以在IP Catalog中搜索ILA,找到该IP核后进行配置。 配置选项包括:样本数据深度、探针数量、探针位宽等等。配置完成后,在顶层模块RTL代码中例化ILA IP核,接着正常烧录程序上板调试。

(1)设计部分

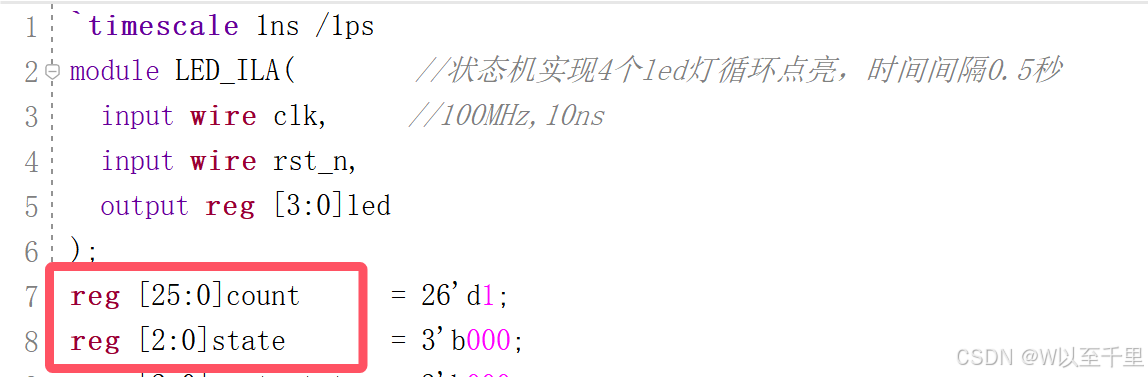

假设已有一个编译成功的工程需要debug调试,我这里直接给一个案例。

工程实现的功能为:通过状态机来实现4个led灯循环点亮,时间间隔0.5秒。

`timescale 1ns /1ps

module LED_ILA( //状态机实现4个led灯循环点亮,时间间隔0.5秒

input wire clk, //100MHz,10ns

input wire rst_n,

output reg [3:0]led

);

reg [25:0]count = 26'd1;

reg [2:0]state = 3'b000;

reg [2:0]next_state = 3'b000;

parameter count_max = 26'd5000_0000;

parameter IDLE = 3'b000;

parameter s1 = 3'b001;

parameter s2 = 3'b010;

parameter s3 = 3'b011;

parameter s4 = 3'b100;

always@(posedge clk or negedge rst_n)begin//计数器

if(!rst_n)

count <= 26'd1;

else if(count == count_max)

count <= 26'd1;

else

count <= count + 26'd1;

end

always@(posedge clk or negedge rst_n)begin//state状态转换

if(!rst_n)

state <= 3'b000;

else if(count == count_max)

state <= next_state;

end

always@(*)begin//next_state状态转换

if(!rst_n)

next_state <= 3'b000;

else begin

case(state)

IDLE: next_state <= s1;

s1: next_state <= s2;

s2: next_state <= s3;

s3: next_state <= s4;

s4: next_state <= s1;

default: next_state <= IDLE;

endcase

end

end

always@(*)begin//led输出信号

if(!rst_n)

led <= 4'b0000;

else begin

case(state)

IDLE: led <= 4'b0000;

s1: led <= 4'b0001;

s2: led <= 4'b0010;

s3: led <= 4'b0100;

s4: led <= 4'b1000;

default: led <= 4'b0000;

endcase

end

end

endmodule接着TOP.v顶层模块文件,把上面这个模块例化进去即可。不过之后还要例化IP核,所以代码在后半部分写完后再给出。

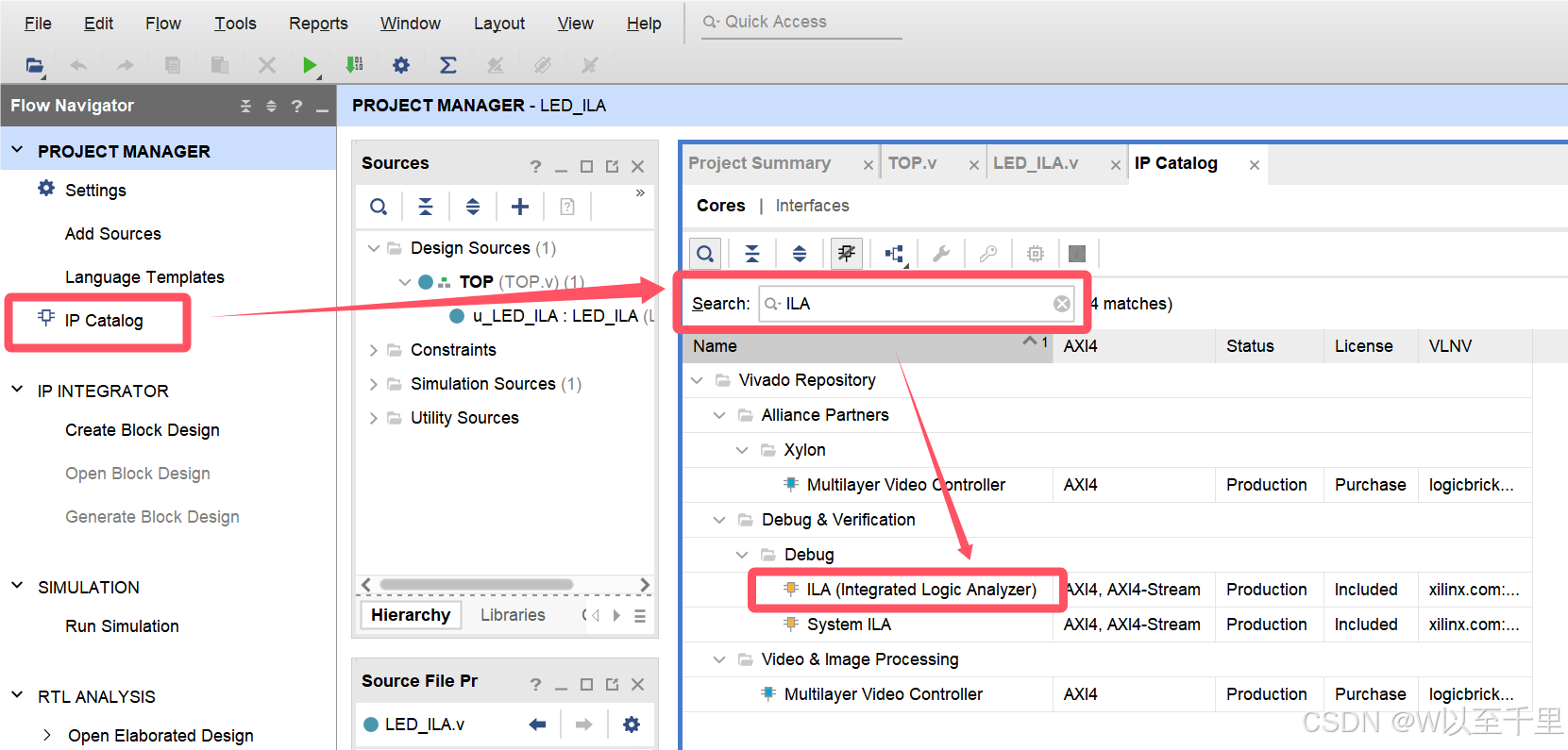

(2)调用ILA IP核

1.按照如下步骤搜索ILA调用IP核,双击" ILA(Integrated Logic Analyzer)"

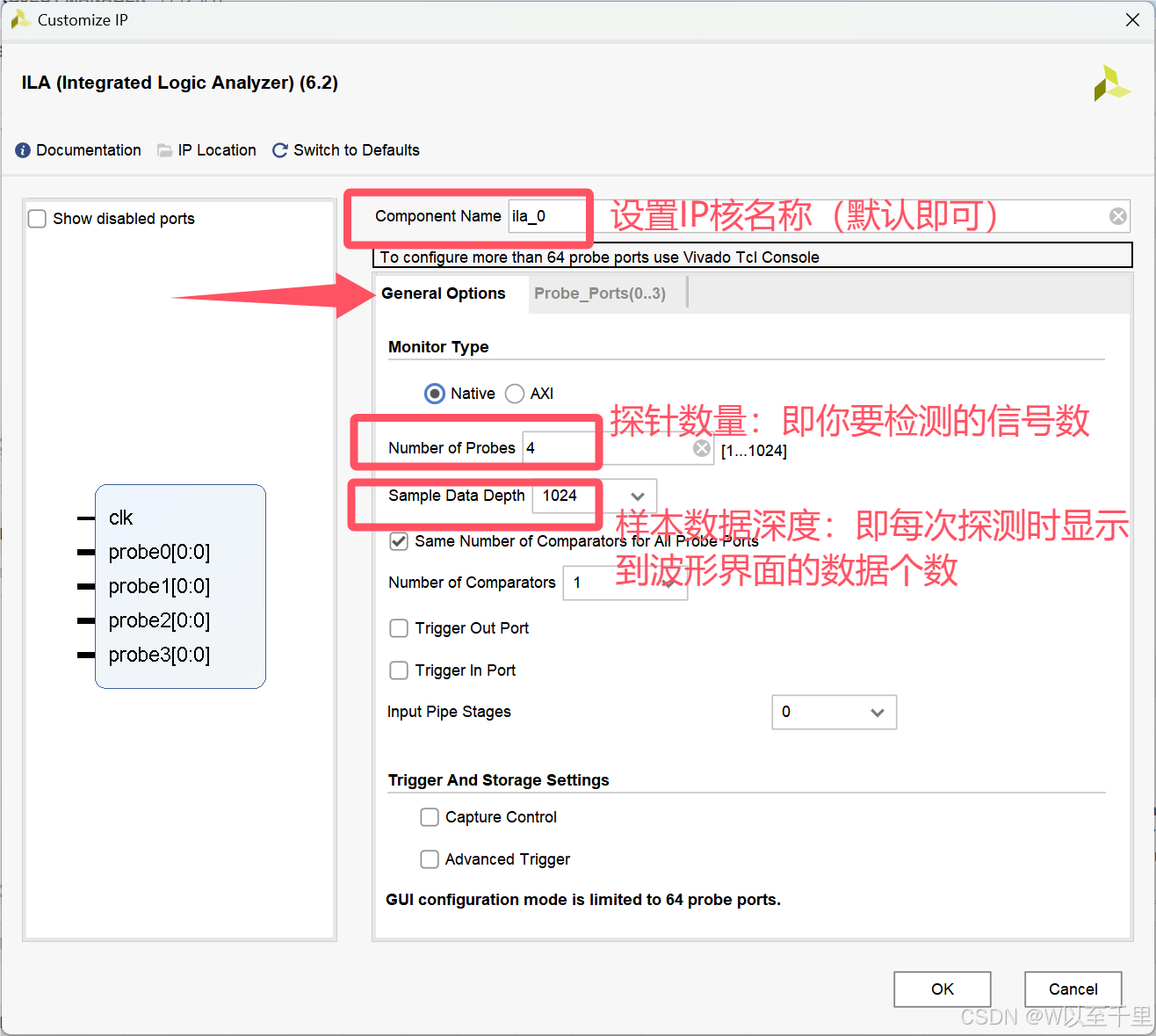

2.进入ILA配置界面,完成基本设置:设置名称、探针数、样本数据深度。其他参数一般用不到保持默认。

(我要看波形的信号有:rst_n、led、count、state所以有4个探针,样本数据深度够用默认1024,即每个有效clk采样一次,采样1024个clk时的数据)

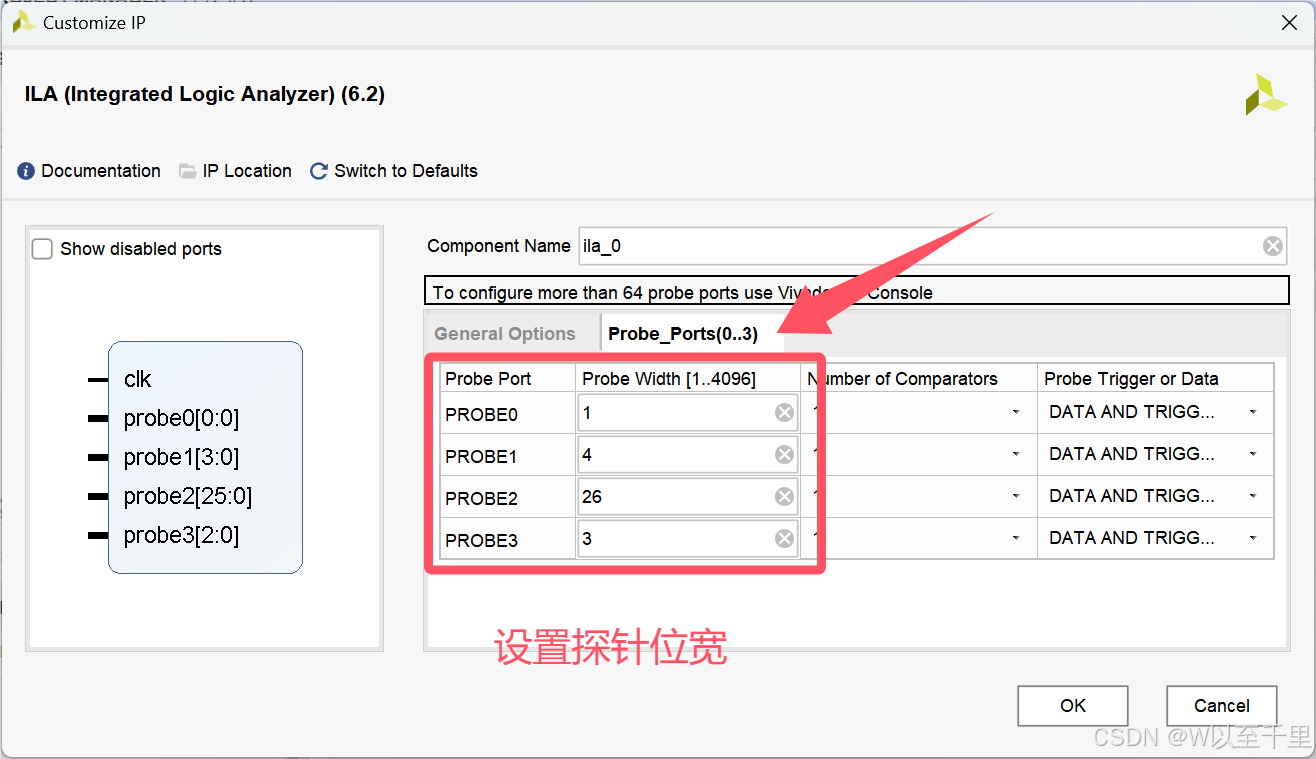

3.接着再当前界面继续设置探针宽度:

(根据rst_n、led、count、state4个信号宽度,依次设置好位宽即可)

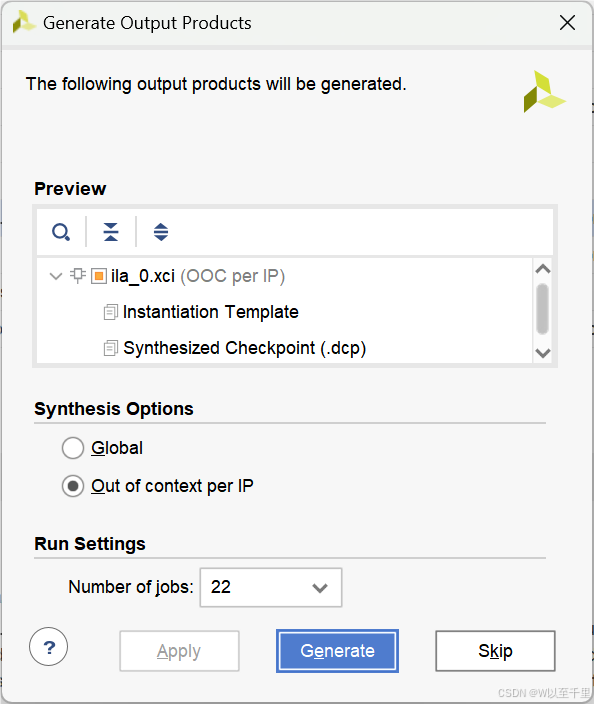

4.再点击OK之后,会弹出该界面,选项保存默认点击“generate”生成IP核,

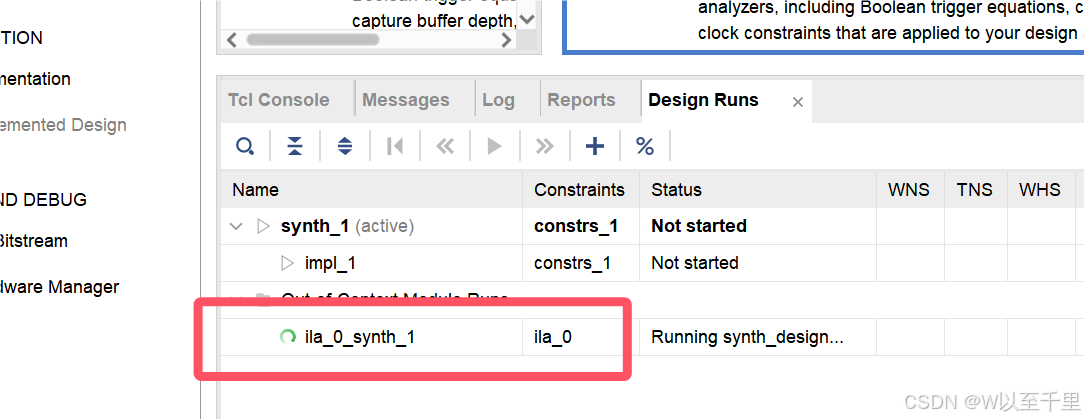

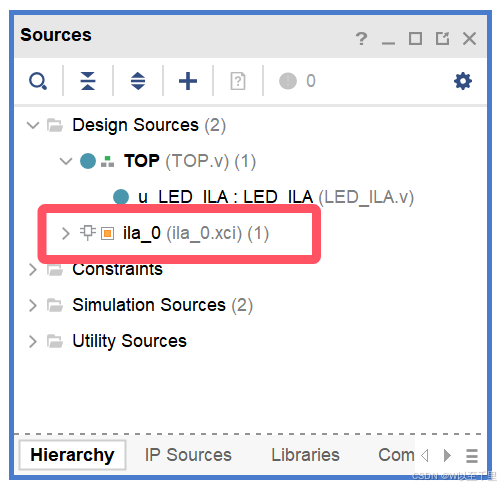

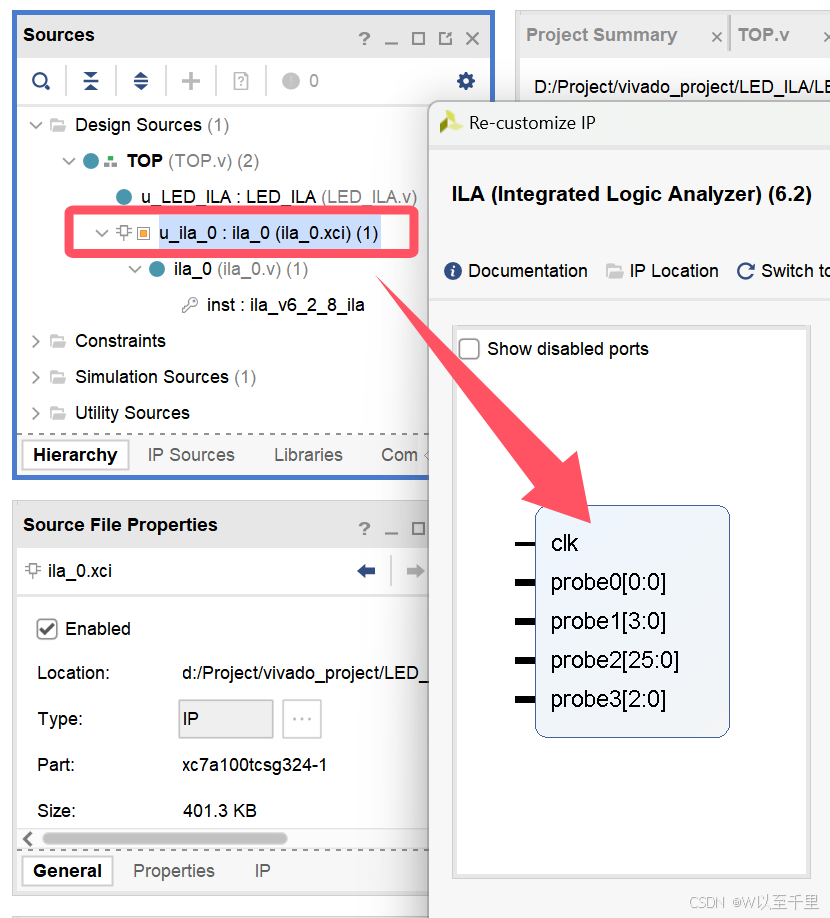

5.这个时候要等一段时间等ip核生成完毕(转圈即正在生成),完毕之后可以看到文件多了一个IP核即ila_o模块。

(3)例化ILA IP核

接着在TOP.v顶层模块文件内例化ILA IP核。并完成连接端口信号:

`timescale 1ns / 1ps

module TOP(

input wire clk,

input wire rst_n,

output wire [3:0]led

);

LED_ILA u_LED_ILA( //例化设计的模块

.clk (clk),

.rst_n (rst_n),

.led (led)

);

ila_0 u_ila_0( //例化ILA IP核

.clk (clk),

.probe0 (rst_n),

.probe1 (led),

.probe2 (u_LED_ILA.count),

.probe3 (u_LED_ILA.state)

);

endmodule

途中会发现count和state是设计模块内定义的寄存器,无法直接连接,此时只需要以“u_LED_ILA.count”的方式连接,因为ILA可以读取模块寄存器内容。

此外不同探针位宽可能不同,注意匹配待检测信号位宽,可以双击IP核查看探针位宽情况

(4)编译综合

接着按照常规流程走:编译、综合、配置管脚、生成比特流文件、烧录开发板。准备进行ILA在线调试。

三、ILA在线调试

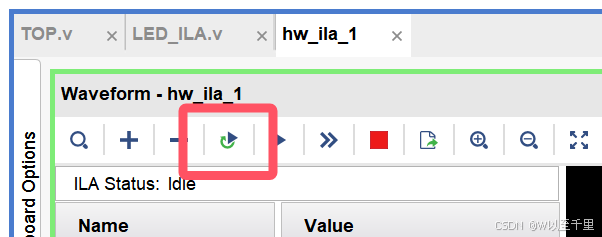

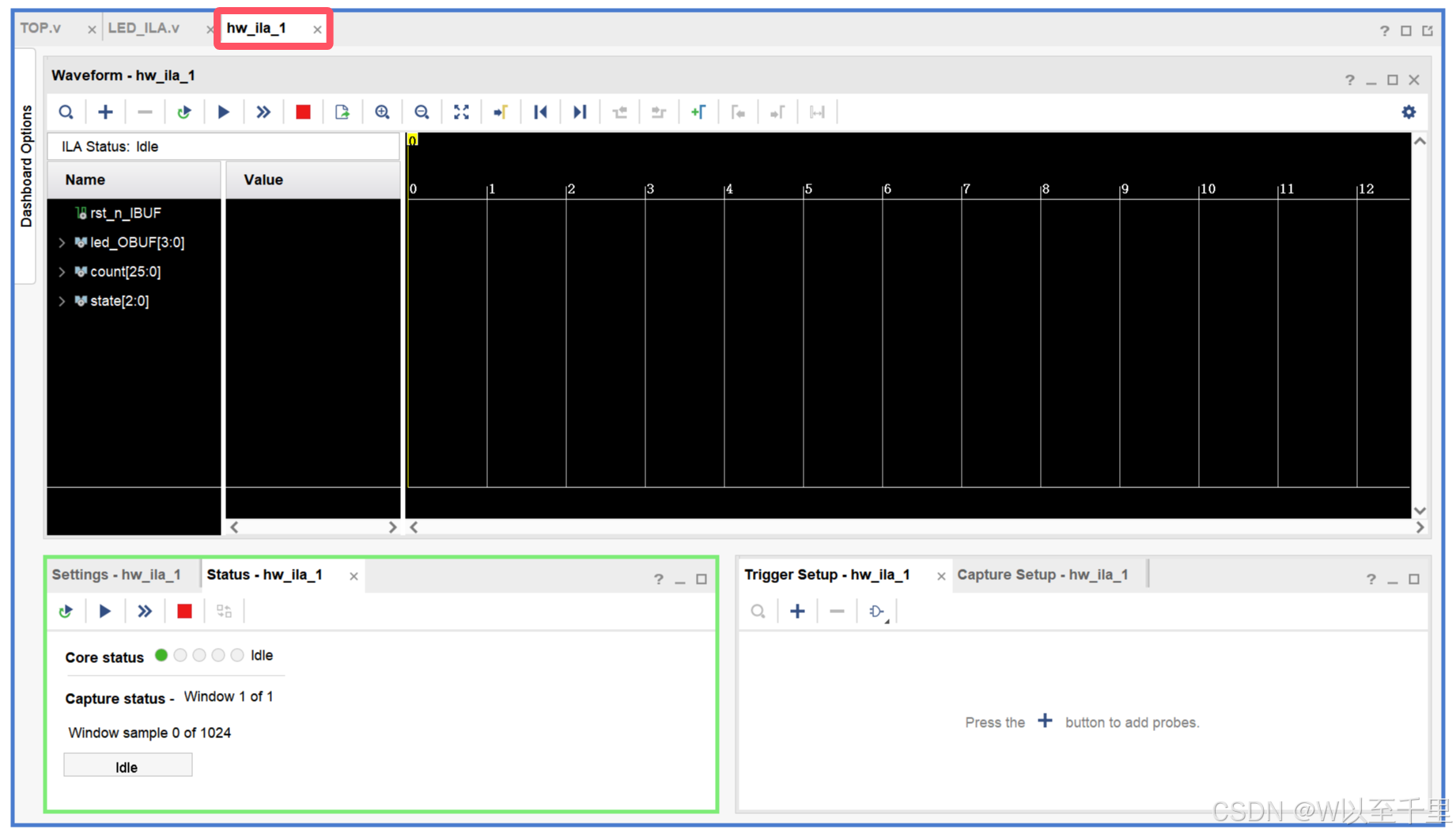

程序烧录到开发板后,Vivado界面会自动弹出ILA的波形窗口如图所示:不过此时这个窗口是空的,是因为还没有触发采样。

因为ILA是数据采样,不可能一直不停采,只能采有限个数据,即有信号触发或手动时开始对探测的信号进行数据采样。下面将介绍如何使用ILA在线调试:

(1)手动运行

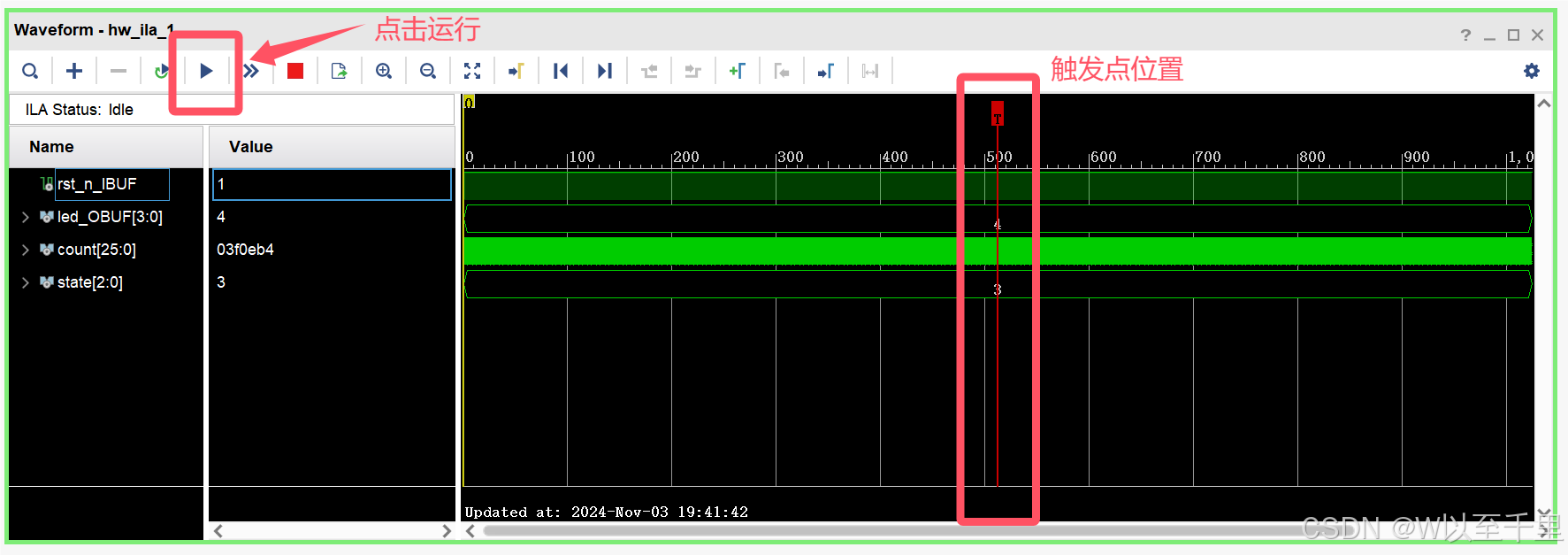

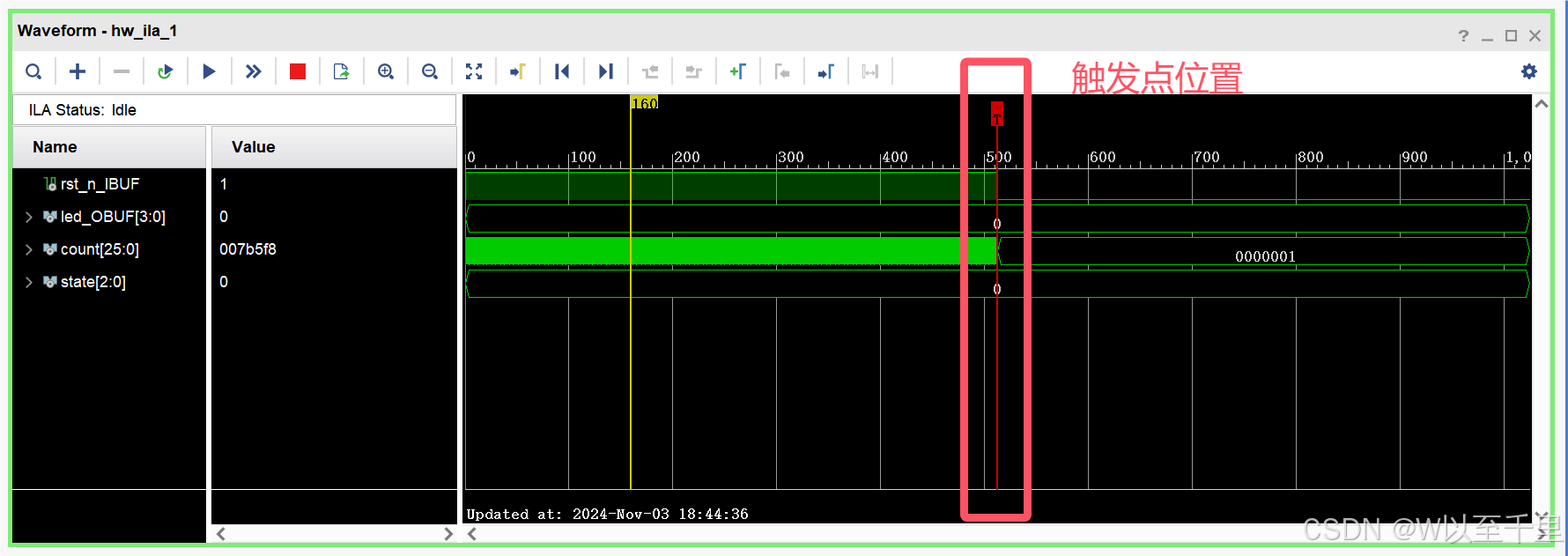

如图所示:点击运行按钮波形会立刻更新,此时红色光标的位置就是你点击运行按钮时的时刻(默认中点),它会在触发点周围进行1024次采样。

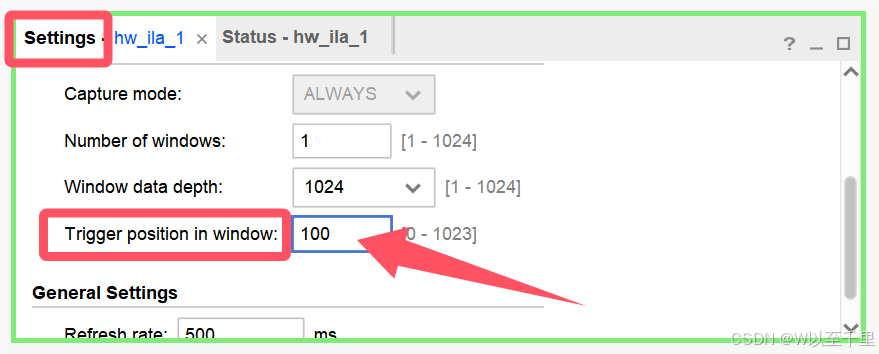

当然你也可以在左下角设置触发点的位置:比如我设置触发点为第100个后,再运行一次,在波形里可以看到触发点位置改变了。(此外还可以设置波形显示的数据个数等等)

(2)运行触发条件

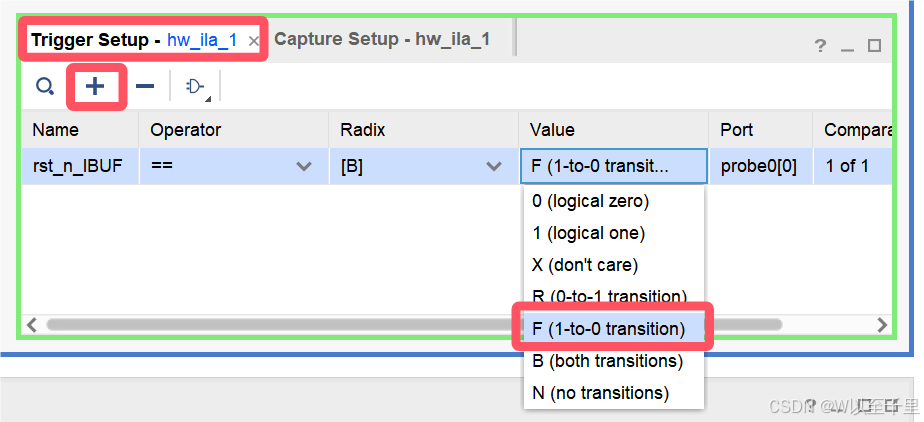

如果我想看特定时刻附近的信号变化情况,手动触发就不适用了,我需要将该特定时刻作为触发点位置,因此需要添加触发条件实现自动触发:

假如我想查看复位时刻其他信号的情况,就需要将复位时刻设置为触发条件,右下角位置添加触发信号并设置条件,我选的是rst_n,同时条件为该信号“1到0转变”时触发。

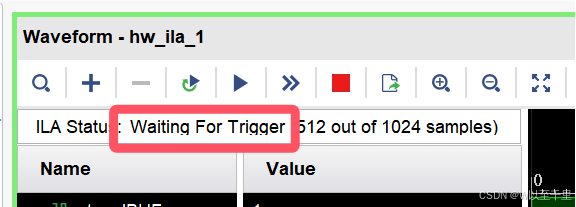

设置完成后再运行一次,会发现界面提示“等待触发”:

这个时候只要你按下开发板的复位按钮(让rst_n产生一个1到0的转换的触发条件),波形界面就会刷新数据,如图所示:

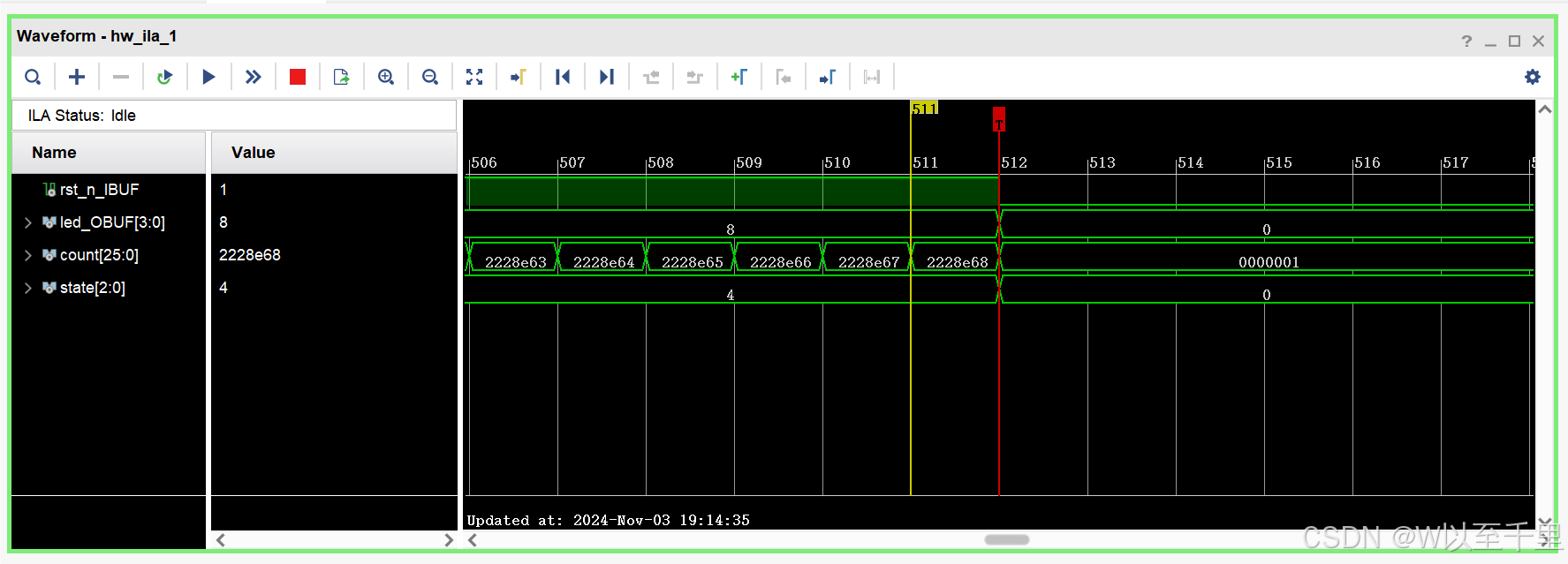

将黄色光标设置移动到触发点附近的位置将波形放大,就可以清楚看到其他信号变化情况了,可以看出复位时所有信号都成功复位:

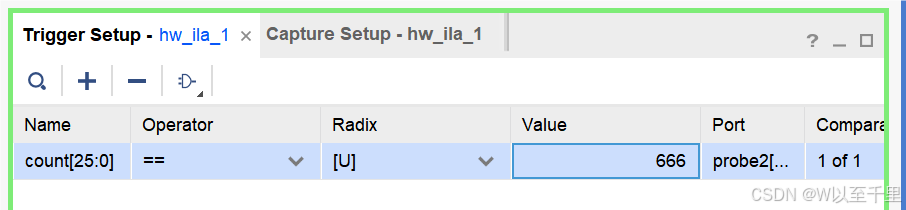

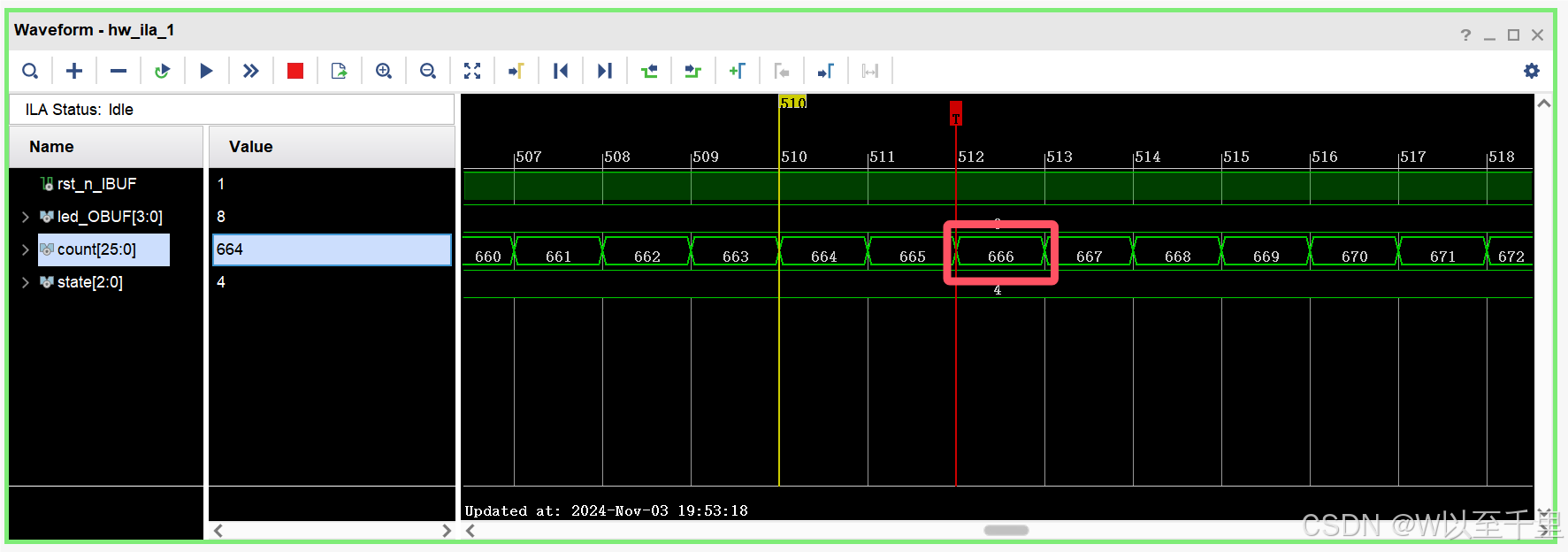

此外触发条件设置多种多样可以根据你的需求进行设置,这样debug起来更加方便快捷,比如要设置某信号到特定值时触发,我可以设置count计数到666的时候触发,运行效果如图所示:

(3)连续触发

这个按钮就是连续触发,当选中这个按钮后不需要手动运行,只要满足触发条件他就会自动运,比如当你设置count计数到666时触发,并选中“连续触发”,count计数每次到666时,波形界面就会刷新一次波形。