关键词:

TriCore TC3XX;TC3XX用户手册;TC3XX ASCLIN;TC397用户手册;

简介:

本篇为英飞凌TC3XX用户手册第36章翻译 - Asynchronous/Synchronous Interface (ASCLIN)

手册适用于TC3XX(包括TC397)芯片

官方架构手册下载链接:

目录

36.3.7.1.1.Break, Wake, Stuck处理

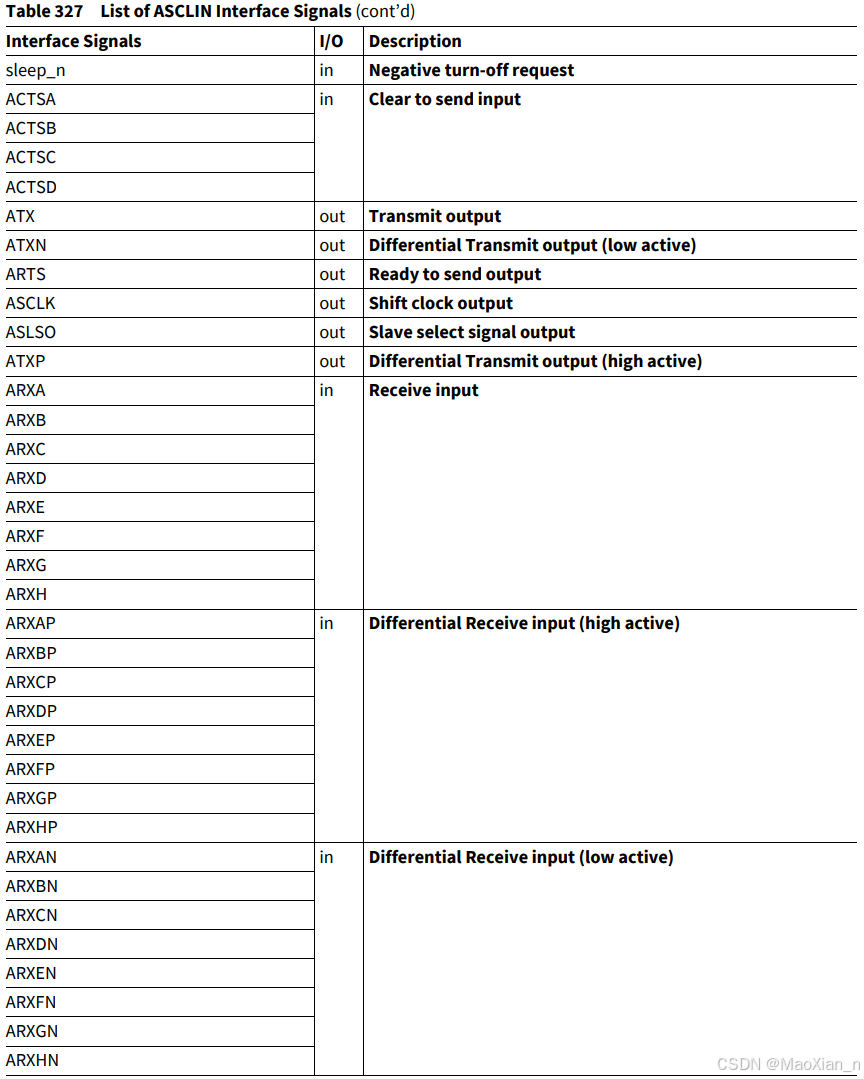

36.同步/异步接口 - ASCLIN

ASCLIN模块支持外设异步串口通信(点对点、LIN协议)和同步SPI通信

LIN - Local Interconnect Network

SPI - Serial Peripheral Interface

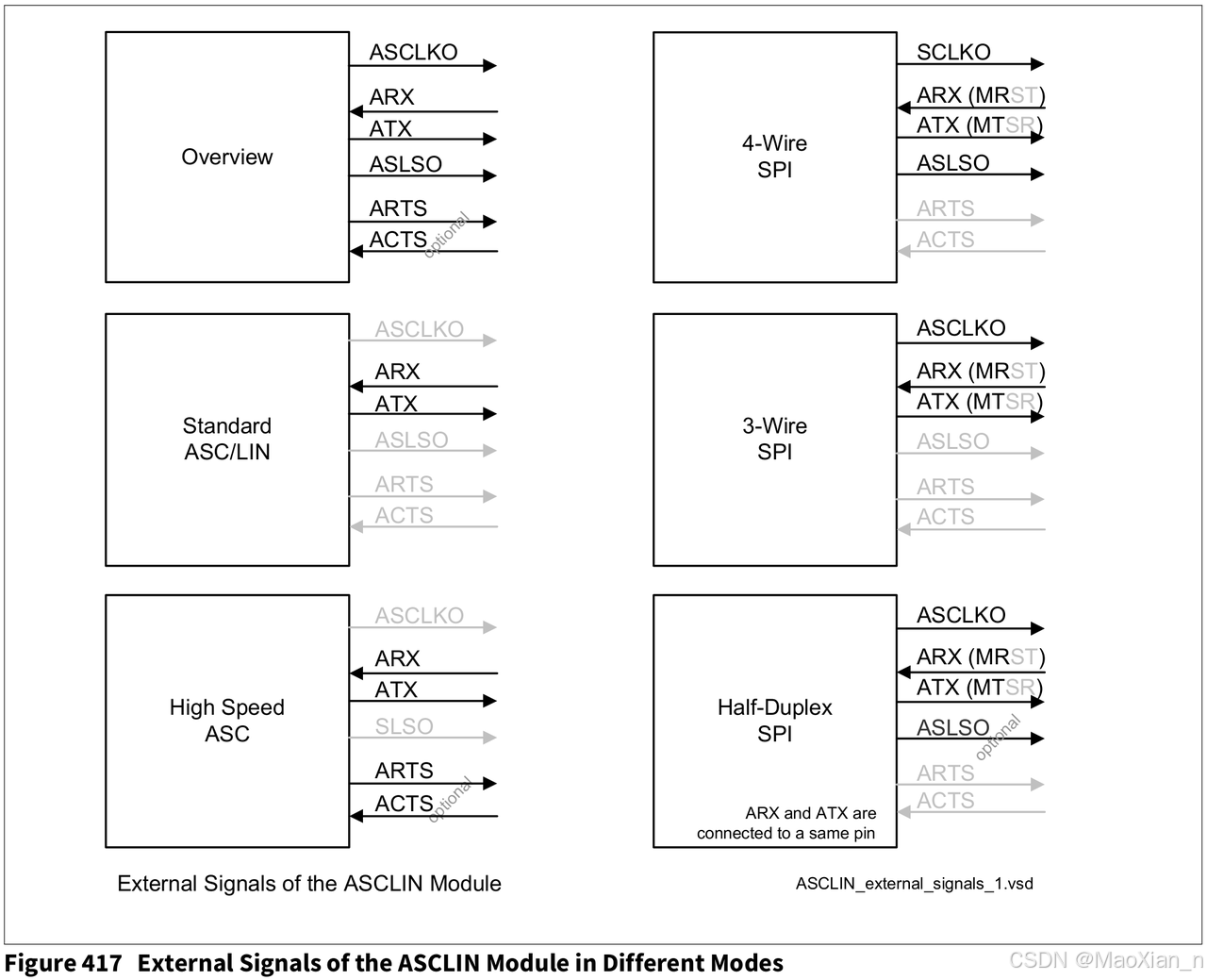

ASCLIN模块的结构如下图所示(RX、TX、RTS、CTS、SCLKO、SLSO信号加上了前缀A,避免和其他模块中的定义产生冲突):

36.1.功能列表

通用

-

16-bytes TxFIFO -

16-bytes RxFIFO -

Pack/Unpack for Rx/Tx FIFO -

中断生成

-

FIFO发送触发电平变化 -

FIFO接收触发电平变化 -

帧错误、奇偶校验错误、

OverRun错误 -

各种模块的内部

Events(ASC/SPI帧结束、LIN Events)

-

-

中断可以触发

CPU或者DMA -

可配置

4~16倍过采样 -

可配置采样点位置

-

输入比特流可配置数字毛刺滤波

Glitch Filter或中值滤波Median Filter -

ASC/LIN模式使用LSB First,SPI模式可配置LSB First或MSB First -

内部回环模式

Loop-Back Mode

标准ASC

-

异步全双工模式

-

7-bit、8-bit、9-bit(最大16-bit)宽度的数据帧,LSB First模式 -

奇偶校验位生成/检查

-

1~2位停止位 -

最大波特率

fA/16(6.25 MBaud @ 100 MHz fA module clock) -

最小波特率

fA/268435456(0.37 Baud @ 100 MHz fA module clock)

-

-

可配置

RTS/CTS握手

扩展ASC

-

可配置

4~16倍过采样-

最多比标准

ASC高4倍的波特率(fA/4) -

PAD类型、输入信号质量、时钟抖动等系统因素会导致可用的超采样率受限制,例如fA/8 = 200MHz/8 = 25MBaud

-

-

可配置采样点位置

LIN

-

支持的协议版本/规范

-

LIN Version1.3、2.0、2.1、2.2 -

J2602

-

-

Break检测 -

Break注入 -

同步域生成

-

基于同步域测量的自动波特率检测

-

可配置冲突检测(仅

LIN 2.1版本支持) -

LIN WatchDogs-

头部超时

-

帧超时、应答超时

-

-

固定性故障(Stuck-at Fault)监测

-

总线

IDLE时间监测 -

唤醒

-

Master模式最小CPU Load-

单个中断指示帧结束

-

-

Slave模式最小CPU Load-

单个中断指示头部接收结束

-

单个中断指示应答结束、帧结束

-

SPI

-

Master模式(不支持Slave模式)-

3/4条读写线路(有/无Slave选择输出信号)

-

-

最大

16-bit数据宽度 -

全双工和半双工

-

最小波特率

fA/268435456 MBaud(0.37 Baud@100 MHz fA module clock) -

最大波特率

fA/4 MBaud(25 MBaud@100 MHz fA module clock)

-

-

可配置前后沿延迟时间

36.2.概览

ASCLIN模块必要的子模块

注意:

-

只有

LIN 2.1版本才会强制使用冲突检测 -

LIN模式下,ARX和ATX信号必须都连接到LIN总线上,ASCLIN模块才能正常工作

36.3.功能描述

36.3.1.外部信号

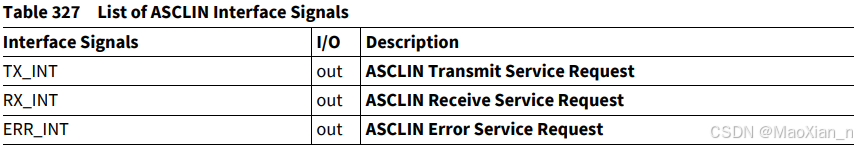

ASCLIN模块提供以下外部信号:

-

串行时钟输出

ASCLK -

接收数据输入

ARX(SPI模式输入Master Receive - MR) -

发送数据输出

ATX(SPI模式输出Master Transmit - MT) -

Slave选择信号输出ASLSO -

请求发送握手输出

ARTS -

清除发送握手输出

ACTS

36.3.2.用户接口

用户接口包含一个TxFIFO和一个RxFIFO,有以下功能:

-

获取数据包,并将其打包为适合

FPI总线宽度的串行帧 -

缓冲

FPI总线上的数据 -

管理握手(

CTS/RTS信号)

36.3.2.1.TxFIFO概览

TxFIFO可以将16-bit的数据打包为两个8-bit帧或一个16-bit帧,也可以将32-bit的数据打包为四个8-bit帧或者两个16-bit帧

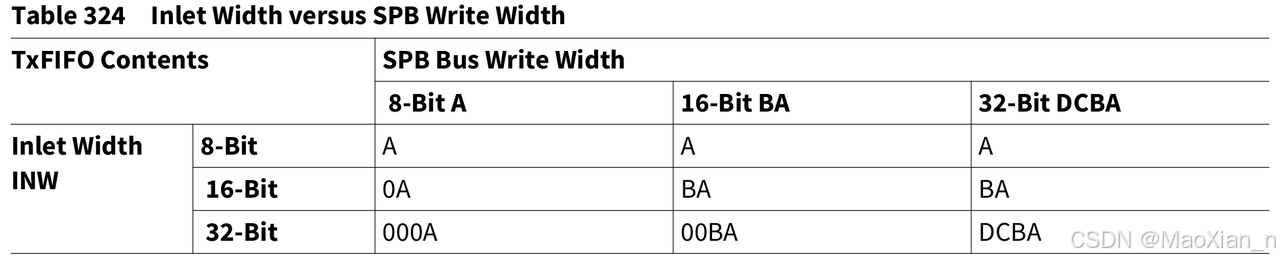

每次向TxFIFO写入数据的字节数,由寄存器位TXFIFOCON.INW定义,其与SPB写入宽度无关,但两者应该相等

如果SPB写入宽度小于INW,缺失的位会补0,如果大于INW则多余的位会被舍弃

在移位寄存器侧,按DATCON.DATLEN的配置,按位传输TxFIFO中的若干字节

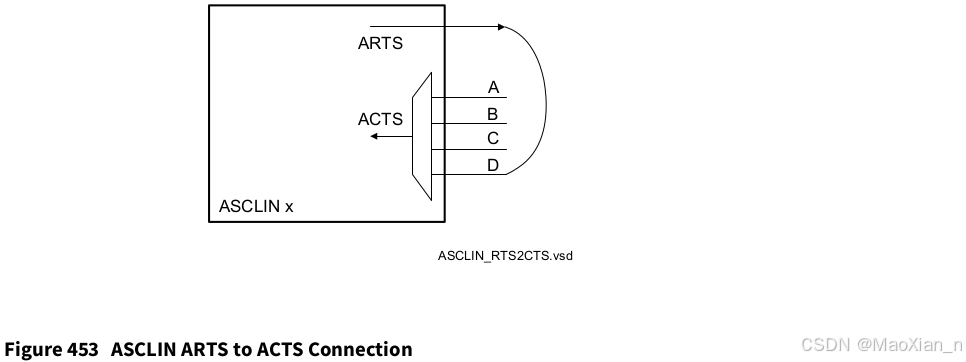

下图展示了INW(Inlet Width)和SPB写入宽度的关系(将要写入TxFIFO的字节为A、B、C、D、0):

36.3.2.2.使用TxFIFO

注意:软件可以根据实际需要配置TxFIFO的宽度

36.3.2.2.1.标准ASC模式

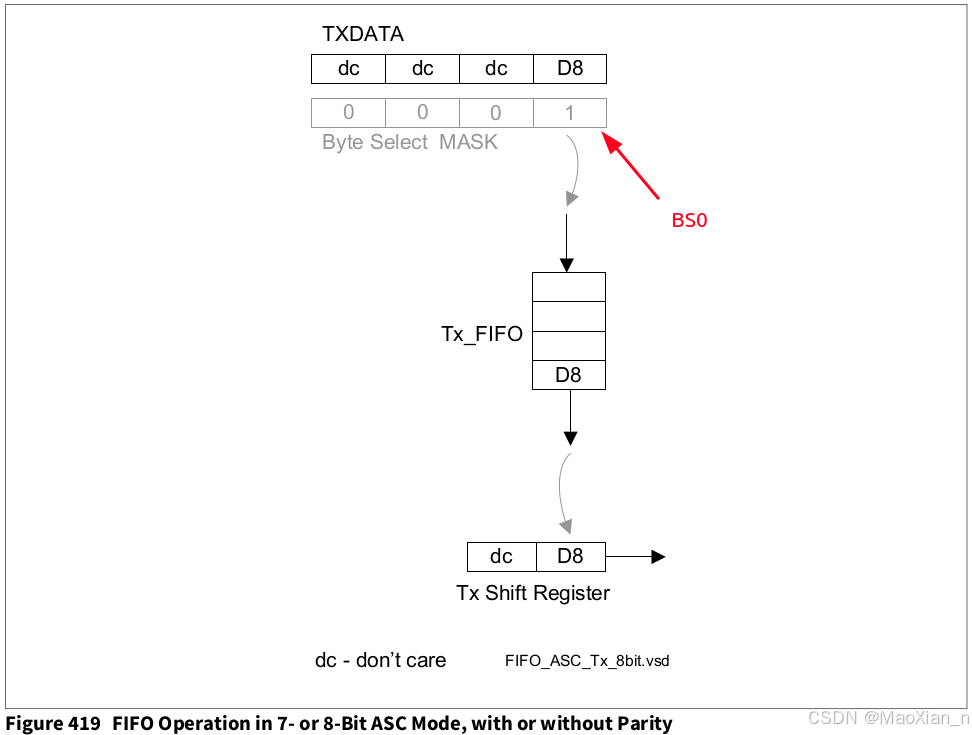

ASC模式的典型用法是发送7-bit或8-bit的值,按照FPI总线设置的数据宽度将8-bit数据写入FIFO

FPI总线宽度为8-bit时,只有BS0(Byte Select 0)信号为激活状态

待发送的数据会被写入TXDATA寄存器,Tx_Inlet_Width和Tx_Outlet_Width均为8-bit

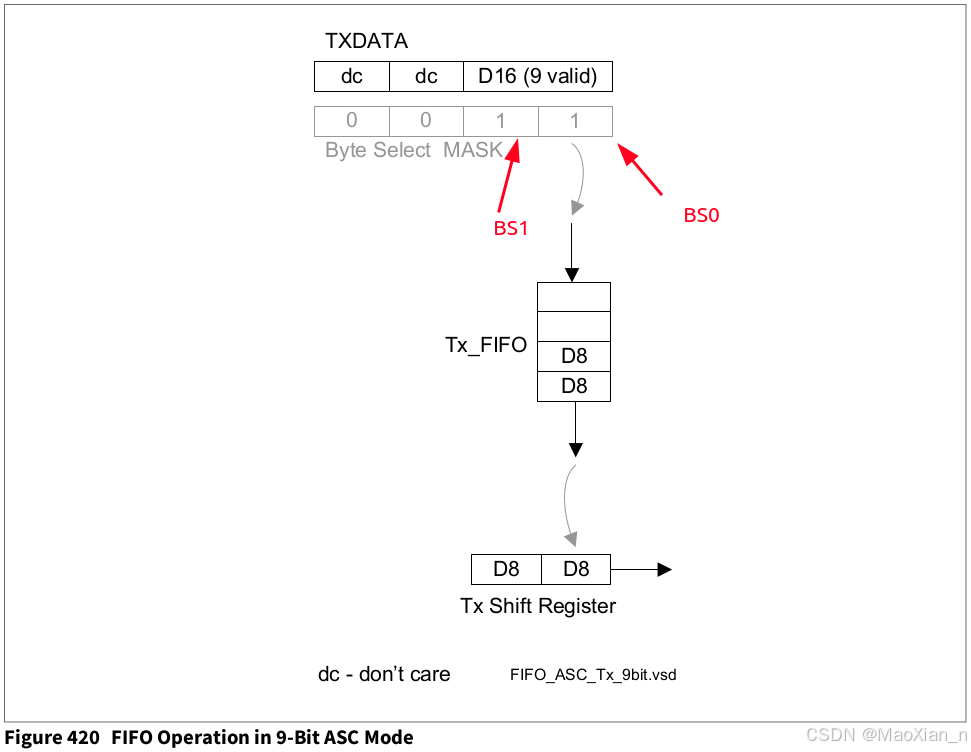

ASC不常用的模式是发送9-bit的值(包括9-bit或8-bit的数据),此时FPI总线宽度为16-bit,同时Byte Select信号的BS0和BS1激活,移位寄存器的读取指针指向的位置,将会被填充两个8-bit的值,并且将读取指针加1

待发送的数据被写入TXDATA寄存器,Tx_Inlet_Width和Tx_Outlet_Width为16-bit

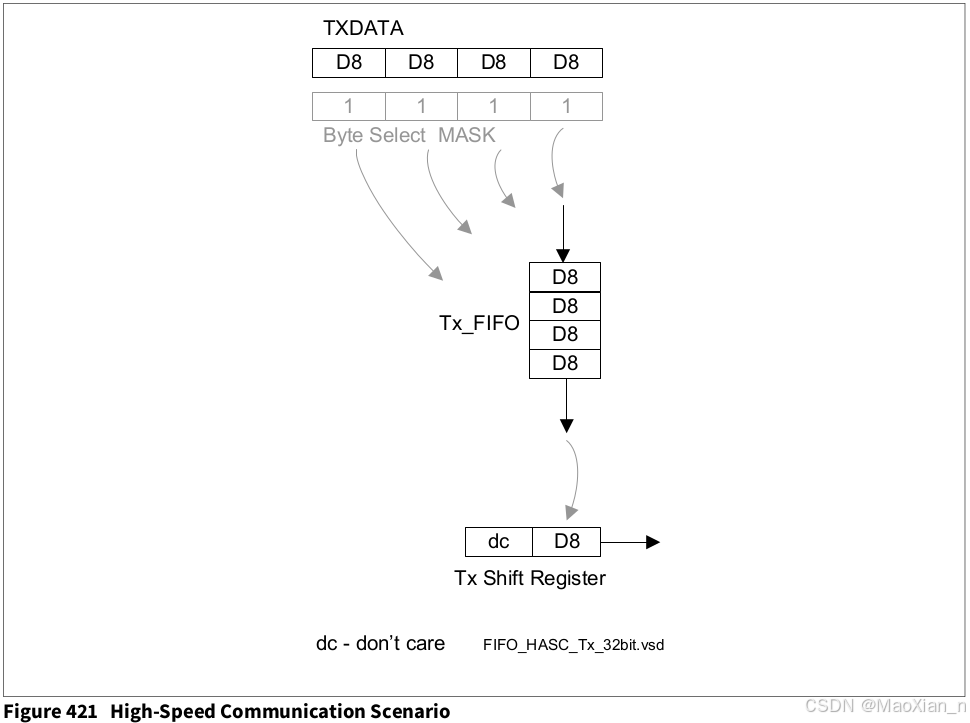

36.3.2.2.2.高速ASC模式

为了降低FPI的总线负载,不使用一次性移动32-bit的方式处理总数为32-bit但是单个为7-bit或8-bit的值,一种方法是在FPI总线数据宽度为32-bit时,使用4个8-bit宽度的值填充FIFO(将32-bit的值拆分为4个8-bit的值),此时所有的Byte Select信号(BS[3:0])均被激活,同时在一个周期内将所有的4字节的数据写入TxFIFO,同时TxFIFO写入指针加4

待发送的数据被写入TXDATA寄存器,Tx_Inlet_Width为32-bit,Tx_Outlet_Width为8-bit

36.3.2.2.3.LIN模式

LIN模式中,若干8-bit的数据帧前会有一个间隔域(Break Area)

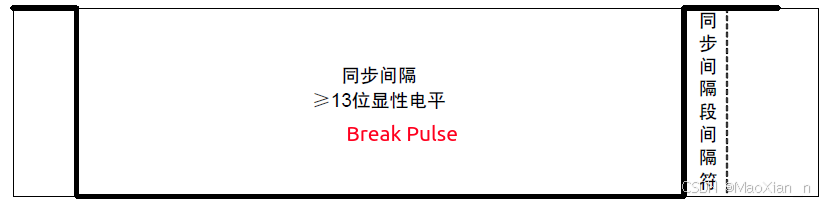

Break Pulse由一个6-bit的可编程定时器产生,例如,产生13~26-bit的间隔域(最多64-bit,但会影响LIN头部)

Break Pulse检测由一个可编程的8-bit定时器实现,此外,也可以设置10-bit或11-bit倍数的标准阈值

Pulse由内部定时器模块产生,待发送的数据序列包含若干字节的数据,用于填充TXFIFO寄存器,随后发送Break Pulse激活TxFIFO

待发送的数据被写入TXDATA寄存器,Tx_Inlet_Width可以为8-bit、16-bit、32-bit,Tx_Outlet_Width为8-bit

36.3.2.2.4.SPI模式

SPI模式是最常用的模式为发送或接收8~16-bit数据,因此,从TxFIFO中读取数据的宽度必须为8-bit或者16-bit,写入数据的宽度为16-bit,如果一次FPI总线读写操作包含了两帧数据,那么写入数据宽度也可以为32-bit

待发送的数据写入TXDATA寄存器,Tx_Inlet_Width最大为32-bit,Tx_Outlet_Width最大为16-bit

36.3.2.3.TXFIFO中断生成

TXFIFO提供了三种中断产生方式,由寄存器位TXFIFOCON.FM控制

-

Single Move Mode -

Batch Move Mode -

Combined Mode

TXFIFO和RXFIFO可以独立的使用不同的中断方式

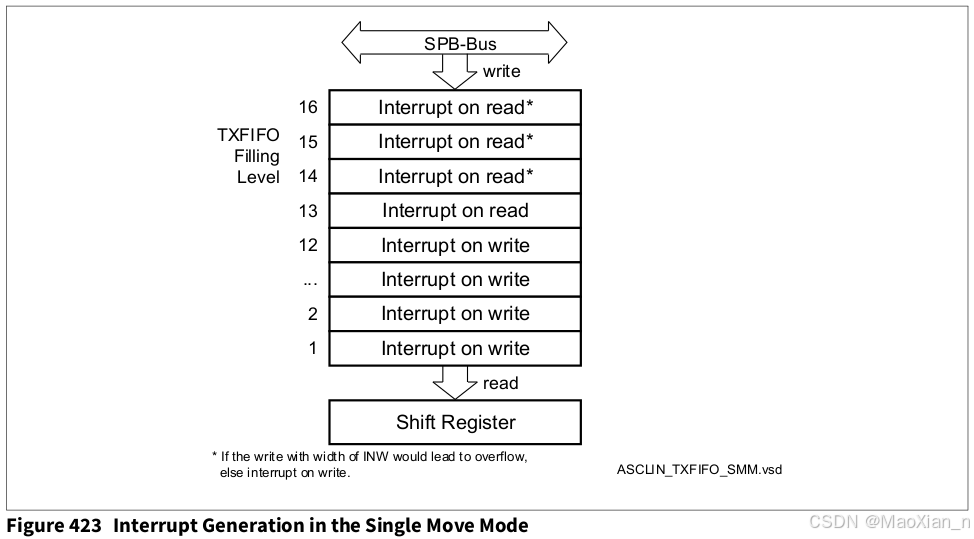

Single Move模式

Single Move Mode是为了使得TXFIFO尽量被填满,一旦TXFIFO中有空闲空间可以立即填充数据

Single Move Mode支持在每个TXFIFO中断产生时,使用Single Move的方式操作DMA

每次向TXFIFO写入时都会触发一次DMA请求,因此至少会有一个空闲的空间可用

如果写入操作将TXFIFO写满,或下次写入会导致TXFIFO溢出,则不会产生中断以避免溢出,这次的中断在移位寄存器进行一次读取后产生,以保证有足够的空间接收INW所设置宽度的数据

为了在上电后触发第一个Refill中断,必须使用软件对TXFIFO进行一次写入操作,或者在TXFIFO中断节点中设置中断标志位,在此之后,DMA或者中断通知链的生命周期会持续到所有读写操作结束

注意:Single Move Mode中,多个软件进行读写操作,或按块移动DMA将会产生多个中断,并导致Events丢失,因此应该避免这种情况产生,当TXFIFO将要填满或者已经填满时,刷新操作将会触发FLAGS.TFL中断

Batch Move模式

Batch Move Mode是为了当TXFIFO中存在多个空闲元素时减少中断数量,例如在一次中断时进行多次移动

Batch Move Mode中仅当Filling Level小于等于设定阈值时才产生中断,该值由寄存器位TXFIFOCON.INTLEVEL定义

注意:为了保证下次中断能正常产生,TXFIFO必须Refill至Filling Level大于中断阈值

当波特率较高但数据帧较短时,若干数据帧会在TXFIFO触发Refill时才会被发送,例如,中断阈值设置为3个元素,则中断会在Filling Level小于3时产生,从而空出两个元素,若TXFIFO的Refill时间延迟太久,以至于已经传输了两个数据帧,则此时的TXFIFO会为空,但填充两个数据帧无法达到中断阈值,因此,除非CPU轮询当前Filling Level或者继续填充数据直至超过阈值,否则不会产生下一个中断(理想情况下TXFIFO在每次Move时都会重新填满)

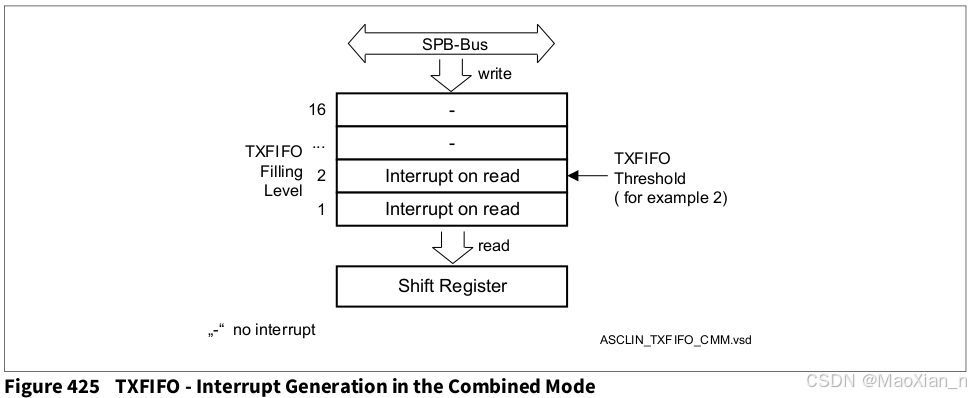

Combined(Compatibility)模式

每次从TXFIFO中取出数据时都会检查Filling Level,当其小于等于INTLEVEL时产生中断,该值由寄存器位TXFIFOCON.INTLEVEL定义

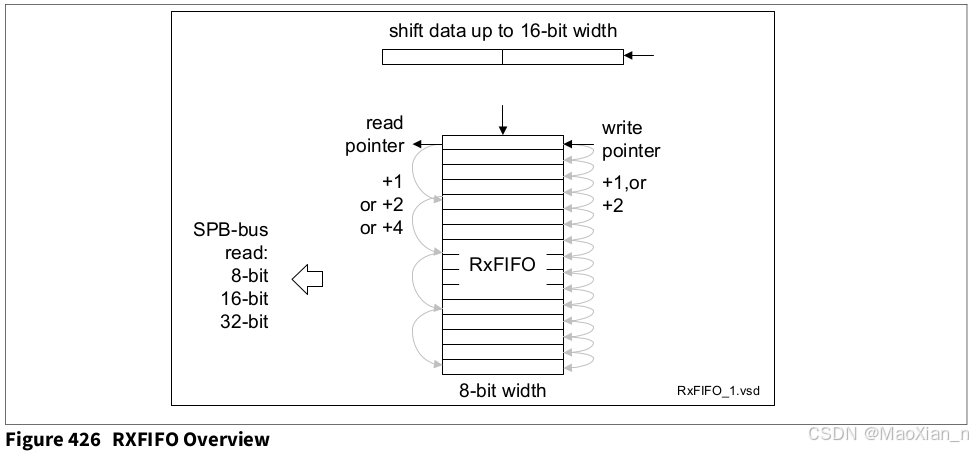

36.3.2.4.RxFIFO概览

RxFIFO可以将两个8-bit的数据帧或者一个16-bit的数据帧写入16-bit宽度的FPI总线中,也可以将4个8-bit的数据帧或者两个16-bit的数据帧写入FPI总线

从RxFIFO中取出数据的长度由寄存器位RXFIFOCON.OUTW定义,SPB总线读取宽度应该与OUTW相等

如果SPB总线读取宽度小于OUTW,则多出来的部分会丢失,如果大于OUTW,则不足的位会补0

移位寄存器按照寄存器位DATCON.DATLEN中定义的数据长度填充RxFIFO

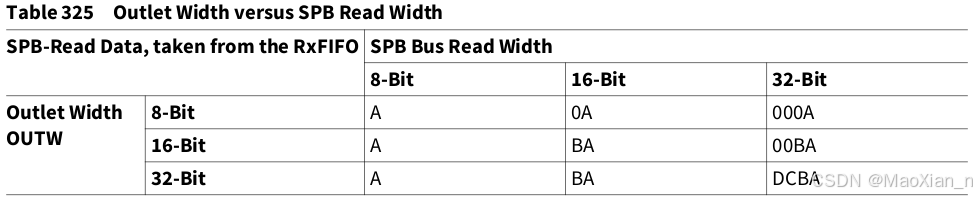

下图展示了输出宽度和SPB总线宽度的关系,RxFIFO中的字节为A、B、C、D,其中A先被取出(填充字节为0)

注意:在Underflow情况下,例如,对RXDATA进行读取操作,按照RXFIFOCON.OUTW定义的数据宽度从RXFIFO中取出对应的字节数,如果其长度超过了RXFIFO中实际存储的数量(大于RXFIFOCON.FILL),此时不足的位会补0以满足读取宽度,此时数据仍保存在RXFIFO中并且不会改变RXFIFOCON.FILL,如果需要清空RXFIFO则必须使用软件清空,同时设置FLAGS.RFU标志位

36.3.2.5.使用RxFIFO

36.3.2.5.1.标准ASC模式

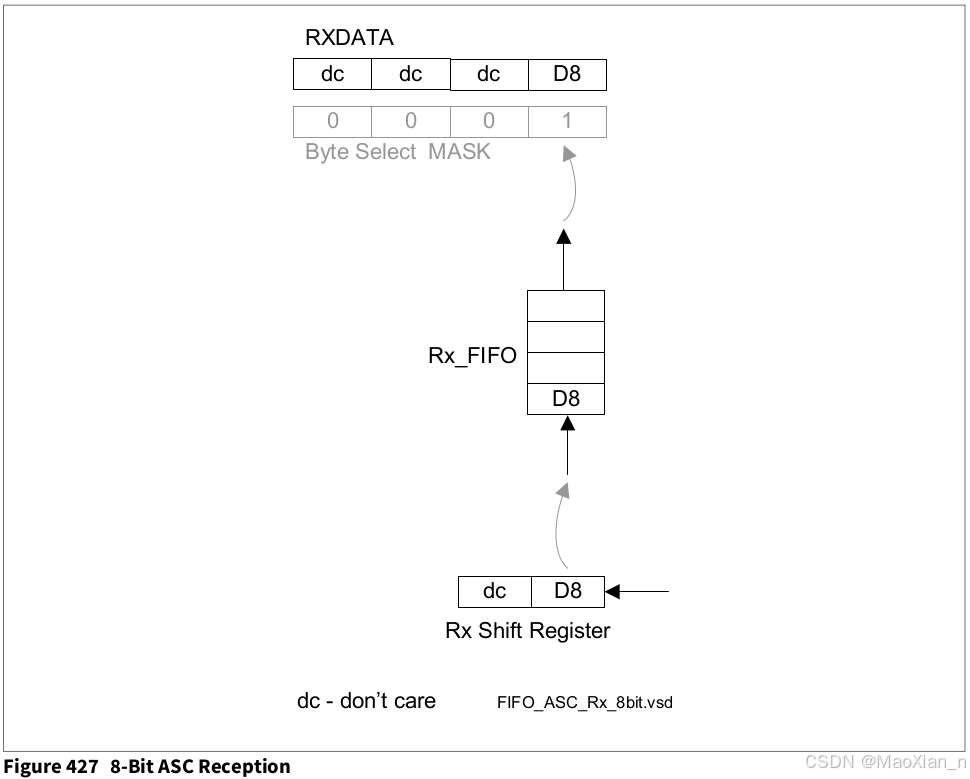

待接收的数据从RXDATA寄存器中读取,当数据宽度为7-bit或8-bit时,每次读取都会从该地址中取出一个字节的数据,同时将RXFIFO存储这几位数据的一个单元清空,此时Rx_Outlet_Width为8-bit,Rx_Inlet_Width为8-bit

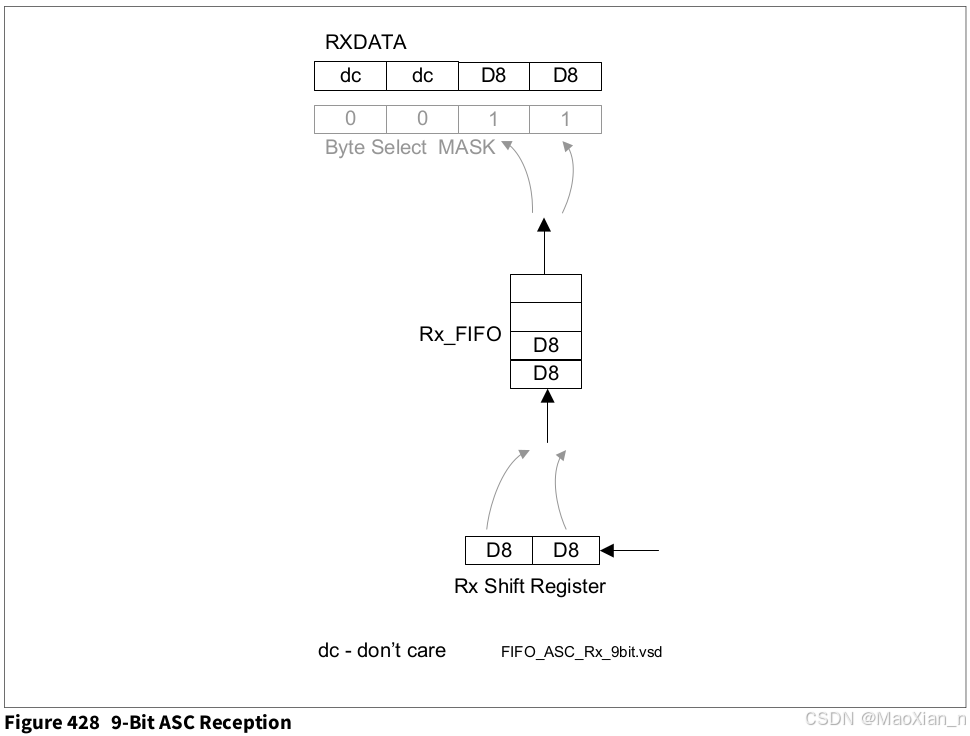

当数据宽度为9-bit时,每次读取两个字节并清空两个单元,此时Rx_Outlet_Width为16-bit,Rx_Inlet_Width为16-bit

36.3.2.5.2.高速ASC模式

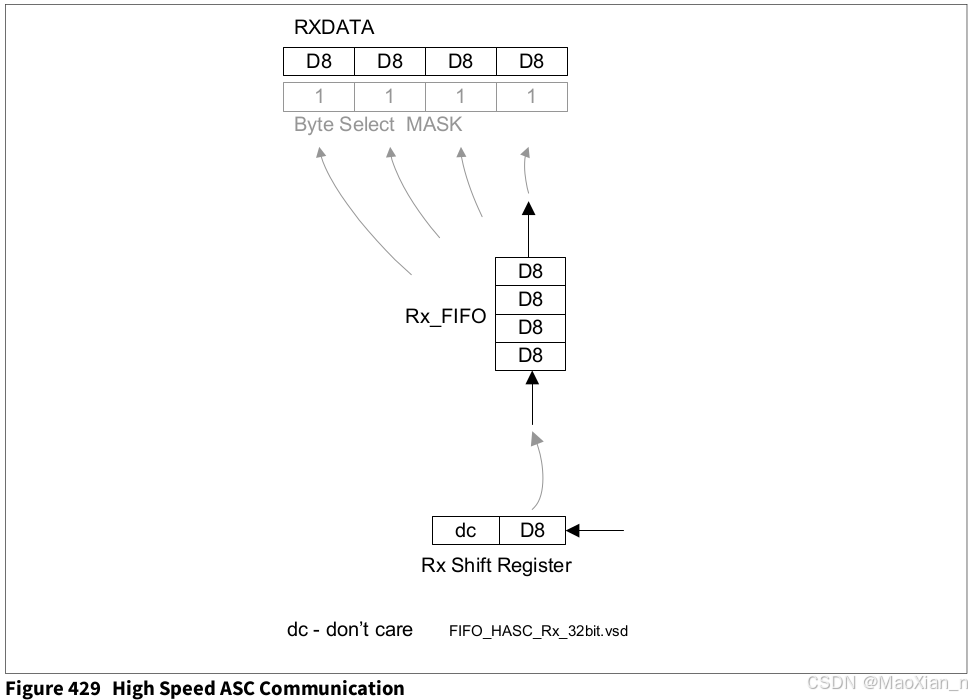

待接收的数据从RXDATA寄存器中读取,当数据宽度为7-bit或8-bit时,每次读取1~4个字节,同时一次性清空4个单元,此时的Rx_Outlet_Width为32-bit,Rx_Inlet_Width为8-bit

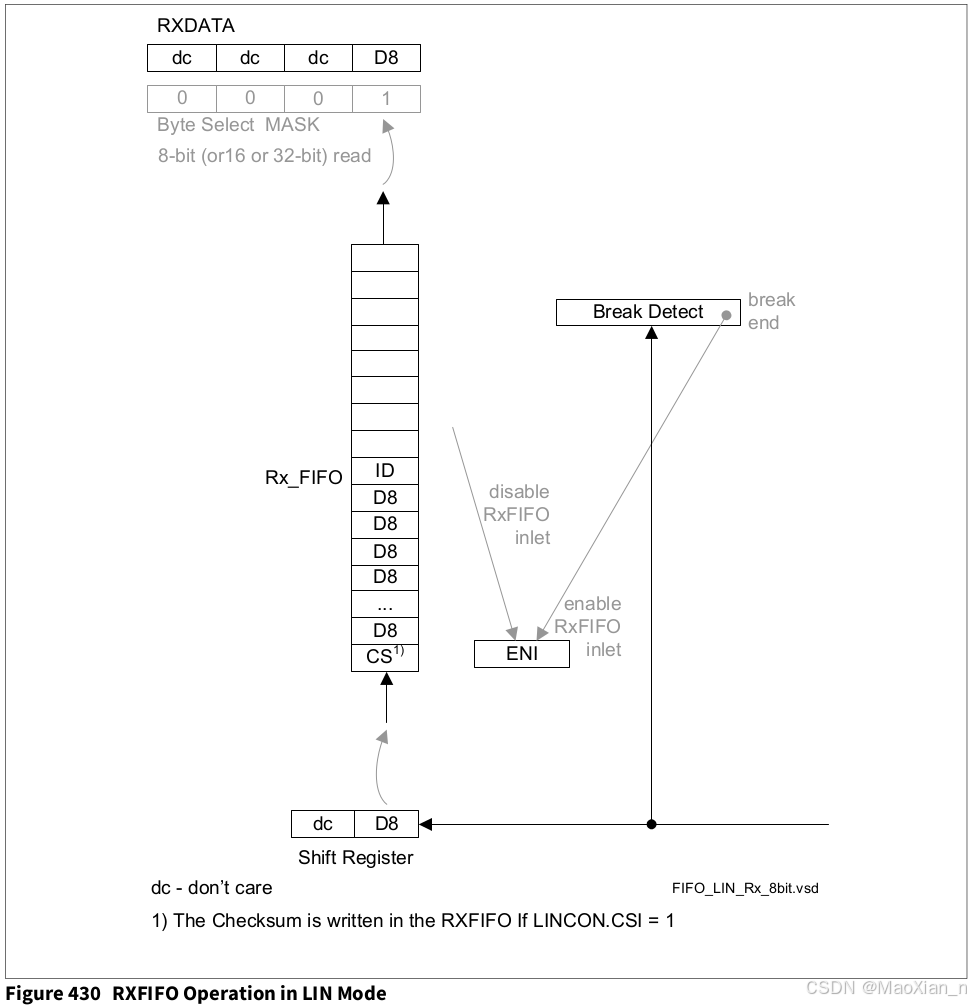

36.3.2.5.3.LIN模式

待接收的数据从RXDATA寄存器中读取,数据读取的宽度为8-bit、16-bit、32-bit,每次读取1个字节,同时清空1个单元,此时Rx_Outlet_Width为8-bit,Rx_Inlet_Width为8-bit

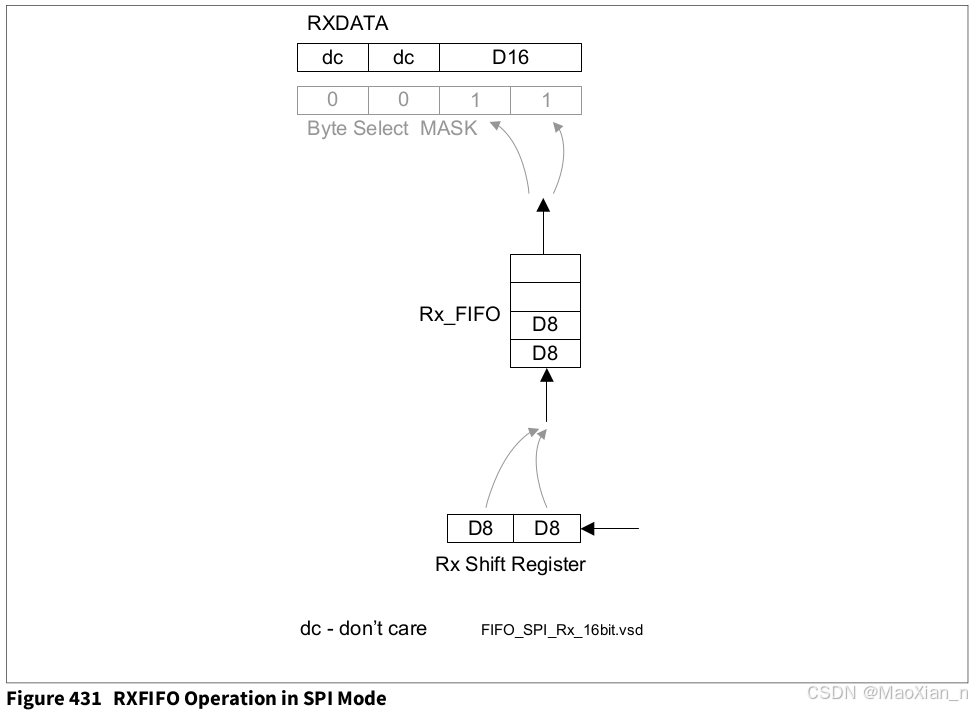

36.3.2.5.4.SPI模式

待接收的数据从RXDATA寄存器中读取,当数据宽度为16-bit时,每次读取2个字节并清空2个单元,此时Rx_Outlet_Width为16-bit,Rx_Inlet_Width为16-bit

36.3.2.6.RTS/CTS握手

当RXFIFO将要写满时接收方会禁用RTS(Request to Send)信号以避免溢出,当开始从RXFIFO中取出数据(例如使用DMA)且Filling Level低于阈值时,会再次使能RTS信号,阈值为RXFIFO大小减4,从而支持使用一字节、两字节、四字节DMA传输,发送方从其CTS引脚接收接收方的RTS信号,同时暂停数据发送

36.3.2.7.RXFIFO中断生成

RXFIFO提供了三种中断方式,由寄存器位RXFIFOCON.FM控制

-

Single Move Mode -

Batch Move Mode -

Combined (Compatibility) Mode

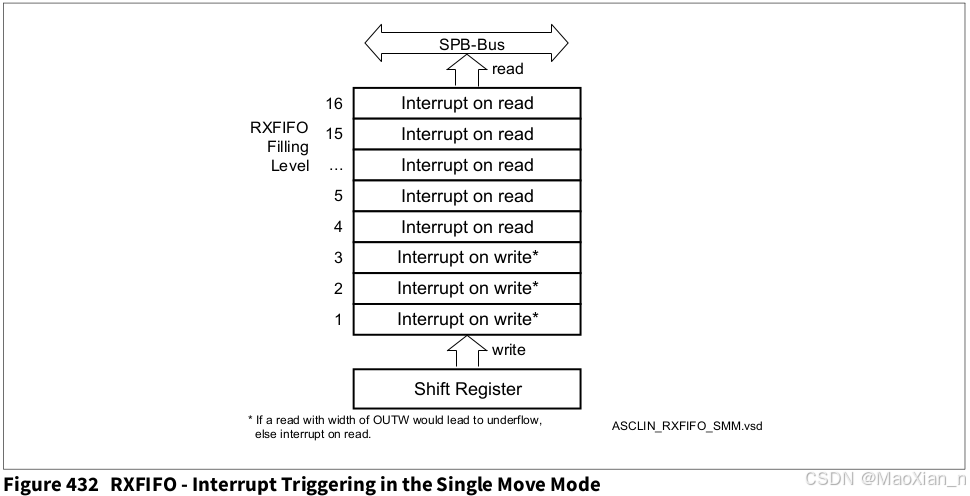

Single Move模式

每次RXFIFO中断执行一次DMA操作,这种模式下会尽可能保持RXFIFO为空(快速输出RXFIFO中的数据),每次从RXFIFO中读取数据后,如果RXFIFO尚未清空则都会触发一次DMA请求

若本次读取使得RXFIFO为空,或者下一次读取会导致RXFIFO中的数据长度,小于RXFIFOCON.OUTW中定义的值,则会触发一次中断以防止这种情况发生,当移位寄存器向RXFIFO中写入一个元素,使RXFIFO宽度满足一个OUTW的宽度时,才会产生中断

移位寄存器将接收到的第一个元素写入RXFIFO中时触发RXFIFO中断,在此之后,DMA中断通知链的生命周期会持续到所有读写操作完成,在DMA所有操作完成后,请求服务的节点中将没有服务请求存在,因此从RXFIFO中读取最后一个元素不会触发中断

注意:在Single Move Mode中,软件一次性进行多次读取,或者按块进行DMA操作会导致多个中断产生,这会导致Event丢失,因此需要避免这种情况发生

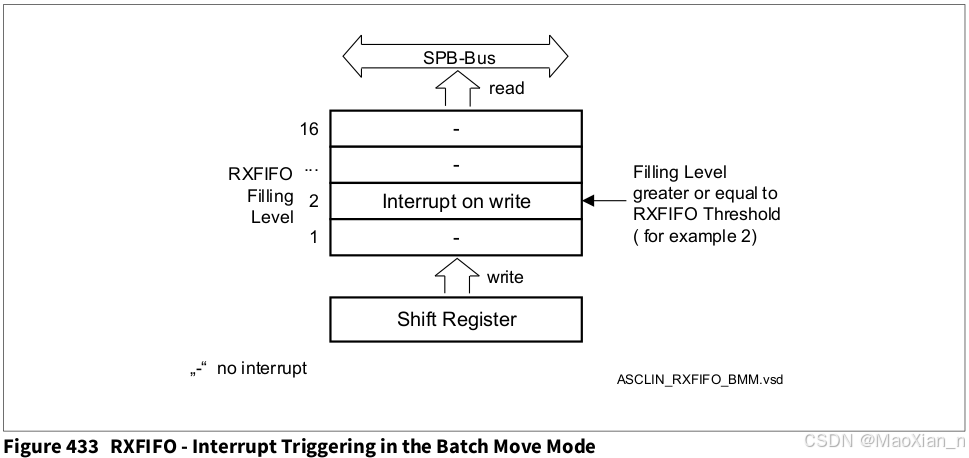

Batch Move模式

Batch Move Mode是为了减少中断次数,例如,在一次中断响应时移动多个元素从而减少CPU中断响应次数

在Batch Move Mode中,当Filling Level继续增加,将要达到或超过设定阈值时才会产生一次中断,这意味着RXFIFO中存在预先定义的若干元素可用,该值由寄存器位RXFIFOCON.INTLEVEL定义

注意:必须保证CPU可以不断清空RXFIFO,并轮询RXFIFO的Filling Level,直至Filling Level降低到中断阈值以下,以此保证下一次中断能正常产生

当数据长度较短且波特率较高时,RXFIFO会在被重新清空前收到多个数据帧,例如,Filling阈值设置为2,中断会在Filling Level大于等于2时产生,如果RXFIFO清空的延迟过长,而此时又来了两帧数据,则RXFIFO会被逐渐填满,那么原本每读取两个帧就能清空RXFIFO的条件就不再满足,在这种情况下就不会产生新的中断,但是当阈值为3或者4时就不会发生这种情况

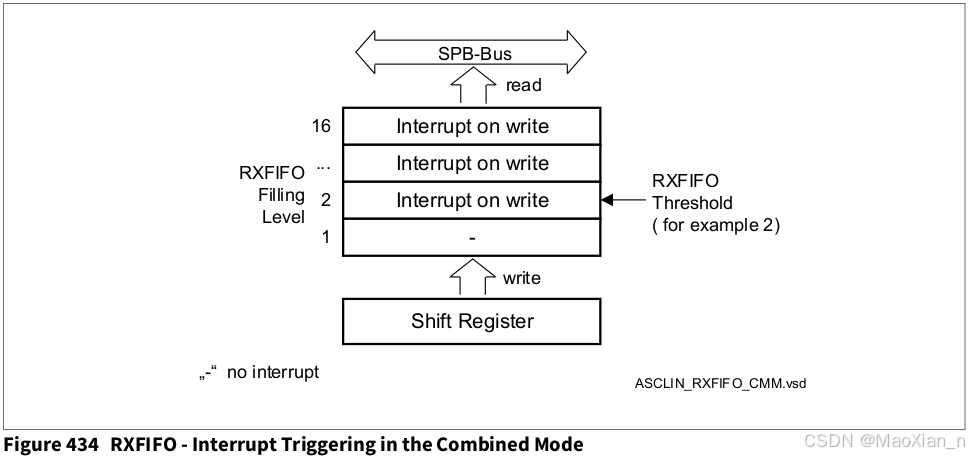

Combined (Compatibility) 模式

当一字节数据发送到RXFIFO时,检测当前RXFIFO的Filling Level,当大于等于INTLEVEL时产生中断,该值由寄存器位RXFIFOCON.INTLEVEL定义

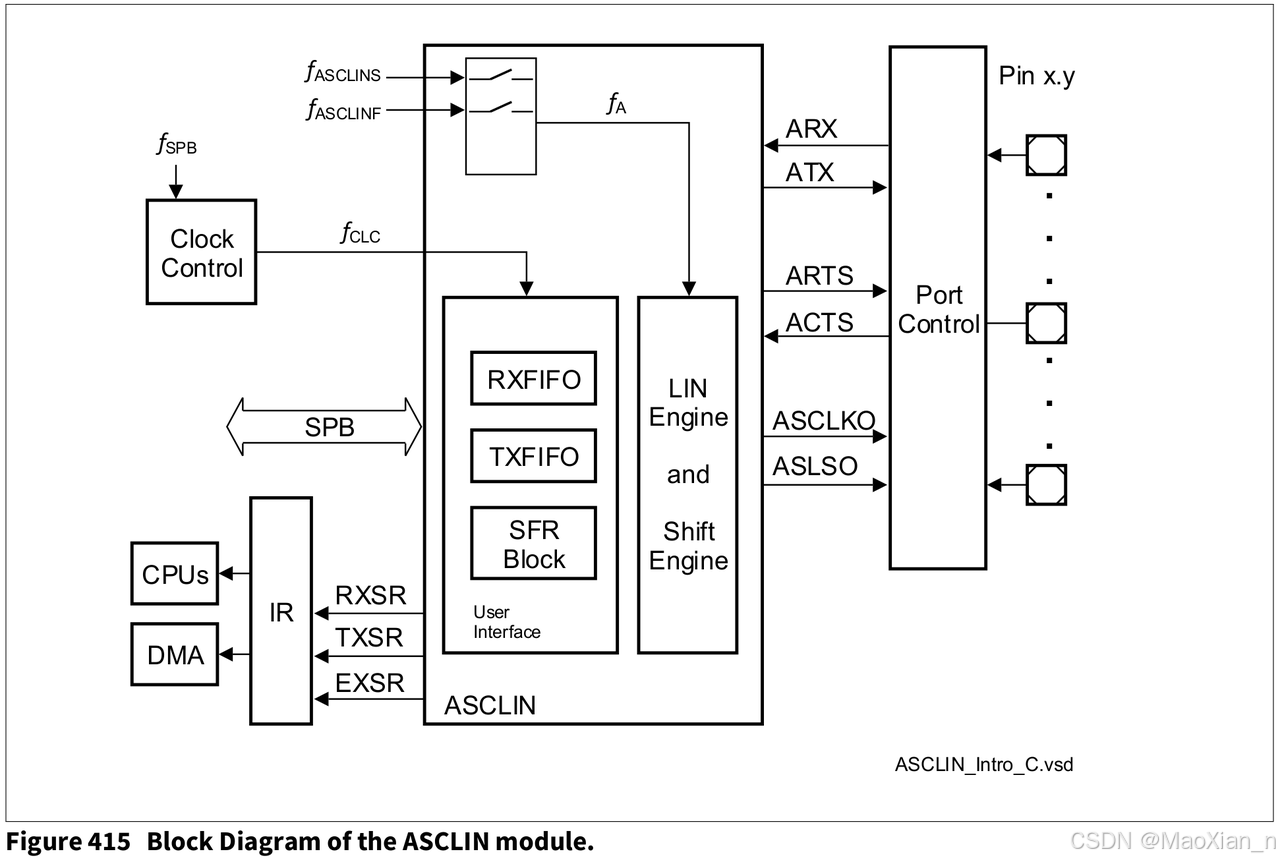

36.3.3.时钟系统

时钟系统为ASCLIN中的各种功能产生所需的时钟信号,如毛刺滤波时钟、超采样时钟、比特时钟和串行SPI时钟

时钟系统fA所使用的时钟独立于SPB总线的时钟,当SPB总线时钟改变时(如低功耗模式)不会影响fA,通过寄存器位CSR.CLKSEL选择fA的时钟源,其可以和SPB总线时钟同步,也可以为异步模式,频率也可高可低

36.3.3.1.波特率生成

分数分频、N分频、超采样分频、可配置采样点

如下几个bit位用于配置28-bit的波特率分频器

-

BITCON.PRESCALER- 预分频器的分频比例 -

BRG.NUMERATOR- 分数分频器的分子 -

BRG.DENOMINATOR- 分数分频器的分母 -

BITCON.OVERSAMPLING- 波特率后分频器的分频比例

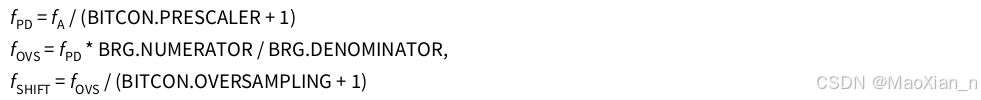

从fA到fSHIFT的计算过程如下:

注意:分数分频需要分子BRG.NUMERATOR小于分母BRG.DENOMINATOR,波特率计算公式如下:

36.3.3.2.位时序

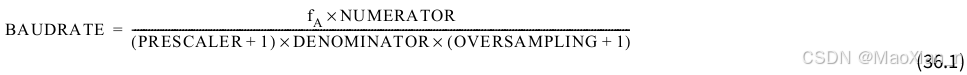

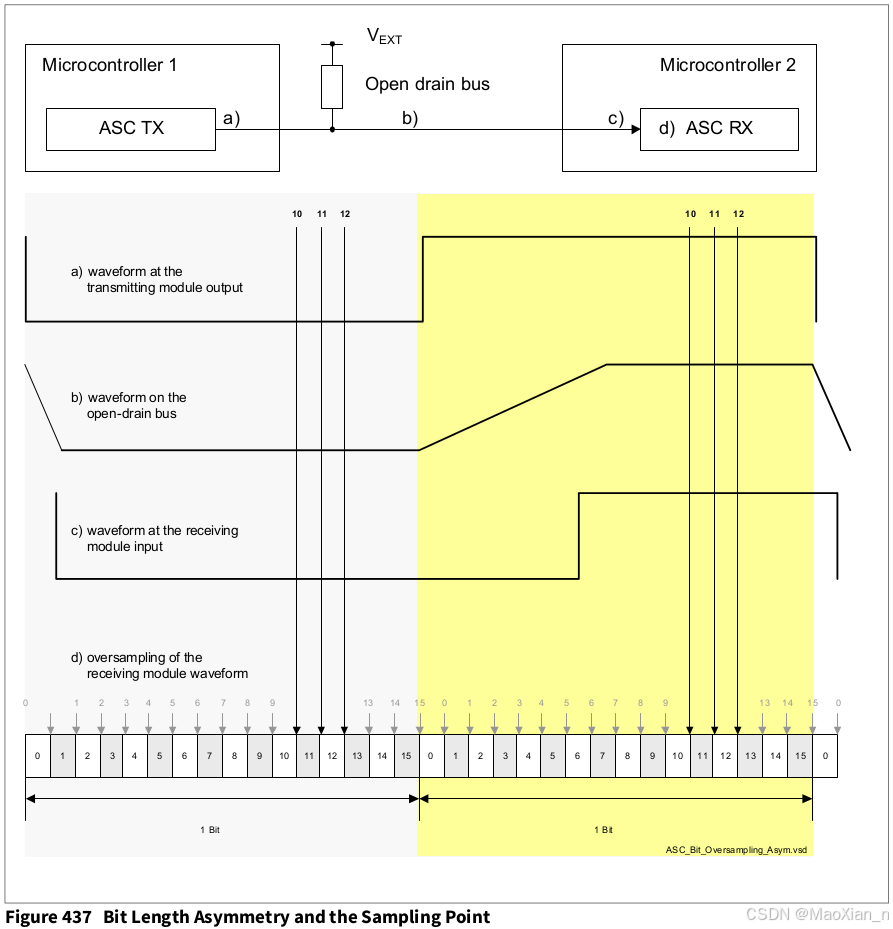

ASCLIN模块提供了多种可配置选项,用于配置超采样、采样点和输入信号滤波的相关属性

输入比特流的超采样系数可配置为4~16倍,即对于输入流的每个bit位,在4~16个ticks时间内连续对其采样,同时,也可以利用超采样频率,形成数字中值滤波处理输入比特流,中值滤波使用三局两胜的方式确定最终的信号值,如果滤波器被禁用,那么每个bit只会被采样一次

采样点也是可以配置的,其需要和超采样因子配合使用,一种标准的使用方法为,使用16倍的超采样率对数据中的7、8、9位进行分析,另一种方式是使用8倍的超采样率对数据的第3、4、5位进行分析

采样相关配置的寄存器位如下所示:

-

BITCON.PRESCALER-12-bit的整数分频器,用于定义分数除法器中使用的MicroTick以生成对应的波特率,同时也用于消除输出信号抖动的数字滤波器 -

BITCON.SAMPLEPOINT- 定义采样点位置和SPI模式中的占空比 -

BITCON.SM- 使能数字中值滤波(三个中的多数):每个bit采样1或者3次 -

IOCR.DEPTH- 定义浮动平均滤波深度:禁用、1 MicroTicks、63 MicroTicks -

BITCON.OVERSAMPLING- 每个比特位采样多少次Ticks(4~16),分数分频器的后采样

采样点应该位于输入比特流的中间位置,如果波特率不是非常准确或者稳定,这个位置是最佳选择,如果晶振的准确性非常高(一个晶振由两个控制器控制会出现这种情况),但是信号边缘非常不对称(使用漏极开路半双工连接会出现这种情况),最好是将采样点移至输入流的后半部分,漏极开路连接会导致比特位0比1长,这种情况下建议将采样点放在比较短的比特位1处,最后,晶振精度、信号边缘对齐程度、冲突检测的Loop-Delay都会影响采样点的最佳位置

36.3.4.数据帧配置

对于数据发送和接收,可使用寄存器位FRAMECON.ODD控制其奇偶校验,使用DATCON.DATLEN控制数据长度,使用FRAMECON.STOP控制停止位

36.3.5.其他配置

参考其他章节Loop-Back

36.3.6.同步模式

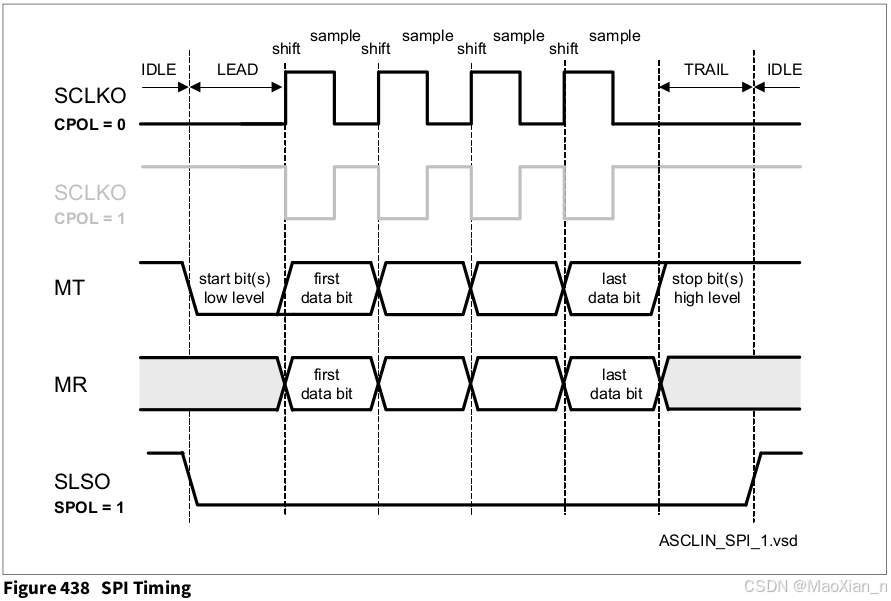

通过FRAMECON.MODE将模块设置为同步模式,同步模式支持先移位后锁存,如下图所示:

36.3.6.1.波特率和时钟生成

同步模式的波特率和时钟生成和异步模式一样,使用相同的预分频器、分数分频器、超采样分频器、可配置采样点,唯一的区别是将移位时钟信号作为输出信号驱动SCLKO引脚,如果请求对称移位时钟则超采样比例应为偶数,同时采样点应该设置为超采样比例的一半,时钟极性由寄存器位IOCR.CPOL控制

36.3.6.2.数据帧配置

前后沿延迟由FRAMECON.LEAD和FRAMECON.STOP控制,FRAMECON.IDLE控制IDLE时间,DATCON.DATLEN用于定义数据长度(2~16-bit)

36.3.6.3.Slave选择配置

SPI Master为每个数据自动使能Slave选择输出信号,IOCR.SPOL配置Slave

36.3.6.4.其他配置

参考其他章节Loop-Back

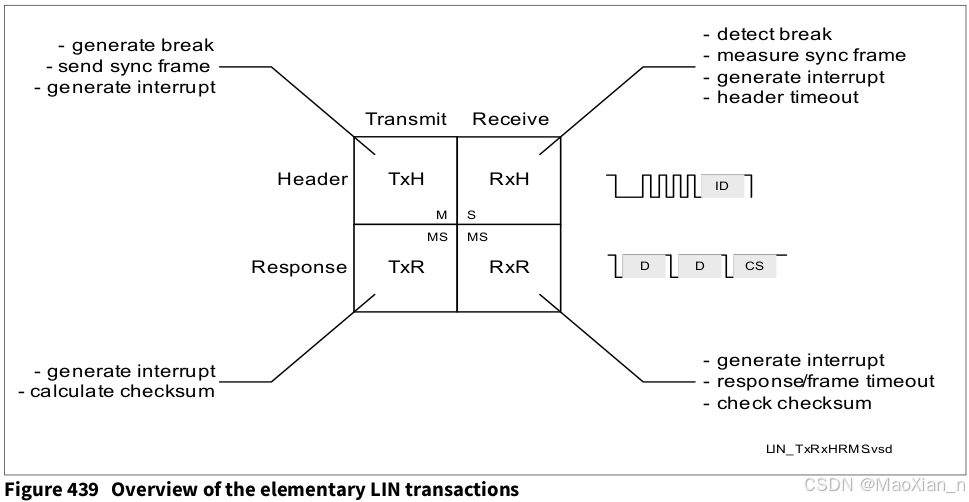

36.3.7.LIN支持

ASCLIN模块为LIN提供硬件支持,支持所有的四种基本的LIN事务:

-

TxH- Transmission of Header,发送报文头 -

TxR- Transmission of Response,发送应答数据 -

RxH- Reception of Header,接收报文头 -

RxR- Reception of Response,接收应答数据

支持Master和Slave模式,Master模式只会执行TxH、TxR、RxR,该模式下不会执行RxH(只负责发送Header),Slave模式只执行RxH、TxR、RxR,该模式不会执行TxH(只负责接收Header)

每种基本事务都需要一些硬件资源以减少CPU的介入:

-

TxH- 发送Header(Master Mode Only)-

Break生成:6-bit字段,以位为单位定义Break长度 -

Sync-Field生成:固定值55H -

带中断生成的

ID传输

-

-

TxR- 发送Response(Master & Slave Mode)-

若干字节数据:

4-bit字段 -

校验和生成:硬件引擎,可支持经典校验和与增强校验和,可以使能或禁用

-

-

RxH- 接收Header(Slave Mode Only)-

自动波特率检测(可选):分数分频器以及可编程的分子和分母

-

若干字节数据:

4-bit字段 -

Header结束中断(必须设置RxR阶段的字节数量) -

溢出超时:

8-bit定时器 -

Break检测:8-bit定时器和可编程的阈值(以位为单位)

-

-

RxR- 接收Response(Master & Slave Mode)-

若干字节数据:

4-bit字段 -

校验和检测:硬件引擎,支持经典校验和与增强校验和,可以使能或禁用,可标记校验和错误并触发错误中断

-

校验和:可以将校验和发送至

RXFIFO -

溢出超时:

8-bit定时器

-

Break检测永远处于激活状态,Master和Slave模式下均能生成Wake-UP信号

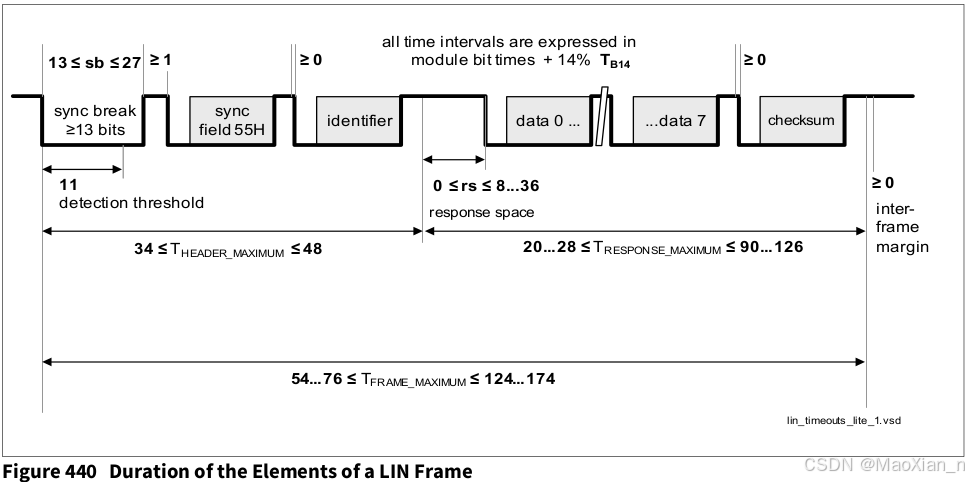

ASCLIN提供的LIN可配置参数比协议标准值范围更大,使用时要注意一些值要符合协议的标准值,如下所示:

-

Break length -

Data width -

Break threshold -

Wake-up length -

Header、frame and response timeout -

Idle time

36.3.7.1.Watchdog

监视Header周期、数据帧、应答、Break Pulse,按预定义的时间阈值检查,超时触发中断,在Slave模式中是必须的

唤醒脉冲由移位寄存和包含多个0-bit的数据字节完成,唤醒脉冲检测采用下降沿检测

为监测总线是否长期处于IDLE或ZERO状态,可以使用轮询的方式

Header超时时间在模块初始化的时候设置,并且在后续都保持不变

帧或者应答超时时间由Response长度(1~8字节)决定,必须在Header接收后由软件根据接收到的ID进行设置,超时初始值由软件设置为最大允许值(256)

模块提供了并行的时钟并根据LIN协议的要求执行Watchdog功能

36.3.7.1.1.Break, Wake, Stuck处理

本小节包括:

-

Monitoring the LIN Bus- 监测LIN总线 -

Break Pulse detection and generation- 间隔域检测及生成 -

Wake Pulse detection and generation- Wake Pulse监测及生成

监测总线

配置FLAGS.RED和FLAGS.FED检测总线是否长时间处于IDLE或停滞状态,使用轮询(如1ms、10ms一次)的方式进行监测,通过配置FLAGSENABLE寄存器中的相关位可以使能中断生成,可使用寄存器FLAGSSET或者FLAGSCLEAR设置或清除对应的标志位

注意:Low Break Pulse和Wake Up Pulse不会导致虚拟字节传输至接收的FIFO,也不会导致帧违规错误中断,脉冲发出后移位寄存器进入初始状态,并等待下一帧开始位的下降沿

Break/Wake Pulse检测

使用10~11-bit的阈值检测Break Pulse(至少13-bit连续的低电平),由LINBTIMER.BREAK配置

在帧的任何位置检测到Break Pulse,都会将LIN重置为BDD(Break Delimiter Detected)状态,包括Watchdog在内整个序列都会从头开始

注意:在帧的任何位置检测到Break Pulse都会设置Frame Error Flag(FE)

通过监测总线在睡眠模式中的下降沿检测Wake Pulse,可以配置IOCR.DEPTH (Glitch Filter)屏蔽过早的唤醒信号

Break/Wake Pulse生成

LINBTIMER.BREAK定义Break Pulse长度(1~64-bit),Wake Pulse一般为5-bit,也可以设置为1~9-bit(通过向TXFIFO中写入对应的字节请求设置FLAGS.TWRQ)

注意:Low Pulse会禁用移位寄存器接收,因此Low Pulse不会被认为是一个正常的ASC帧

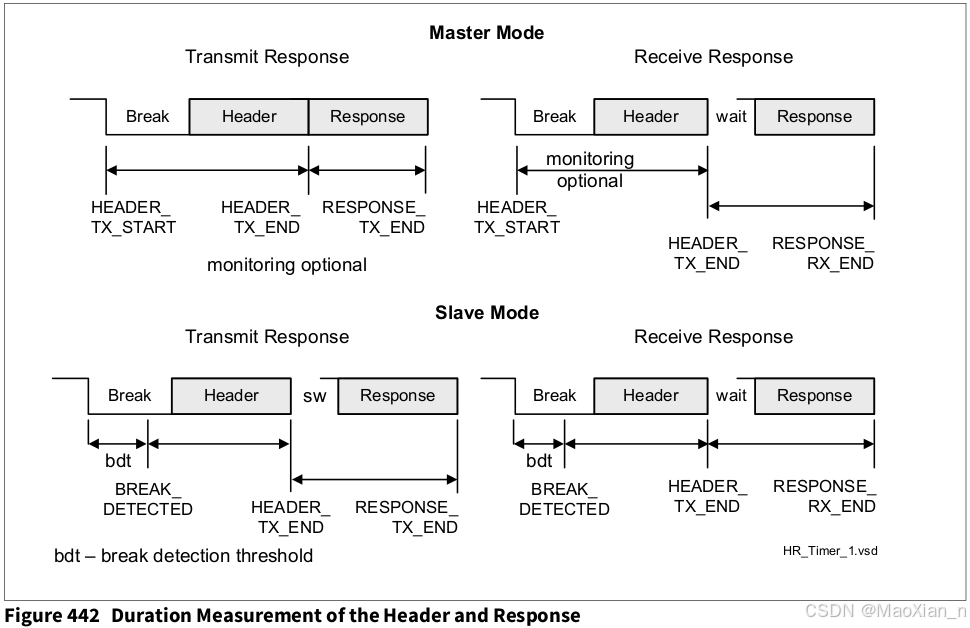

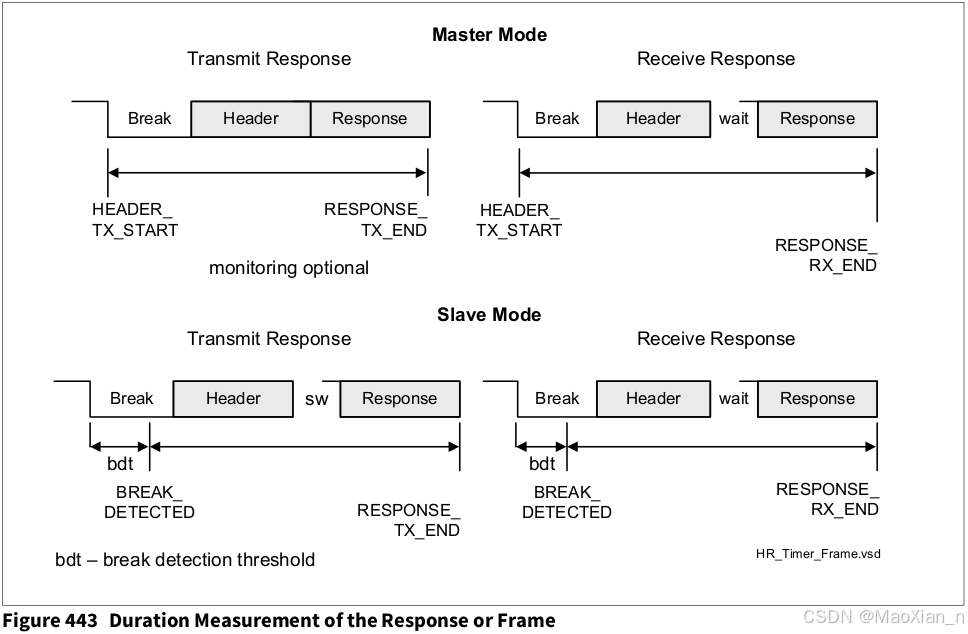

36.3.7.1.2.报文头和应答帧时序

可以分别监测Header和Response

-

Header duration measurement-

Master Mode中的时间测量起始点为Break Pulse的下降沿 -

Slave Mode中的时间测量起始点为Break Pulse结束(检测到连续的10或11-bit低电平)

-

-

Reponse duration measurements-

Master & Slave Mode中时间测量起始范围为Header结束至Respon结束时间

-

注意:为了检测一些错误情况,传输主节点可以监测自己的Header或者Response超时,例如TXFIFO没有包含ID或者将要传输的数据,但是,这些错误情况也可以通过其他方式进行检测

根据寄存器标志位DATCON.RM中的设置,DATCON.RESPONSE定义了Response或帧间隔阈值

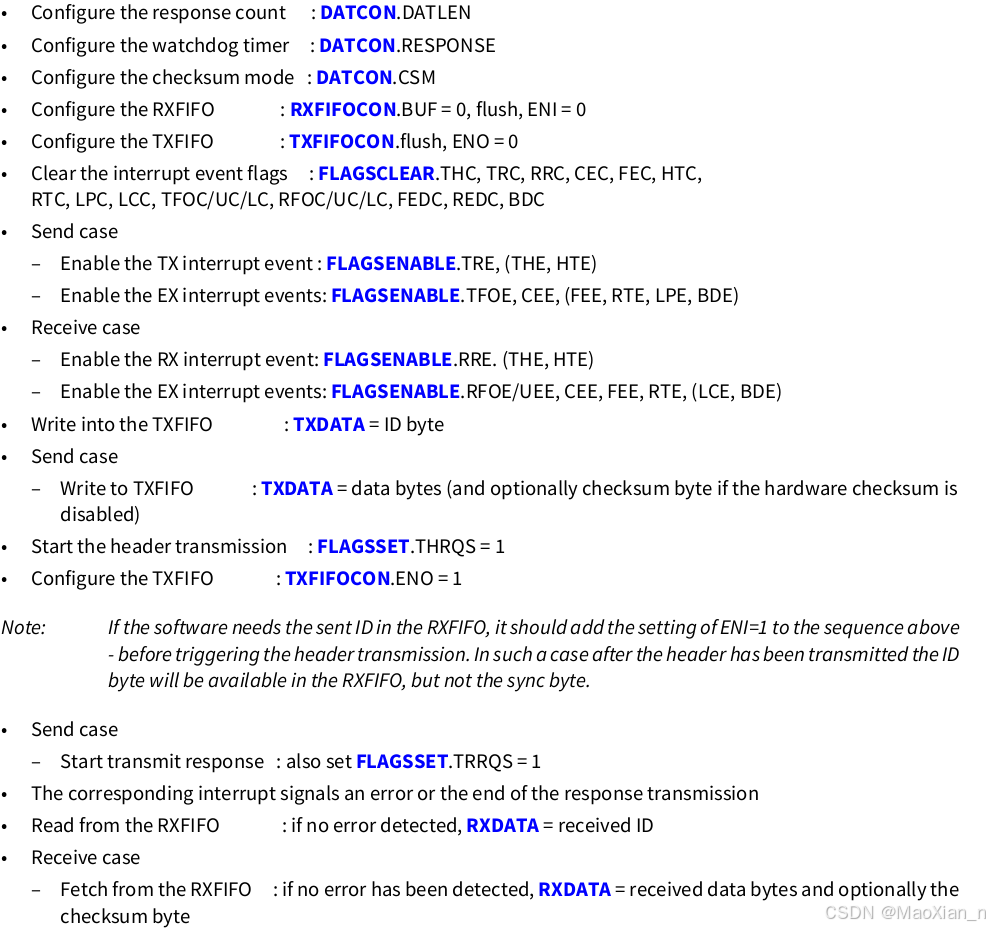

36.3.7.2.Master时序

如下所示的序列展示了如何执行LIN事务,还有其他方式可以实现该序列,例如,使用其他Events控制协议流(用FIFO事件替代Header/Response结束事件):

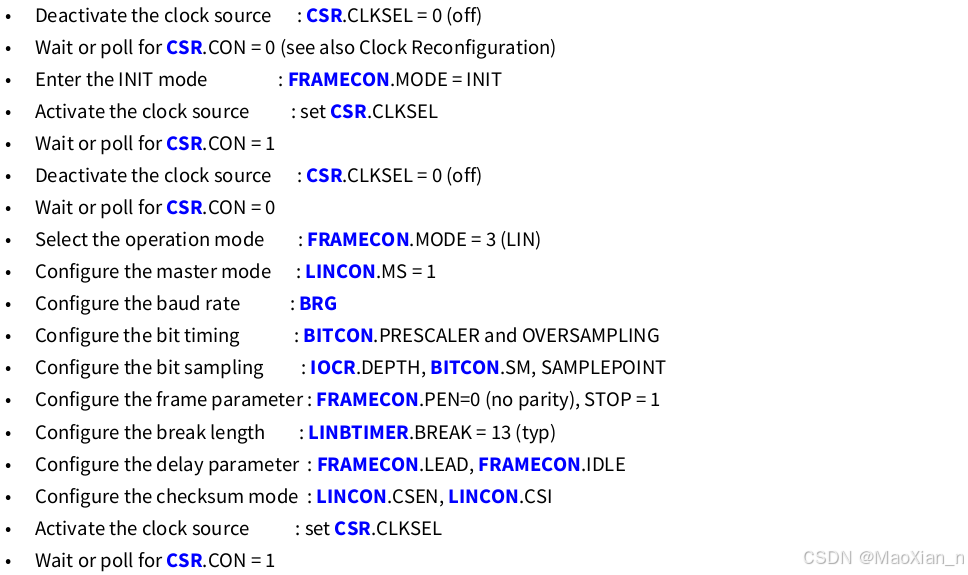

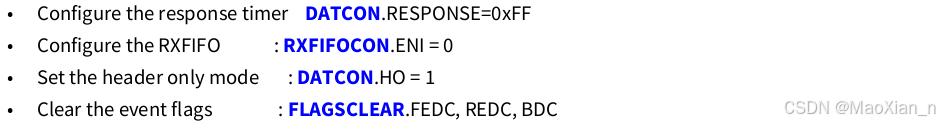

初始化模块

仅发送报文头[master task]

注意:如果软件需要在RXFIFO中发送ID,则需要在该序列执行前设置ENI=1(在触发Header发送之前),该情况下当Header发送完成后就可以操作RXFIFO中的ID字节,而不是Sync字节

响应中断表示ID字节传输/接收结束:

-

Check the error flags:FLAGS.HT、CE(FE、LP) -

Read from the RXFIFO:若未检测到错误,则RXDATA=received ID

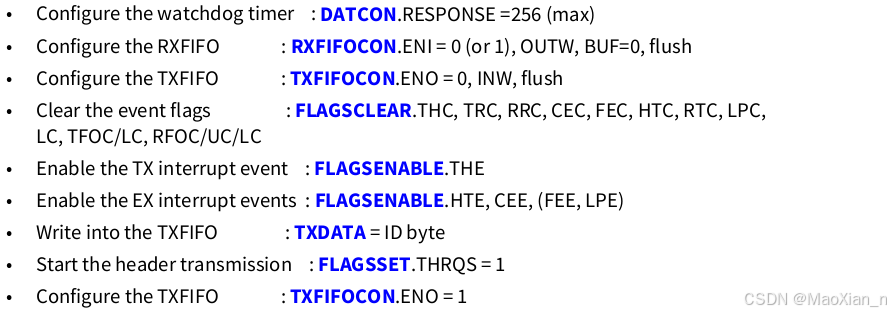

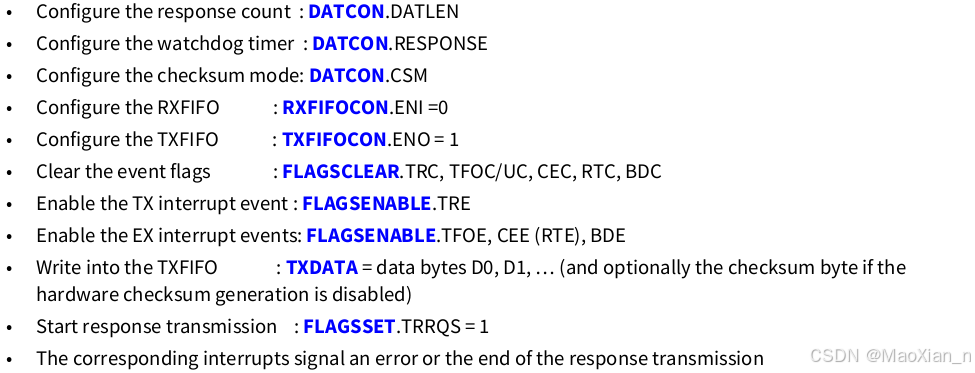

向最新的报文头发送应答[slave task]

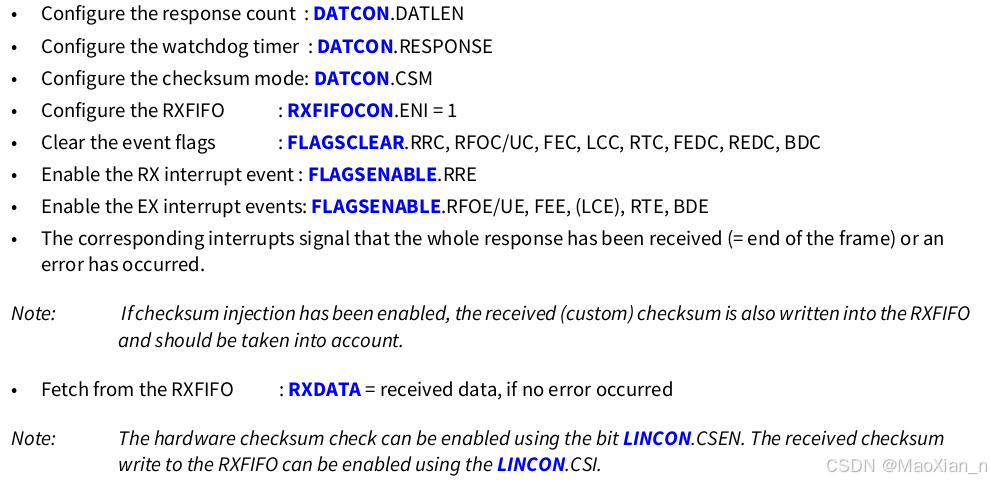

从最新的报文头接收数据[slave task]

忽略最新的报文头[slave task]

除非Slave并非一定响应,LIN Master始终知道Header之后是由自己发送Response还是接收Slave的Response,或者Response传输路径是Salve to Slave

在访问始终响应的Slave时建议先配置Header和Response,之后再开始Header及其他部分的传输

开始LIN传输[master mode]

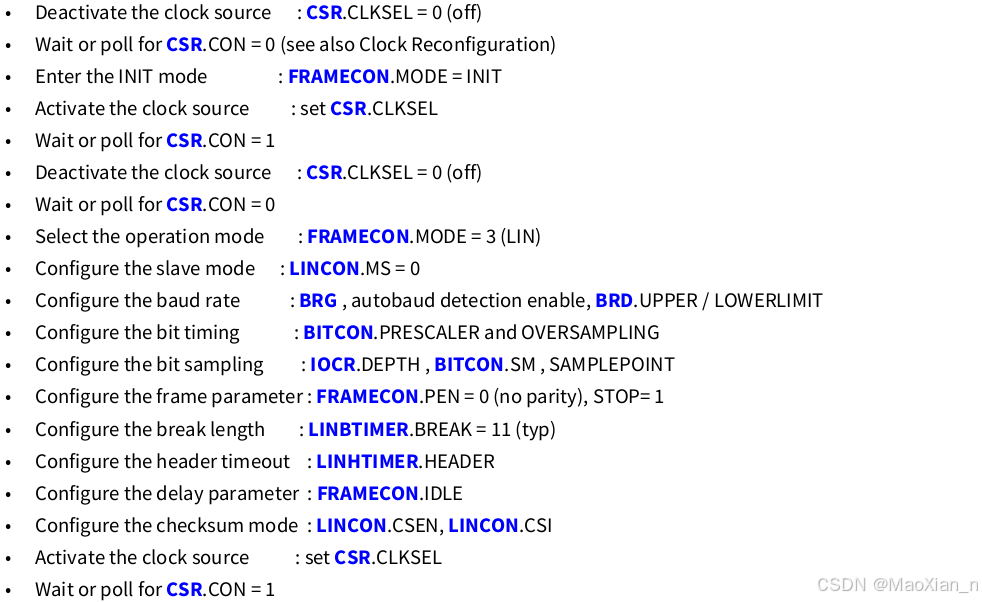

36.3.7.3.Slave时序

如下所示的序列展示了Slave如何执行LIN事务,也可以通过其他方式实现,例如使用其他Events控制协议流(用FIFO事件替代Header/Response结束事件):

初始化模块

Slave模式下,模块会等待从Master发送的Header,即等待跟随在Sync字节和ID之后的Break Pulse

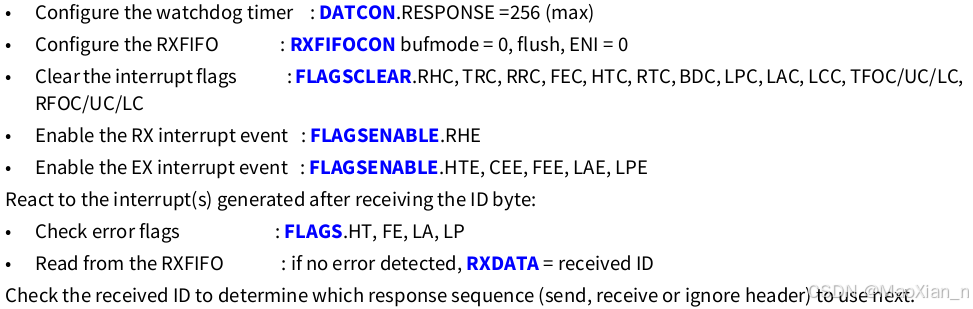

配置报文头接收[slave task]

LIN Slave事先不知道自己应该响应Header,还是会收到另一个Slave发送的Response,其会检查接收到的ID信息,以确认该ID是与Transmit Response关联还是Receive Response关联,又或者直接忽略(由其他Slave发送),Look-Up操作和确认操作应该由软件在允许的Response时间内完成

向最新的报文头发送应答[slave task]

(same sequence as in master mode)

从最新的报文头接收应答[slave task]

(same sequence as in master mode)

忽略最新的报文头[slave task]

如果接收到的ID包含错误,或者该报文头不是发送给该从节点的

(same sequence as in master mode)

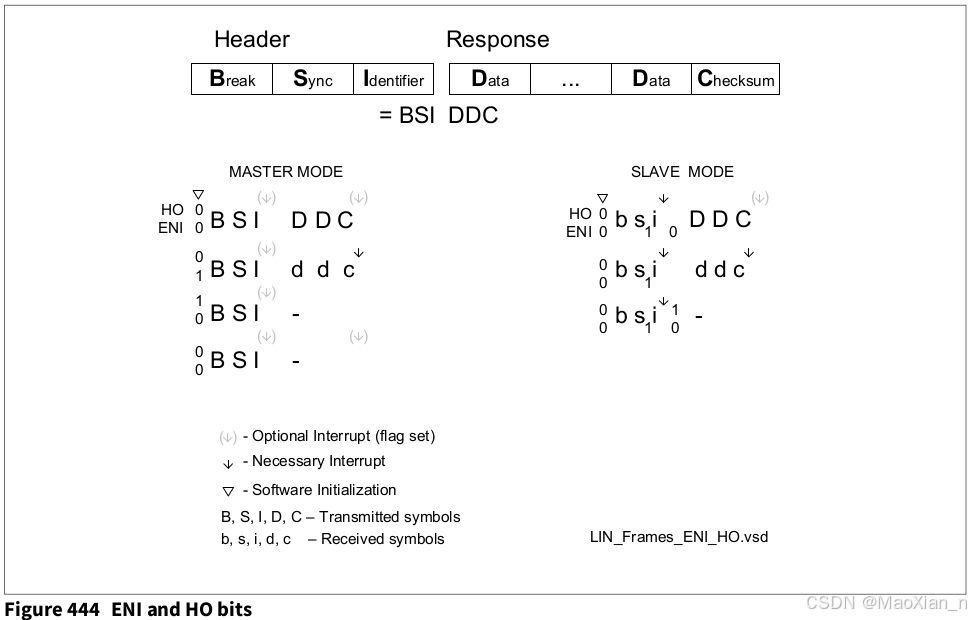

36.3.7.4.使用ENI和HO位

ENI (Enable Input)和HO (Header Only)会影响LIN帧中各种类型字节数据的接收

当需要忽略Response中的字节时使用HO位,此时模块会等待下一次的Break Pulse,ENI位可以使用软件设置,Slave模式下也可以由硬件设置(在Sync字节接收之后),以便在RXFIFO中传输Header的ID字节

36.3.7.5.错误恢复

本小节描述了模块在LIN帧接收/发送过程中检测到错误时的行为

数据接收相关的错误

如果出现接收错误,接收方会将状态设置为Wait For Break,同时触发一次中断,错误类型如下:

-

ID Parity error- ID校验错误 -

Checksum error- 校验和错误 -

Timeout error- 超时错误 -

Framing error- 帧错误 -

Baud Rate error- 波特率错误

数据发送相关的错误

冲突错误,如果开启冲突检测位FRAMECON.CEN,当前帧会被舍弃并且发送方会进入IDLE状态

36.3.7.6.睡眠和唤醒

模块可以生成250us~5ms的Wake Up电平,当Wake Up低电平持续时间超过150us时会唤醒模块,此时,接收到Wake Up的Master可以轮询Slave节点,Master节点可以发送Break Pulse/Header、或者发送/接收Response数据,被唤醒的Slave应该能够在最大100ms的Wake Up时间后接收到LIN Header,发出Wake Up信号的Slave希望在Wake Up结束的150ms~250ms内接收到Header,如果时间结束了还没收到Header,则Slave会再次发送Wake Up信号

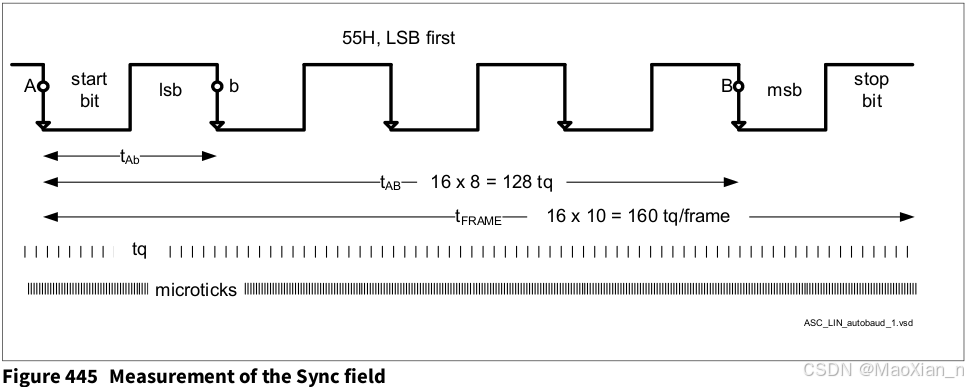

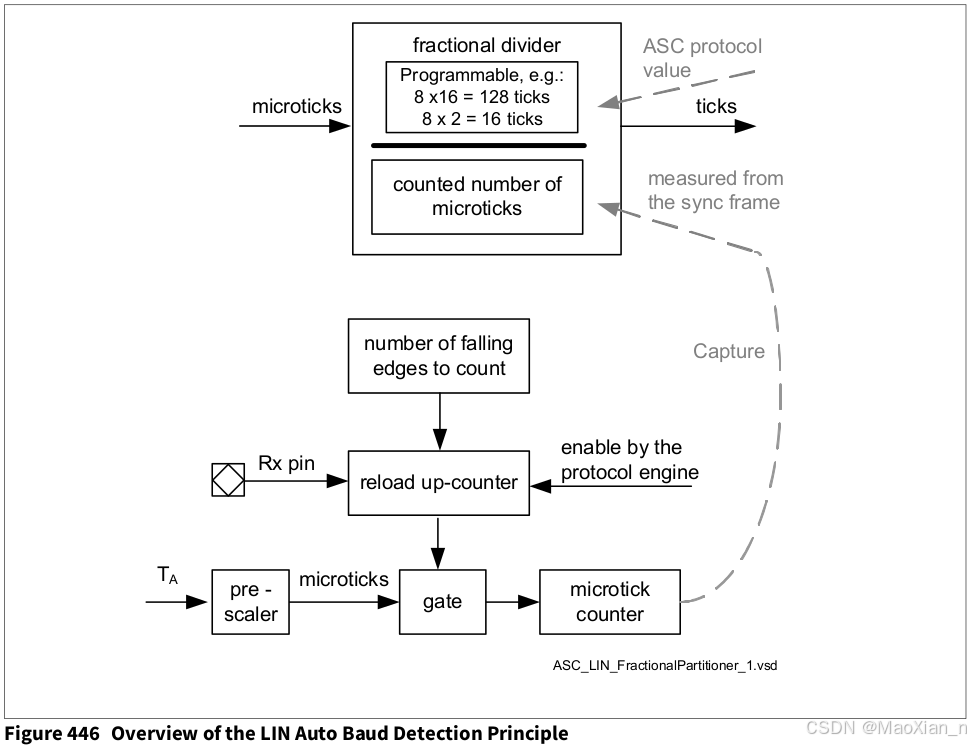

36.3.8.自动波特率检测

Slave模式下,接收Header中的Sync字节时,自动波特率检测处于激活状态,其衡量Sync字节55H中两个下降沿之间的最长间隔时间,该测量值用于分数分频器的分母及自动波特率生成

下面几个寄存器位用于监测自动波特率检测:

-

BRD.MEASURED-Sync字节第1个到第5下降沿的间隔时间 -

BRD.UPPERLIMIT- 如果自动波特率检测获得的值比标准波特率低14%,即测量时间大于UPPERLIMIT,则会产生报错并在该位使能时产生中断 -

BRD.LOWERLIMIT- 自动波特率检测获得的值比标准波特率高14%(测量时间大于UPPERLIMIT),则会产生报错并在该位使能时产生中断

自动波特率相关操作

BRD.UPPERLIMIT定义了多个MicroTicks内传输8-bit的数据允许的最大时间间隔,因此也确定了所能允许的最小波特率,为应对自动波特率低于标准值14%的情况,UPPERLIMIT定义值要比标准比特率高16%(BaudRate = 1/BitTime)

BRD.LOWERLIMIT定义了多个MicroTicks内传输8-bit数据的最小耗时,因此也确定了最大允许波特率,为应对自动波特率高于标准值14%的情况,要在LOWERLIMIT中定义比标准值低12%的值(BaudRate = 1/BitTime)

如果使能自动波特率检测,则分数分频器的分子为8x(BITCON.OVERSAMPLING+1),同时BRG.NUMERATOR中定义的值将被忽略,对于16倍的标准LIN协议超采样率(BITCON.OVERSAMPLING=15),所使用的分子为128并且忽略BRG.NUMERATOR中定义的值,BRG.NUMERATOR的值建议为128或者8x(OVERSAMPLING+1)

BRG.DENOMINATOR定义了分数分频器的分母,其初始值为LIN协议标准值,同时可由软件修改,在模块操作的过程中BRD.MEASURED中的值会自动读取至分数分频器的分母(只要其中的值在规定的范围内)

注意:为了保证分数分频器的工作行为正确,必须使用正确的分子(如8x(OVERSAMPLING+1)要小于等于BRD.MEASURED中定义的分母值),硬件不会检查这些值

自动波特率检测计算Sync字节中第1个下降沿到第5个下降沿的间隔时间,并将该值作为分母,LIN协议波特率的范围为2400~19200(期望时间为19.2 KBaud,8*52.1us = 416.8us),期望分母为TA = 10ns(417us/10ns = 41700)

分子计算方式为8*16=128(16倍超采样率),同时忽略BRG.NUMERATOR

36.3.9.冲突检测

LIN和SPI半双工模式中,冲突检测可以监测传输/接收字节的一致性

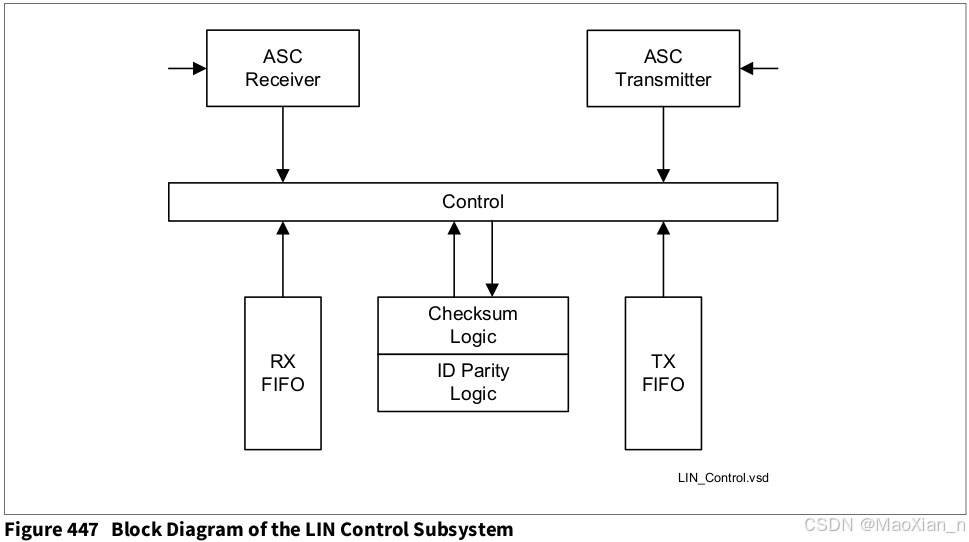

36.3.10.LIN协议控制器

LIN协议控制器连接发送/接收方、Rx/Tx FIFO、校验逻辑和看门狗,控制器会仔细处理Sync字节并自动处理校验和

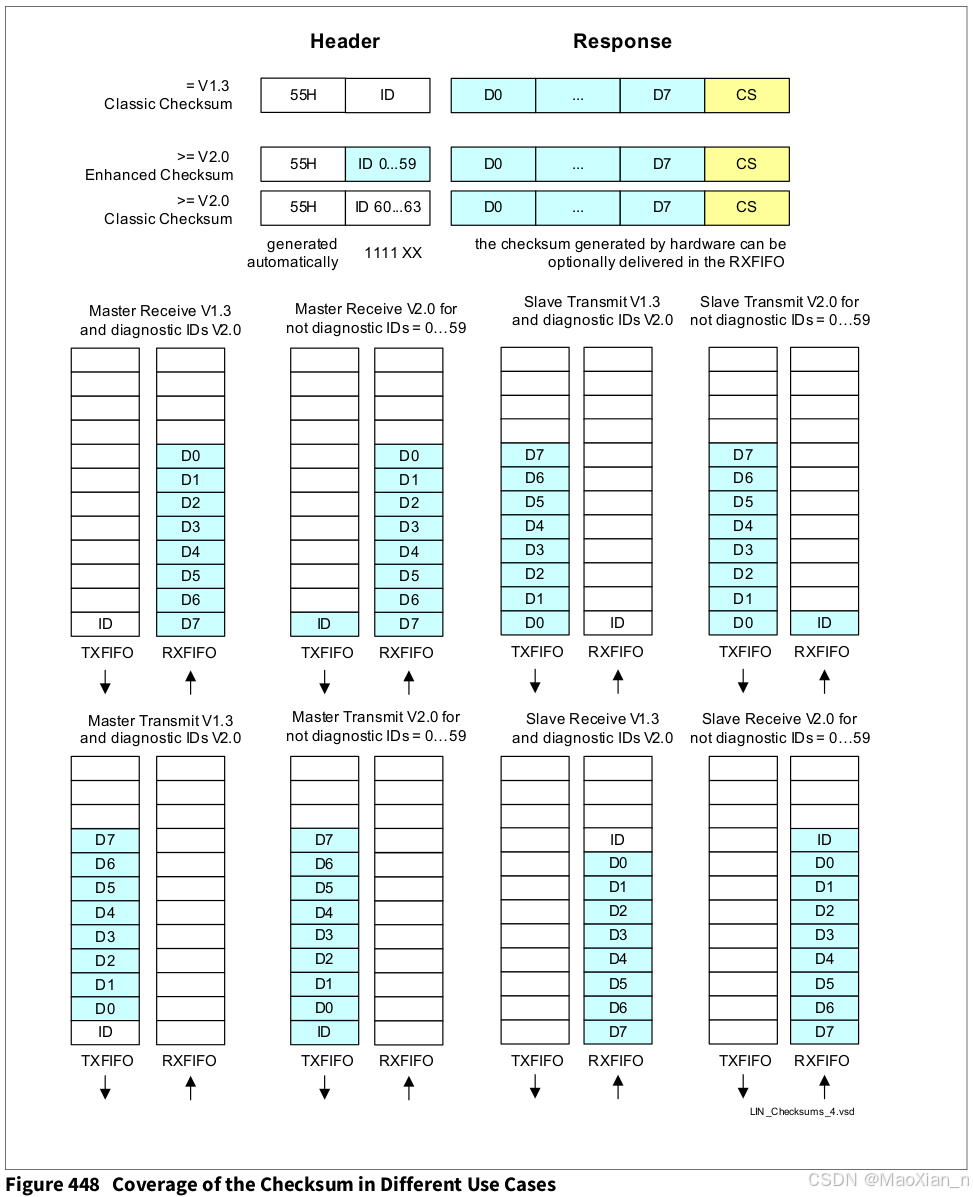

硬件校验和检查可以使能或禁用,通过软件可以设置(DATCON.CSM)使用传统校验和或增强型校验和,如下图所示,ID0~ID59使用增强型校验和而ID60~ID63使用传统校验和

同时,ID奇偶校验位由Master生成并由Slave进行检查,Slave如果检查到奇偶校验错误则会产生错误中断

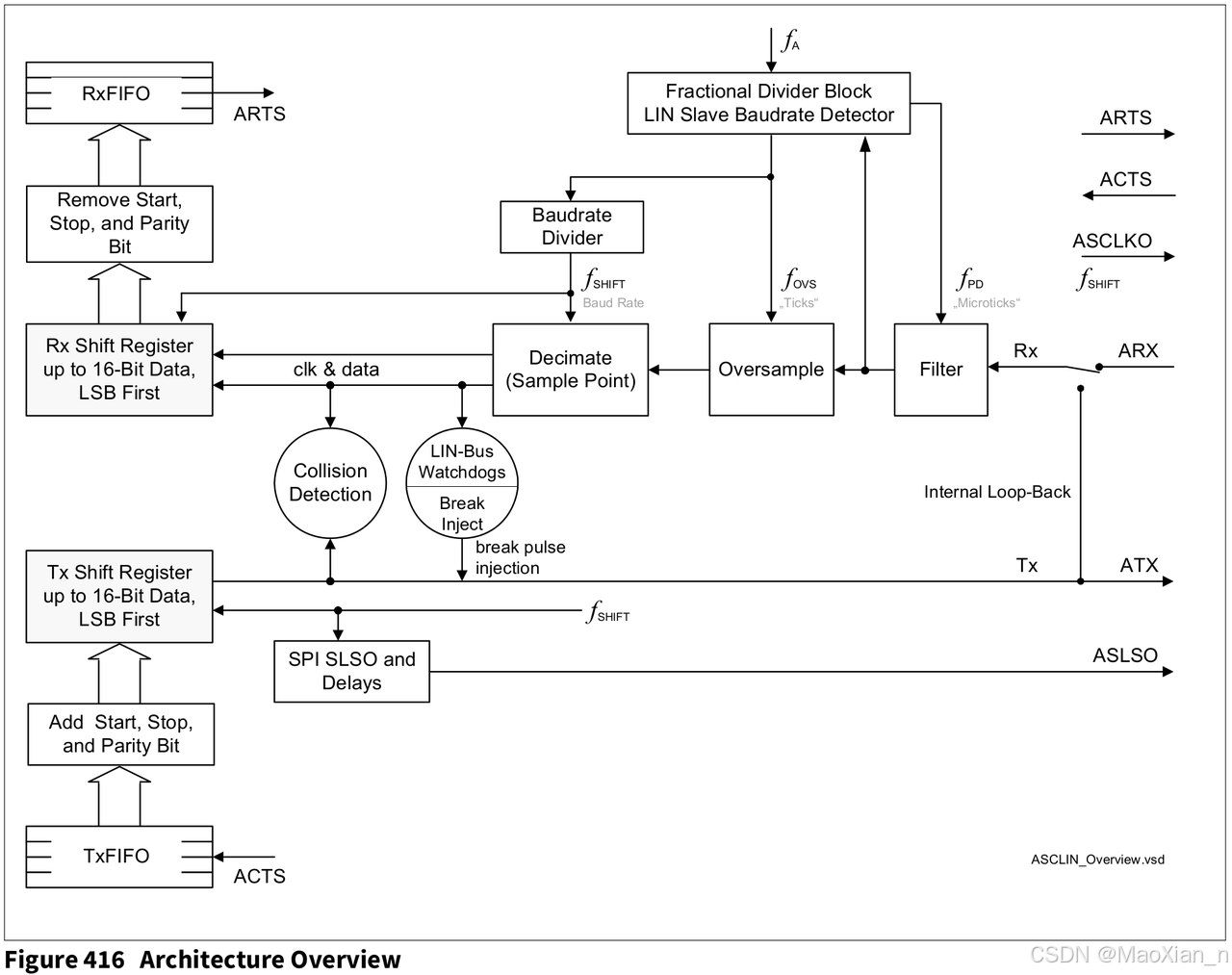

36.3.11.中断

ASCLIN模块会产生三种中断:

-

TX- 传输中断-

指示

TxFIFO Level事件

-

-

RX- 接收中断-

指示

RxFIFO Level事件

-

-

EX- 错误中断-

指示所有错误(

FLAGS.PE、FE、CE、RFO、RFU、TFO) -

其他额外事件(

FLAGS.FED、RED)

-

LIN事件包括了接收/发送Header与Response,其中断也被归纳为如下三种:

-

TX-

Master发送Header完成(FLAGS.TH) -

发送

Response完成(FLAGS.TR)

-

-

RX-

Slave接收Header完成(FLAGS.RH) -

接收

Response完成(FLAGS.RR)

-

-

EX-

LIN协议(FLAGS.BD、TC) -

LIN错误事件(FLAGS.HT、RT、LP、LA、LC)

-

为了确定LIN中断源,需要轮询FLAGS寄存器

触发DMA

中断信号也用于触发DMA,中断信号会接入中断路由模块,因此,可以选择将中断信号发送给CPU或者DMA,DMA没有独立的触发信号

服务请求节点和事件节点的关系

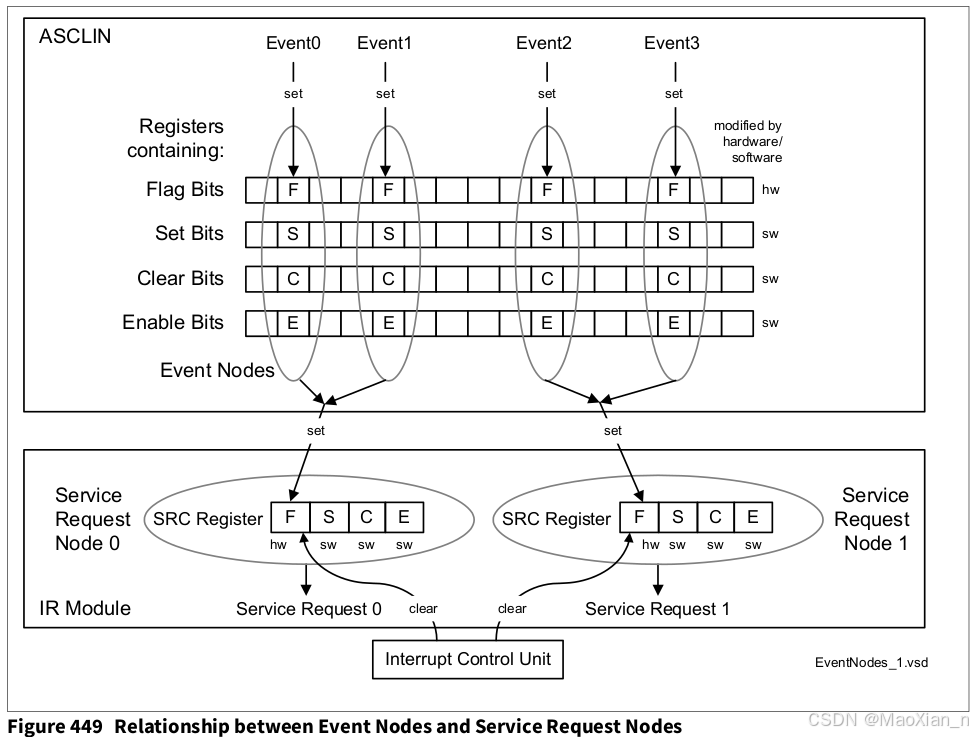

有几个事件专门用于Service Request(中断),每个服务请求(中断)包含一个服务请求控制寄存器SRC(Service Request Control),该寄存器中有对应的标志位、标识设置、清除及使能位,SRC寄存器在中断路由(Interrupt Router,IR)模块中,SRC寄存器中的服务请求标志位由硬件设置,如果同时设置了使能位,那么当中断服务开始执行时,硬件会清除该标志位

一个中断节点可能被多个事件触发,每个事件也包含一个标志位及相关的设置/清除和使能位,这几位分别在四个寄存器中:FLAGS、FLAGSSET、FLAGSCLEAR、FLAGSENABLE,这四个标志位共同构成一个事件并形成一个虚拟的事件节点,如下图所示:

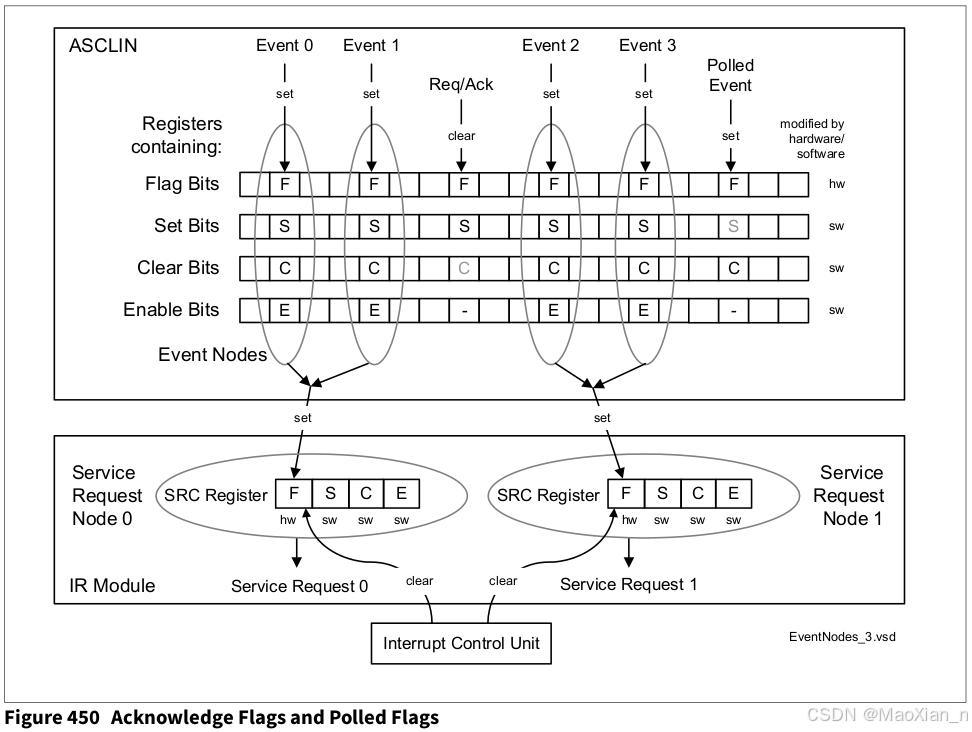

事件标志位由硬件设置并在使能时触发一次中断,标志位必须由软件在对应的中断服务路由中清除(查找标志位对应的中断源),在测试时也可以使用软件设置中断标志位

一些标志位不会产生中断并且没有对应的使能位,这些标志位用于发送请求或者提供给软件用作轮询,如下图所示:

软件清空请求/应答标志位会被忽略(如FLAGS.TRRQ、THRQ、TWRQ)

ASCLIN模块中没有专门用于轮询的标志位(禁用标志位对应的使能位可以将所有标志位都设置为仅供轮询使用,例如通过使用FLAGS.FED、RED标志位实现IDLE/STUCK监测)

36.3.12.数字滤波器

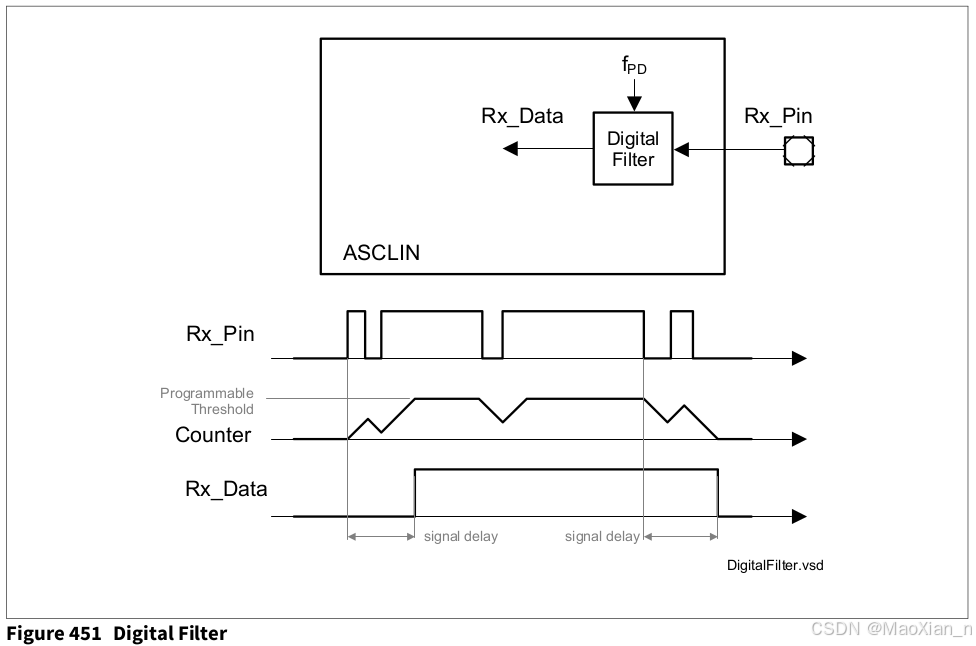

数字毛刺滤波器按照设定的阈值计算上升/下降沿以消除输入信号中的毛刺,但是滤波器会导致输入延迟,延迟大小取决于数字滤波器的采样频率fPD和IOCR.DEPTH中定义的阈值,不应该在SPI模式中使用滤波器

36.3.13.挂起、睡眠和下电行为

ASCLIN模块一般传输8-bit宽度的数据(不超过16-bit),所使用的波特率也比较低(一般为几KBaud),如果在数据传输的中途将模块挂起或关闭,会导致接收方接收到错误的数据,LIN模式中这样做会导致接收方产生超时错误,如果ASCLIN模块接收到关闭时钟信号的请求,则会立即禁用DMA传输请求,因此关闭模块时需要保证当前没有正在传输的数据帧并且Rx/Tx FIFO为空

36.3.13.1.OCDS挂起

OCDS(On-Chip Debug System) Soft Suspend会在当前事务结束后将模块挂起,在ASC和SPI模式中为当前帧的结束位置,在LIN模式中为当前LIN帧(Response、Header Timeout、Response Timeout)的结束位置

调试时可以使用OCDS Hard Suspend,会立即停止ASCLIN模块的所有活动,同时立即停止fCLC内核时钟,但是同步时钟fA会保持开启

注意:读取/写入操作会导致内核时钟fCLC短暂开启,在Hard Suspend状态下访问寄存器会导致意想不到的副作用(比如信号会变成持续激活的状态),同时这也会影响到其他模块,而且仅仅对内核进行重启无法将整个系统恢复正常

36.3.13.2.睡眠模式

进入睡眠模式表示ASCLIN模块已经完成了所有事务并且RX/TXFIFO为空,软件应该仅在该情况下发送休眠请求

模块响应睡眠请求的方式和禁用请求一致

36.3.13.3.禁用请求(下电)

进入禁用模式表示ASCLIN模块已经完成了所有事务并且RX/TXFIFO为空,软件应该仅在该情况下发送禁用请求,只要该请求是单向的(必须重新初始化才能使用该模块)就不会产生问题,此时,模块会关闭所有输出、停止输入响应,内部状态变为初始化状态,寄存器中的值不会修改,然后模块响应请求,关闭所有时钟

36.3.14.复位行为

Reset触发源有两个:BPI(Bus Peripheral Interface),寄存器的Reset位KRSTx0.RST和KRSTx1.RST

KRSTx.RST只对Kernel执行Reset,不会重置BPI相关寄存器

BPI复位会执行应用程序复位,除了OCS其他所有寄存器都会被复位,同时所有输出口都会接收到复位值

OCS寄存器需要使用Debug Reset进行复位

36.3.15.具体实现

本小节介绍ASCLIN模块的特定配置及其与其他模块的联系,ASCLIN模块的具体数量参见附录

36.3.15.1.BPI_FPI模块寄存器

36.3.15.1.1.系统寄存器

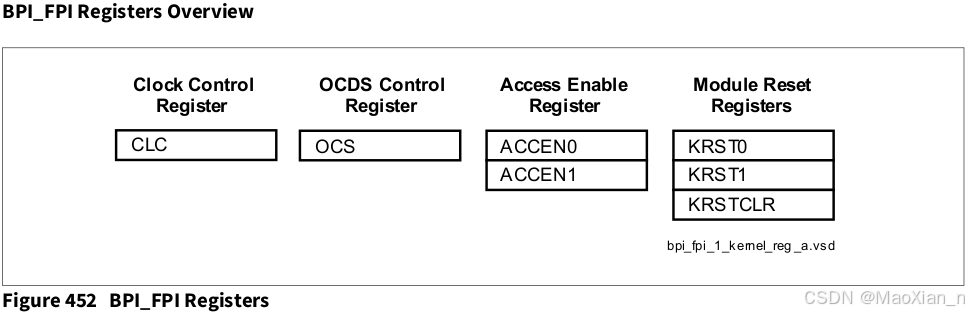

BPI_FPI模块相关寄存器如下图所示(对应一个内核配置):

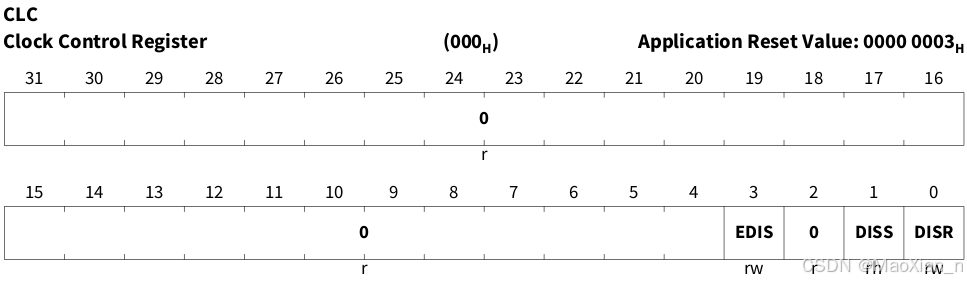

时钟控制寄存器

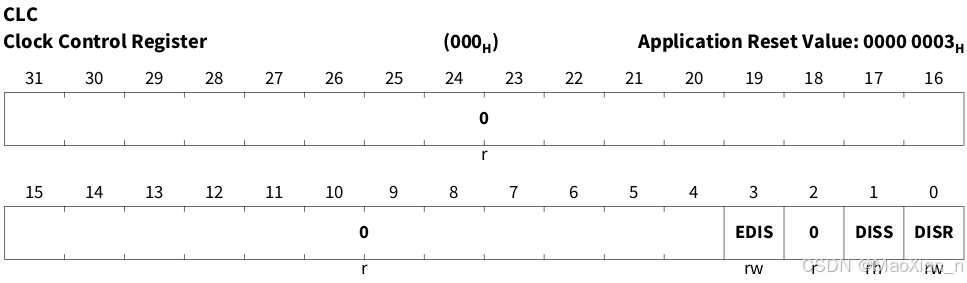

时钟控制寄存器CLC

-

DISR:Module Disable Request Bit,使能/禁用模块 -

DISS:Module Disable Status Bit,指示当前模块状态(使能 or 禁用) -

EDIS:Sleep Mode Enable Control,控制模块的睡眠模式,控制模块响应或忽略睡眠信号-

0:使能 -

1:禁用

-

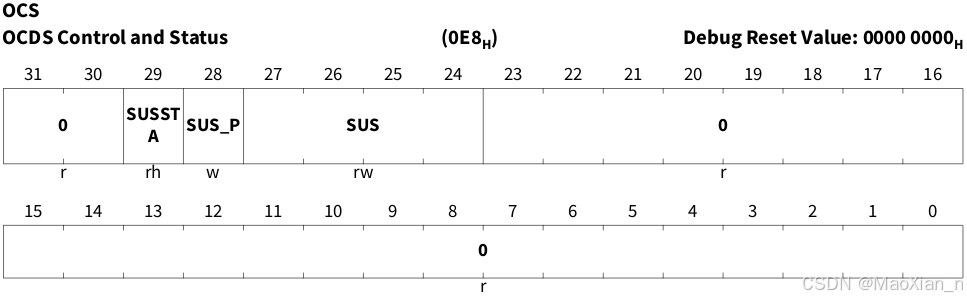

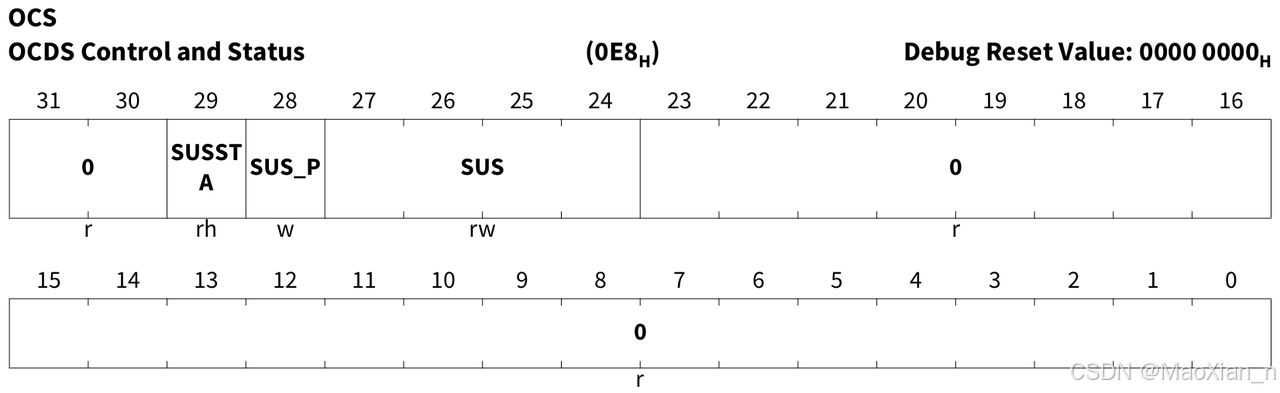

OCDS控制和状态

OCDS控制和状态寄存器OCS,控制模块在Suspend模式下的行为(调试时使用),使用Debug Reset可以清空OCS寄存器,只有当OCDS使能时才能读写OCS寄存器,如果OCDS为禁用状态则OCS寄存器中的值不会改变,同时Suspend控制也会失效

-

SUS:OCDS Suspend Control,是否响应OCDS发送的发送的挂起信号-

0:忽略信号 -

1:硬件挂起,立即关闭时钟信号 -

2:软件挂起

-

-

SUS_P:SUS Write Protection,写入保护,仅当SUS_P为1时才可以修改SUS,读取该位返回0 -

SUSSTA:Suspend State,指示模块是否为挂起状态-

0:模块未挂起 -

1:模块已经挂起

-

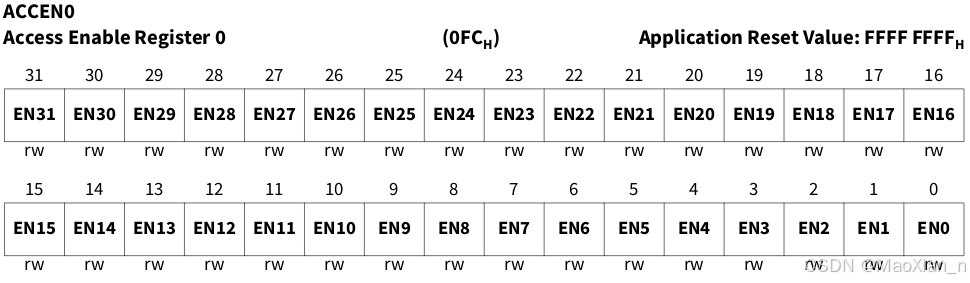

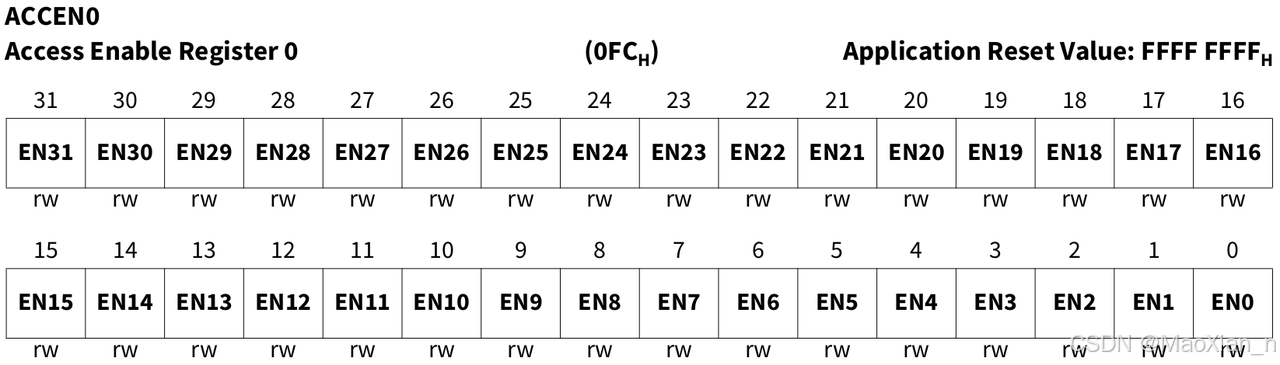

权限使能寄存器0

控制片上总线(TAG ID 000000B~011111B)事务的写入许可,BPI_FPI允许6-bit的TAG ID,ACCEN0寄存器为每一个TAG ID提供了一个使能位

映射关系:EN0 --> 000000B,EN1 --> 000001B,......,EN31 --> 011111B

-

ENn (n=0-31):Access Enable for Master TAG ID n,控制TAG ID n的写入允许-

0:写入权限不会被执行 -

1:允许写入权限

-

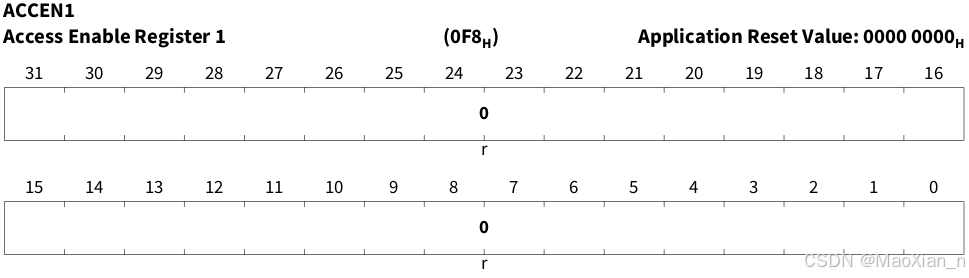

权限使能寄存器1

控制片上总线(TAG ID 100000B~111111B)事务的写入许可,BPI_FPI允许6-bit的TAG ID,ACCEN0寄存器为每一个TAG ID提供了一个使能位

映射关系:EN0 --> 100000B,EN1 --> 100001B,......,EN31 --> 111111B

-

该寄存器未使用

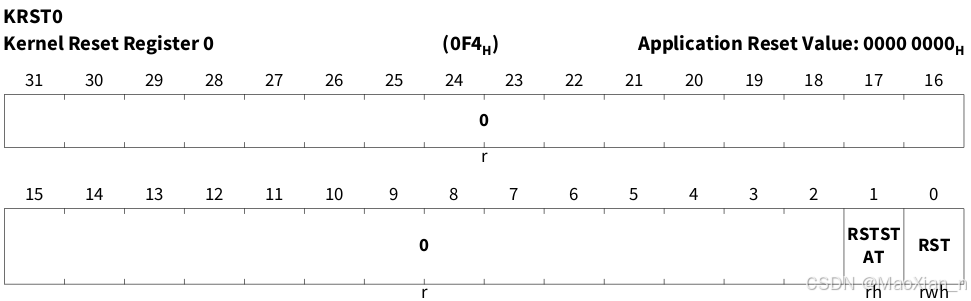

内核复位寄存器0

用于内核相关模块复位,Debug Reset相关的内核重置寄存器不受影响,复位内核模块时需要向RST位写1,当内核模块复位序列完成后,BPI总线会重置RST位,该寄存器包含一个内核重置状态位,当RST标志位被BPI_FPI复位的同时会将该标志位置1,该标志位可用于检查内核是否被复位,通过向KRSTCLR.CLR写1可以将RSTSTAT标志位写0

注意:内核复位过程中(直至RSTSTAT置1),访问内核寄存器会导致错误

-

RST:Kernel Reset,内核复位请求,如果两个内核复位寄存器的RST都被设置,则执行内核复位,内核复位执行后,BPI_FPI会重置RST位-

0:没有复位请求 -

1:存在复位请求

-

-

RSTSTAT:Kernel Reset Status,指示内核模块是否已执行复位,BPI_FPI在同一时钟周期内执行内核复位后,会重置该位,可以通过向KRSTCLR寄存器的CLR位写1清除该位-

0:未执行过内核复位 -

1:内核复位已执行

-

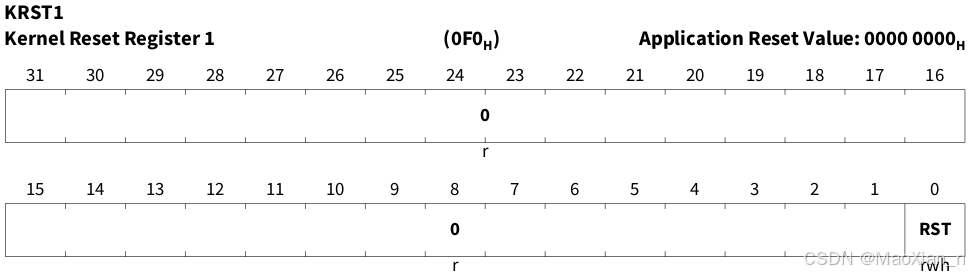

内核复位寄存器1

用于内核相关模块复位,Debug Reset相关的内核重置寄存器不受影响,复位内核模块时需要向RST位写1,当内核模块复位序列完成后,BPI总线会重置RST位

-

RST:Kernel Reset,内核复位请求,如果两个内核复位寄存器的RST都被设置,则执行内核复位,内核复位执行后,BPI_FPI会重置RST位-

0:没有复位请求 -

1:存在复位请求

-

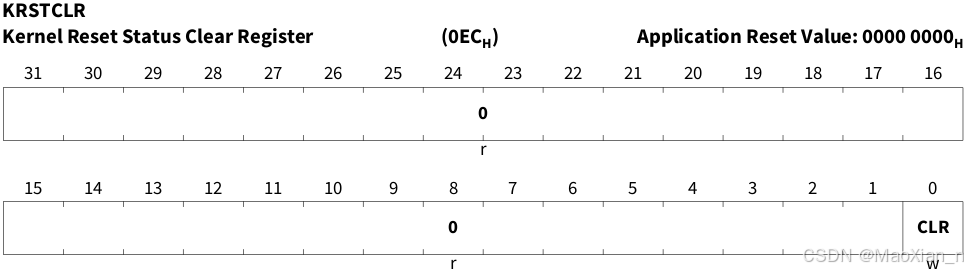

内核复位状态清除寄存器

用于清除内核复位状态位KRST0.RSTSTAT

-

CLR:Kernel Reset Status Clear,内核复位状态清除,写1将KRST0.RSTSTAT重置-

0:无操作 -

1:清除内核复位状态KRST0.RSTSTAT

-

36.3.16.片上连接

本小节展示了ASCLINx的片上连接

引脚连接

引脚定义和连接章节介绍了ASCLIN模块的引脚和连接方式

没有对应引脚的信号如下所示:

-

The unconnected ARX signals in the lower half range (RXA to RXD) are connected to (active) low level, “0”

-

The unconnected ARX signals in the upper half range (RXE to RXH) are connected to (inactive) high level, “1”

-

The unconnected ACTS signals are connected to low level “0”, which is after reset the inactive level (but disabled via IOCR.CTSEN bit field, meaning don’t care)

自连接

每个ASCLIN实例都有如下连接:ARTS --> ACTSD

该连接方式在SPI模式(频繁的并行接收/发送数据)下非常有用,如果通过IOCR.CTS选择使用这种连接方式,则TXFIFO只会在RXFIFO中有空闲单元时才会发送数据,如果没有选择这种连接方式,则TXFIFO只会在软件清空RXFIFO后才会自动开始传输

36.3.17.CAN支持

ASC Tx/Rx和CAN Tx/Rx会相互覆盖,详情参考端口和引脚章节,可擦除Flash的设备可以由CAN引脚通过ASC加载,详情参考Boot章节

36.4.寄存器

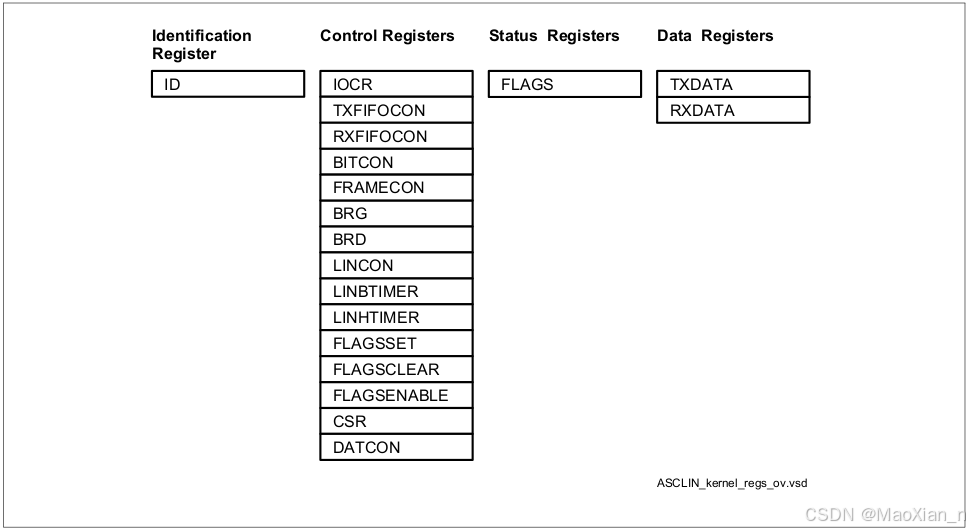

本小节描述了ASCLIN模块相关的内核寄存器,其他模块引用这些寄存器时会使用具体的实例,并加上对应的前缀ASCLIN0_(对应ASCLIN0),ASCLIN地址空间中的所有寄存器都会在程序复位时一起复位

内核寄存器概览

注意:寄存器绝对地址 = 基址 + 偏移

36.4.1.内核寄存器

0x00 - CLC

Clock Control Register - 时钟控制寄存器

模块接入CLC时钟控制接口后,CLC可以控制模块的时钟输入信号、睡眠模式、使能/禁用

-

DISR:Module Disable Request Bit,使能/禁用模块 -

DISS:Module Disable Status Bit,指示当前模块状态(使能 or 禁用) -

EDIS:Sleep Mode Enable Control,控制模块的睡眠模式,控制模块响应或忽略睡眠信号-

0:使能 -

1:禁用

-

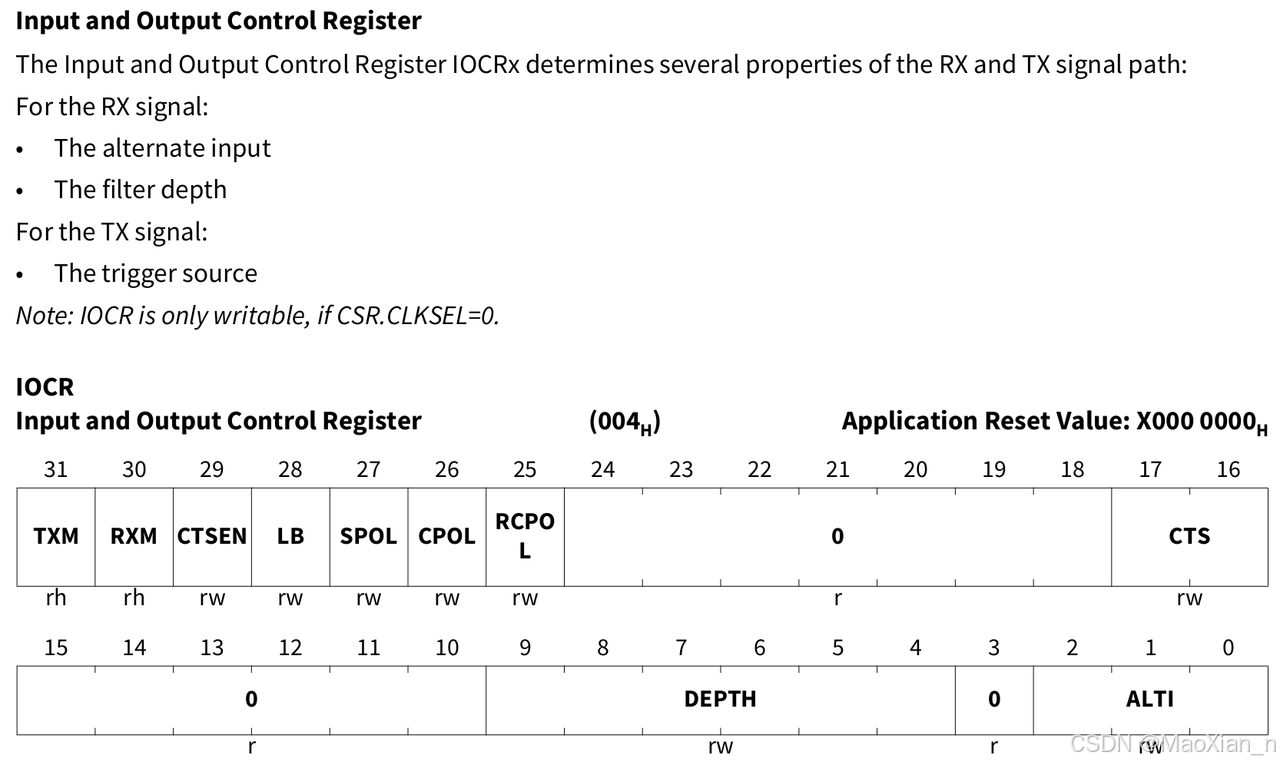

0x04 - IOCR

Input and Output Control Register - 输入输出控制寄存器

控制输入Rx的备用输入通道和滤波深度,发送Tx的触发源

注意:IOCR仅当CSR.CLKSEL=0时可写

-

ALTI:Alternate Input Select,备用输入选择,Rx的信号源(输入通道选择)-

000:输入通道A -

001:输入通道B -

010:输入通道C -

011:输入通道D -

100:输入通道E -

101:输入通道F -

110:输入通道G -

111:输入通道H

-

-

DEPTH:Digital Glitch Filter Depth,输入信号毛刺滤波深度,提高抑制强度会增加输入延迟-

00:关闭,默认值 -

01:1 -

...

-

3F:63

-

-

CTS:CTS Select,CTS输入引脚选择-

00:ACTSA -

01:ACTSB -

10:ACTSC -

11:ACTSD

-

-

RCPOL:RTS CTS Polarity,RTS/CTS信号为高/低电平,该电平表示准备好发送/清除-

0:高电平 -

1:低电平

-

-

CPOL:Clock Polarity in Synchronous Mode,时钟信号IDLE模式的高/低电平,默认无信号传输时为低电平-

0:时钟信号的IDLE为低电平 -

1:时钟信号的IDLE为高电平

-

-

SPOL:Slave Polarity in Synchronous Mode,SLSO信号IDLE模式的高/低电平,默认无信号传输为低电平-

0:SLSO信号的IDLE为低电平 -

1:SLSO信号的IDLE为高电平

-

-

LB:Loop Back Mode,在ASC和SPI模式下,使能该位可以让模块在没有外部连接的情况下运行和测试,LIN模式下不应该使用该方式-

0:禁用 -

1:使能

-

-

CTSEN:Input Signal CTS Enable,控制模块是否响应外部CTS信号,如果禁用CTS信号视为永久激活状态-

0:禁用 -

1:使能

-

-

RXM:Receive Monitor,监视接收信号的当前状态-

0:当前信号为低 -

1:当前信号为高

-

-

TXM:Transmit Monitor,监视发送信号的当前状态-

0:当前信号为低 -

1:当前信号为高

-

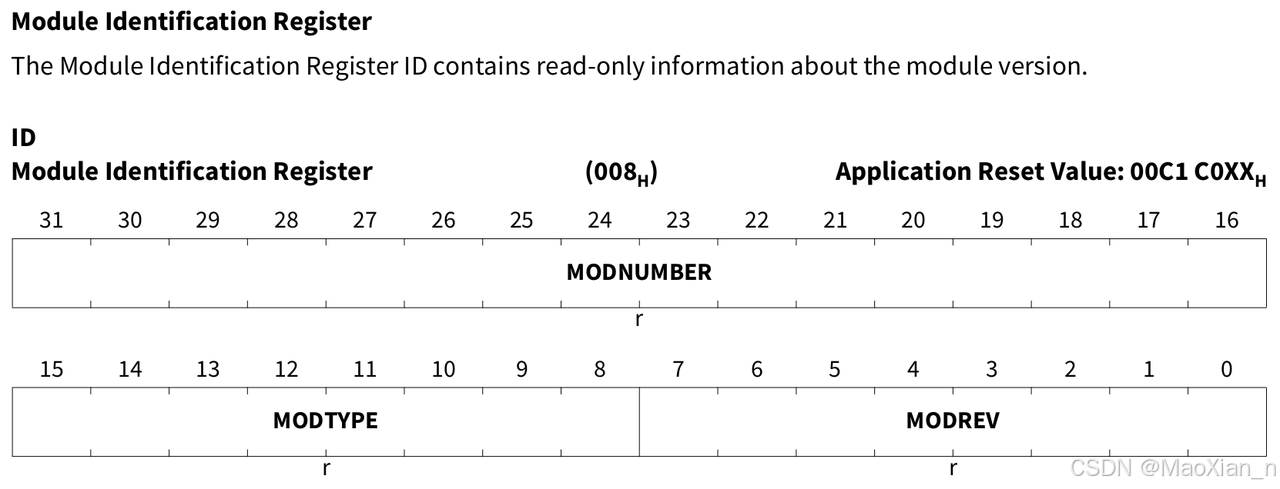

0x08 - ID

Module Identification Register - 模块信息寄存器

存储当前模块的版本信息(只读)

-

MODREV:Module Revision Number,版本号,从01开始(第一个版本) -

MODTYPE:Module Type,模块类型,该位为C0,定义模块位32-bit -

MODNUMBER:Module Number Value,和MODTYPE一起使用确定模块的唯一编号

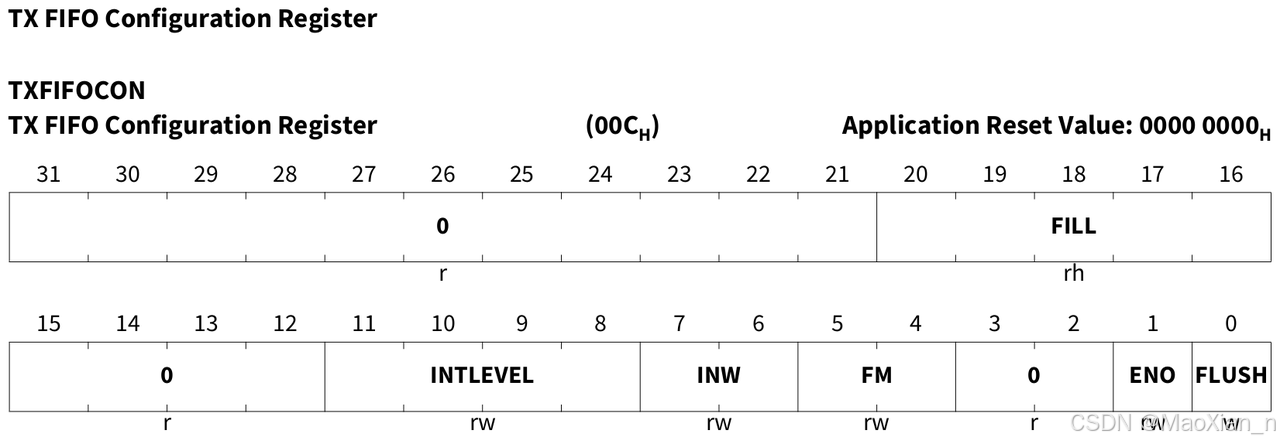

0x0C - TXFIFOCON

TX FIFO Configuration Register - FIFO发送配置寄存器

-

FLUSH:Flush the Transmit FIFO,刷新TxFIFO,置1清空TxFIFO,向其写0无效-

0:无效 -

1:清空TxFIFO

-

-

ENO:Transmit FIFO Outlet Enable,使能Transmit,SPI/ASC模式下使能该位后,数据准备好后立即发送,LIN模式下使能该位,只有在获取到控制信号后才将数据发送至移位寄存器-

0:禁用 -

1:使能

-

-

FM:TXFIFO Mode,选择逐位发送、多位发送、按包发送-

00:Combined Move模式 -

01:Single Move模式 -

10:Batch Move模式 -

11:保留

-

-

INW:Transmit FIFO Inlet Width,每次FPI总线写入时,TxFIFO每次写入的字节数(如每次4字节)-

00:0 -

01:1 -

10:2 -

11:4

-

-

INTLEVEL:FIFO Interrupt Level,TxFIFO每次发送数据后检查TXFIFOCON.FILL,当TXFIFOCON.FILL小于等于TXFIFOCON.INTLEVEL时触发中断,该方式对应Combined Move模式-

0:0 -

...

-

F:15

-

-

FILL:FIFO Filling Level,只读,保存当前TxFIFO的Filling Level-

00:0 -

...

-

10:16 -

11:保留,未使用 -

...

-

1F:保留,未使用

-

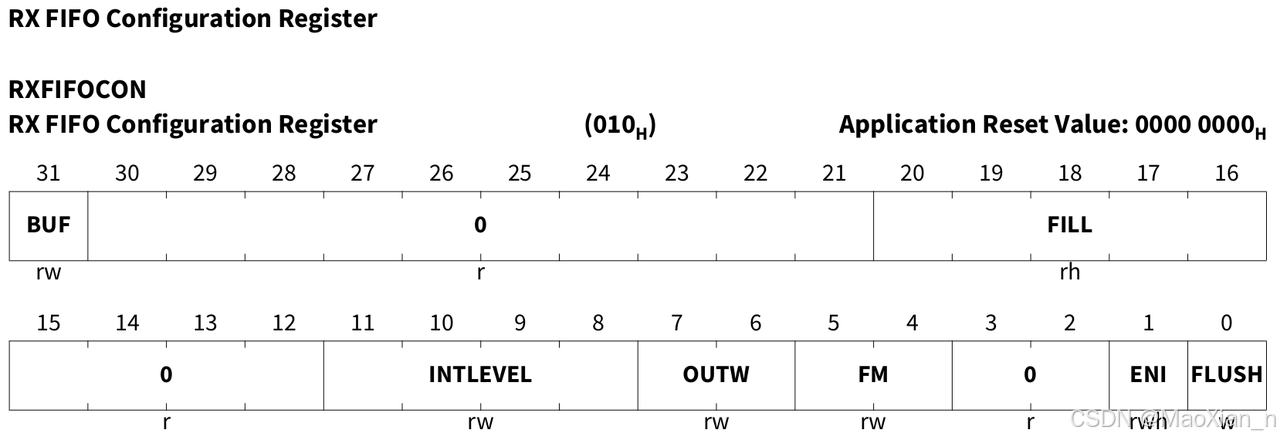

0x10 - RXFIFOCON

RX FIFO Configuration Register - FIFO接收控制寄存器

-

FLUSH:Flush the Receive FIFO,刷新RxFIFO,置1清空RxFIFO,向其写0无效-

0:无效 -

1:清空RxFIFO

-

-

ENI:Receive FIFO Inlet Enable,使能Receive并从移位寄存器中开始接收数据,在LIN Slave模式下,硬件在正确的接收到同步域后设置该位,软件可以在接收到外部ID信号后清除该位,从而阻止响应后续数据 -

FM:RXFIFO Mode,选择逐位接收、多位接收、按包接收-

00:Combined Move模式 -

01:Single Move模式 -

10:Batch Move模式 -

11:保留

-

-

OUTW:Receive FIFO Outlet Width,每次FPI总线读取数据时,RxFIFO每次读取的字节数(如每次读取4字节)-

00:0 -

01:1 -

10:2 -

11:4

-

-

INTLEVEL:FIFO Interrupt Level,RxFIFO每次读取数据后,检查Filling Level,大于等于该值时触发中断,这种方式对应Combined Move模式-

0:1 -

...

-

F:16

-

-

FILL:FIFO Filling Level,只读,保存当前RxFIFO的Filling Level-

00:0 -

...

-

10:16 -

11:保留 -

...

-

1F:保留

-

-

BUF:Receive Buffer Mode,如果该位为0则RxFIFO为普通模式,该位置1后,每次接收新数据时会直接覆盖原来的数据,其行为为32-bit的Single-Stage缓冲区,低位存放有效数据,高位用0填充-

0:RxFIFO -

1:Single-Stage Rx Buffer

-

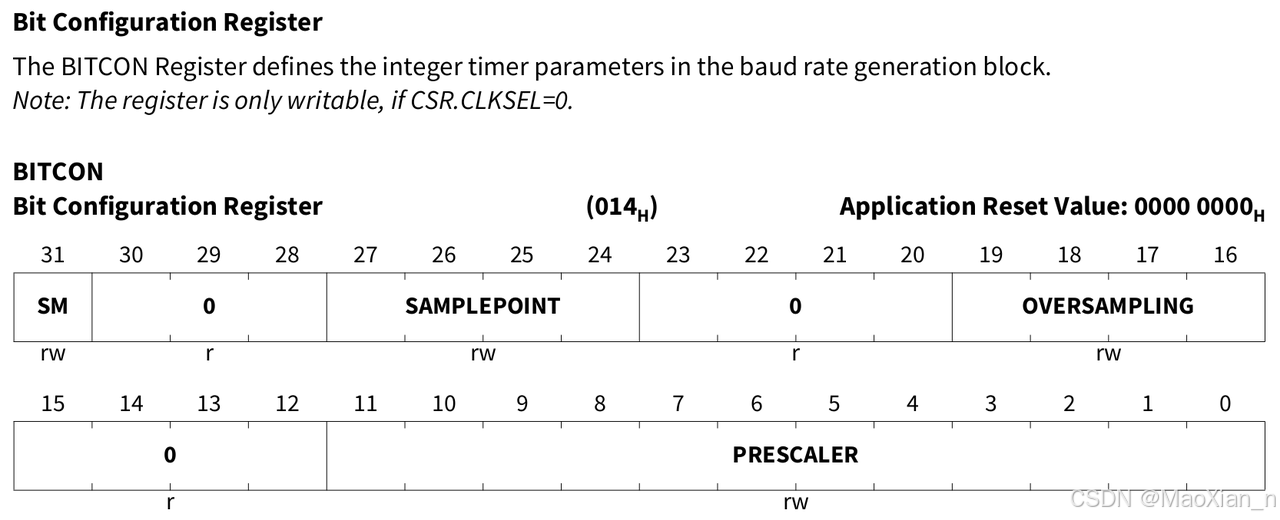

0x14 - BITCON

Bit Configuration Register - 位配置寄存器

配置采样信号

注意:仅当CSR.CLKSEL=0该寄存器可写

-

PRESCALER:Prescaling of the Fractional Divider,预分频系数,取值范围0~4095(分母1~4095),用于输入数字滤波 -

OVERSAMPLING:Oversampling Factor,过采样,取值范围4~16-

0:1(非法值) -

1:2(非法值) -

2:3(非法值) -

...

-

3:4 -

F:16

-

-

SAMPLEPOINT:Sample Point Position,采样点位置,取值范围0~15,例如,需要在第7、8、9个信号点处采样,则该位配置为9,在SPI模式下,该位+1以ticks为单位定义第一个SCLK半个周期的长度,该值禁止大于等于OVERSAMPLING-

0:0(禁止使用) -

1:1 -

...

-

F:15

-

-

SM:Sample Mode,采样模式,对每一位采样几次-

0:1 -

1:3

-

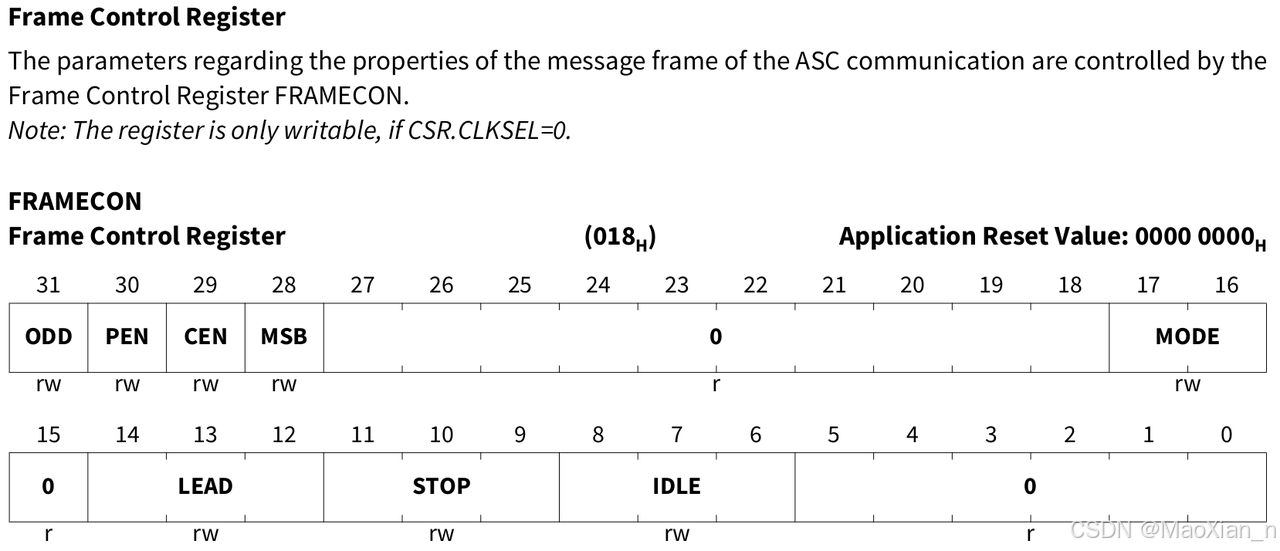

0x18 - FRAMECON

Frame Control Register - 帧控制寄存器

ASC通信数据帧配置

注意:仅当CSR.CLKSEL=0该寄存器可写

-

IDLE:Duration of the IDLE delay,IDLE时间,如果TXFIFO中存在多个待发送的字符,则该值为字符发送的间隔Pause,SPI模式下该值为数据帧的间隔,ASC和LIN模式下该值为每个字节传输的间隔Pause,报文头和应答的间隔Pause也使用IDLE描述-

注意:冲突检测和

IDLE并行运行,LIN Master模式下会导致两个字节之间的间隔延长一个bit位的时间,如果包括数字滤波器延时在内的数据往返延时长于IDLE延时,便会产生这种效应,LIN Slave模式下IDLE=0 -

000:0 -

...

-

111:7

-

-

STOP:Number of Stop Bits,停止位长度,定义ASC和LIN模式中停止位的数量,定义SPI模式中的Trailing延时,ASC模式中的标准值为1和2,LIN模式的标准值为1,SPI模式没有标准值-

000:0(ASC和LIN模式中不允许使用该值) -

001:1 -

...

-

111:7

-

-

LEAD:Duration of the Leading Delay,SPI模式为Leading延迟,ASC模式无效,LIN模式为开始同步之前的延迟-

000:0(LIN和4-Wire SPI不允许使用该值) -

001:1 -

...

-

111:7

-

-

MODE:Mode Selection,模式选择(INIT/ASC/SPI/LIN),INIT模式下所有输出为Inactive状态,此时模块不会响应输入信号,切换模式前需要先进入INIT模式,SCLK信号仅在SPI模式下为Active状态,CTS信号仅在ASC模式下为Active状态-

00:INIT -

01:ASC -

10:SPI -

11:LIN

-

-

MSB:Shift Direction,移位方向(LSB or MSB),SPI模式中定义移位寄存器的方向,ASC和LIN模式中需要置为0,奇偶校验位位于数据末尾,与移位方向无关-

0:LSB First -

1:MSB First

-

-

CEN:Collision Detection Enable,使能冲突检测-

0:禁用 -

1:使能

-

-

PEN:Parity Enable,校验位使能,ASC和SPI模式可以使用奇偶校验位,LIN模式不应该使用该位-

0:禁用 -

1:使能

-

-

ODD:Parity Type,奇/偶校验类型,所有模式均可以使用该位-

0:奇 -

1:偶

-

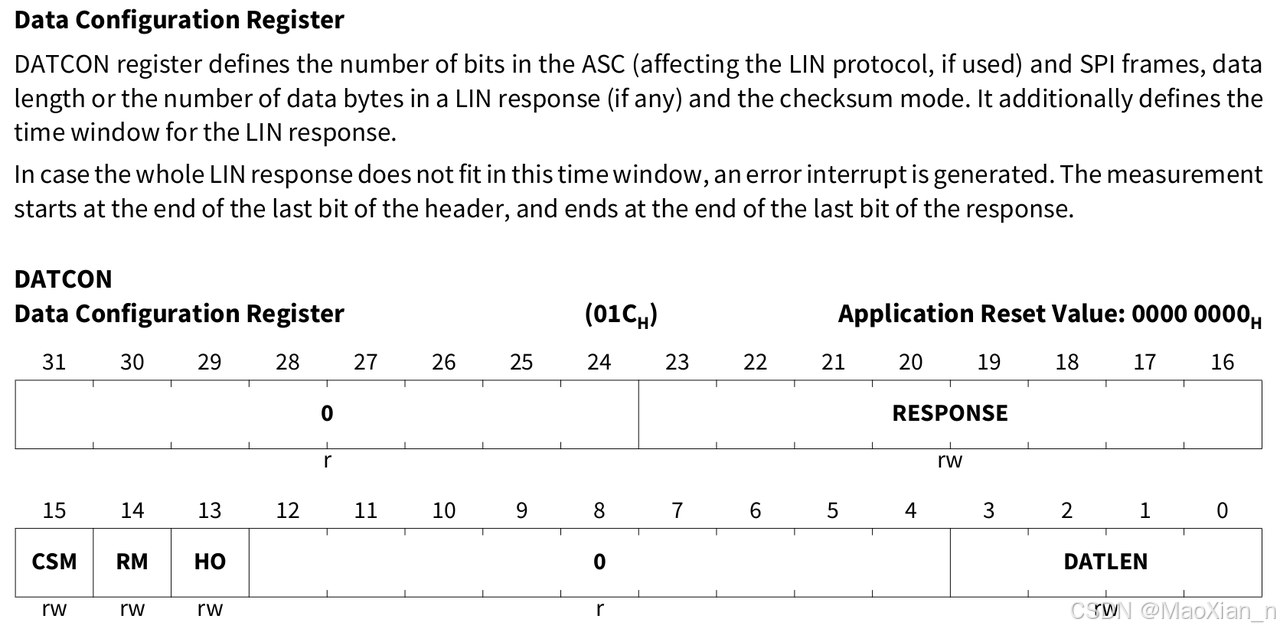

0x1C - DATCON

Data Configuration Register - 数据配置寄存器

配置ASC和SPI模式中数据帧的长度(也会影响LIN报文长度),LIN模式中应答数据的长度及检查模式,LIN模式中数据帧传输超时时间,如果LIN报文未能在规定的时间窗口内完成传输,则会触发中断,该时间窗口从报文头的最后一个bit开始,到应答的最后一个bit结束

-

DATLEN:Data Length,数据长度,定义一个字符的bit数量,ASC模式中一个字符的标准长度为7~9-bit,SPI模式中没有标准的长度,LIN模式中一个字符的标准长度为8-bit,该位定义了应答报文的字节数量-

0:1 -

...

-

F:16

-

-

HO:Header Only,设置LIN数据帧仅包含报文头还是同时包含报文头和应答数据-

0:同时包含报文头和应答报文 -

1:仅关注报文头,忽略应答报文

-

-

RM:Response Mode,LIN数据帧超时/应答超时,确定RESPONSE位定义的超时阈值为LIN应答报文还是LIN帧-

0:Frame -

1:Response

-

-

CSM:Checksum Mode,校验模式,使用经典/增强校验和-

0:经典校验和 -

1:增强校验和

-

-

RESPONSE:Response Timeout Threshold Value,应答超时时间(1~256Bit)

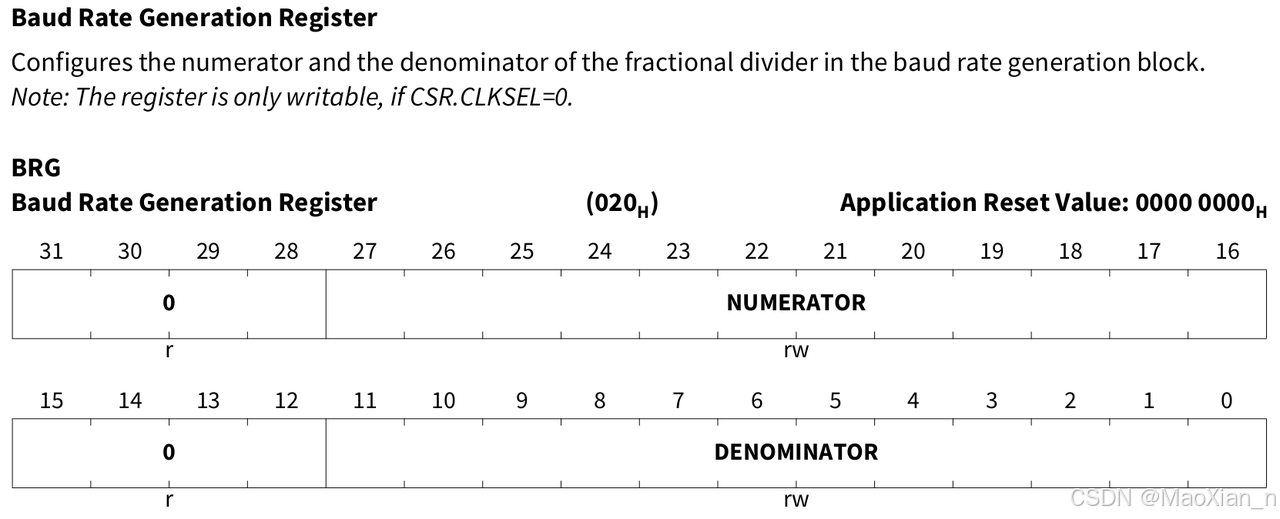

0x20 - BRG

Baud Rate Generation Register - 波特率生成寄存器

设置波特率的分子和分母(波特率 = 传输速率 / 每个数据线所需的时间)

注意:仅当CSR.CLKSEL=0时该寄存器可写

-

DENOMINATOR:Denominator,分母,由软件设置(范围0~4095),禁止将该值置为0,在ASC、SPI、LIN Master和LIN Slave模式中,如果未使用自动波特率检测,则该值定义了波特率,在LIN Slave模式中,如果使用了自动波特率检测则该值为标准值,自动波特率检测所使用的硬件值参考BRD寄存器 -

NUMERATOR:Numerator,分子,由软件设置(范围0~4095),禁止将该值置为0

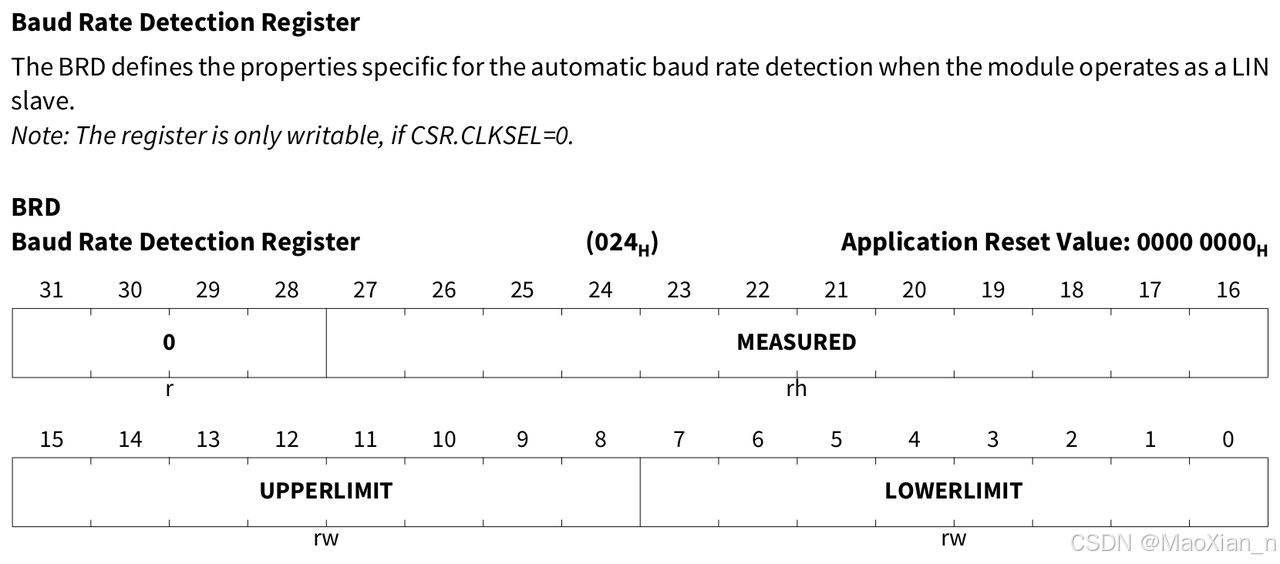

0x24 - BRD

Baud Rate Detection Register - 波特率检测寄存器

LIN模式中的自动检测波特率

注意:仅当CSR.CLKSEL=0时该寄存器可写

-

LOWERLIMIT:Lower Limit,一个时钟周期内传输8-bit数据所允许最小的时长,最低四位为1000 -

UPPERLIMIT:Upper Limit,一个时钟周期内传输8-bit数据所允许最大的时长,最低四位为1000 -

MEASURED:Measured Value of 8-bits from Sync Field,LIN模式中,一个时钟周期内传输8-bit报文头同步域的平均时长,在LIN Slave模式中,若开启了自动波特率检测,该值会自动加载至分数分频器的分母

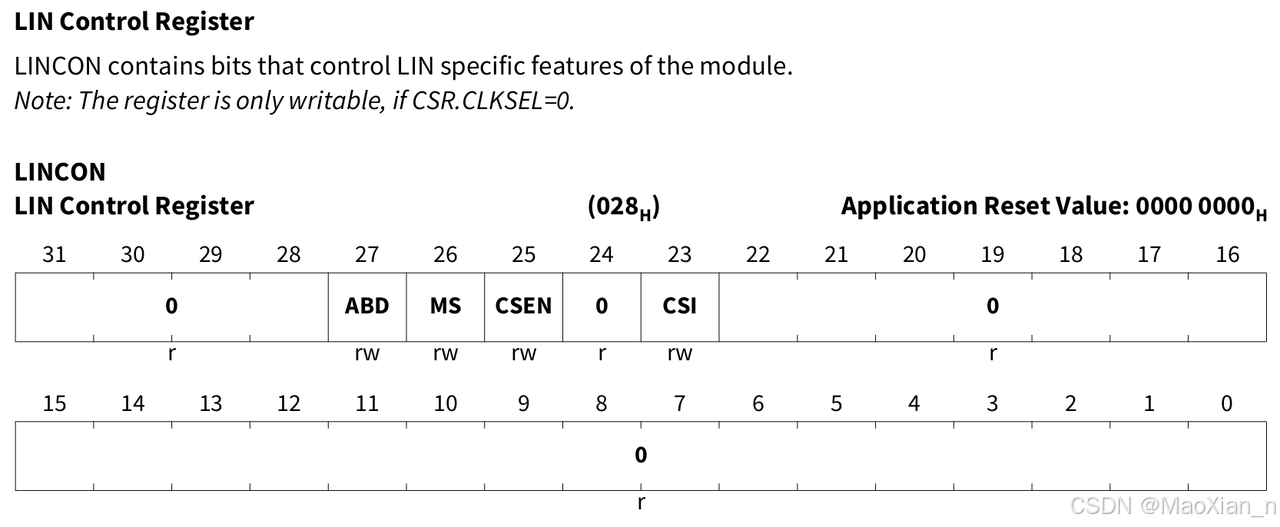

0x28 - LINCON

LIN Control Register - LIN控制寄存器

配置LIN协议特性

注意:仅当CSR.CLKSEL=0时该寄存器可写

-

CSI:Checksum Injection,是否将接收到的校验数据写入RXFIFO-

0:不写入 -

1:写入

-

-

CSEN:Hardware Checksum Enable,使能硬件校验生成和检查-

0:禁用 -

1:使能

-

-

MS:Master Slave Mode,设置LIN模块为Master/Slave模式-

0:Slave -

1:Master

-

-

ABD:Autobaud Detection,使能自动波特率检测,使能LIN Slave的自动波特率检测,其他模式该位无效,如果禁用自动波特率检测(时钟精度足够)会检测同步域(字节域和停止位)的正确性,如果错误则触发帧错误-

0:禁用 -

1:使能

-

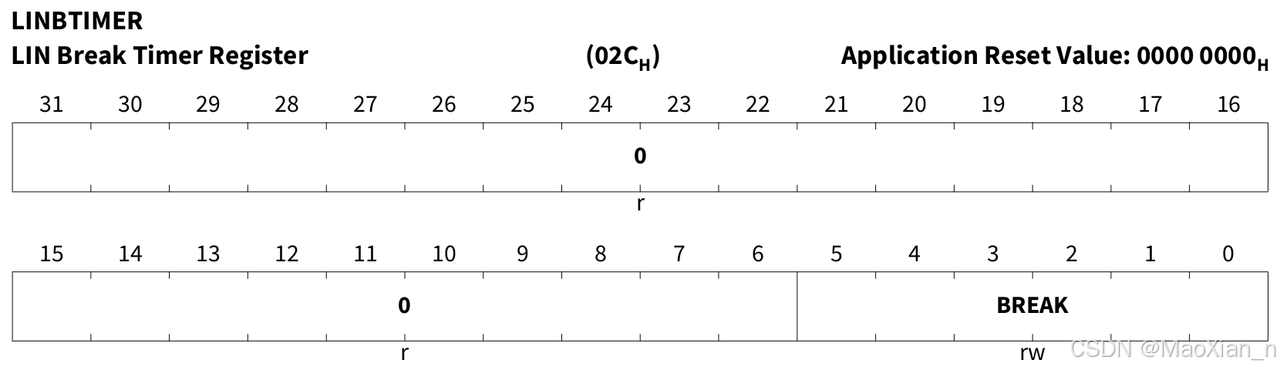

0x2C - LINBTIMER

LIN Break Timer Register - LIN间隔时间寄存器

LIN通讯报文头间隔时间设置

-

LIN Slave模式中定义间隔域检测时限 -

LIN Master模式中定义中断脉冲的长度

如果启用了中断定时器会持续的监视总线

注意:仅当CSR.CLKSEL=0时该寄存器可写

-

BREAK:Break Pulse Generation and Detection,间隔时间,时间单位为Bit-

LIN Slave模式:定义Break Pulse持续时间 -

LIN Master模式:定义传输Break Pulse的持续时间

-

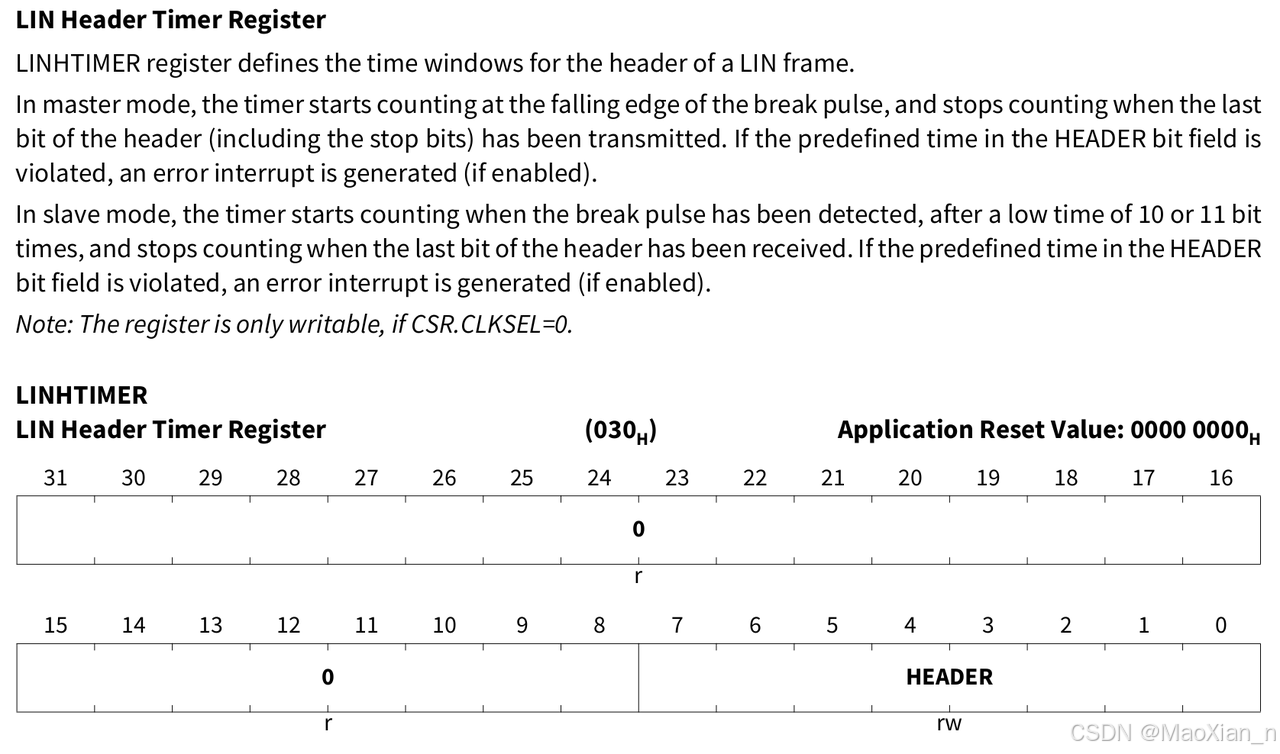

0x30 - LINHTIMER

LIN Header Timer Register - LIN报文头时间寄存器

定义LIN报文头的时间窗口,LIN模式下会记录接收/发送报文头花费的时间,超时会触发错误中断

-

LIN Master模式:定时器在Break Pulse的下降沿开始计数,报文头的最后一位(包含停止位)传输完毕后停止计数,如果HEADER位中预定义的时间为非法值则产生中断 -

LIN Slave模式:定时器在检测到Break Pulse时开始计时,10~11-bit的间隔之后,接收到报文头的最后一位后停止计数,如果HEADER位中预定义的时间为非法值则产生中断

注意:仅当CSR.CLKSEL=0时该寄存器可写

-

HEADER:Header Timeout Threshold Value,报文头超时阈值(范围0~255 bit time)

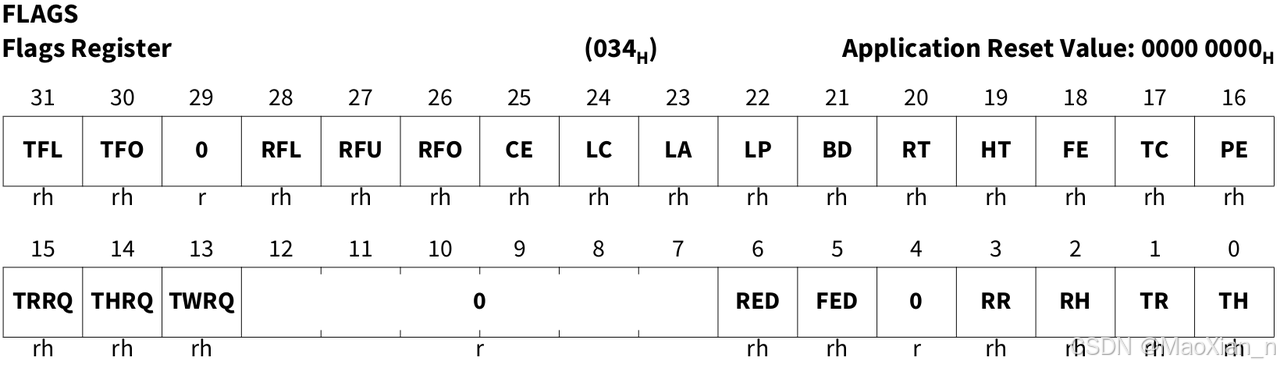

0x34 - FLAGS

Flags Register - 标志位寄存器

ASCLIN所有模块的标志位,可以通过FLAGSENABLE寄存器启用相应的中断触发功能(只有当FLAGSENABLE寄存器中对应的位为1时,才会产生中断)

-

TH:Transmit Header End Flag,HEADER_TX_END,由硬件设置,软件清除,使能后触发发送中断-

0:自上次软件清除该标志位后,未发生过HEADER_TX_END事件 -

1:自上次软件清除该标志位后,产生了新的HEADER_TX_END事件

-

-

TR:Transmit Response End Flag,RESPONSE_TX_END,由硬件设置,软件清除,使能后触发发送中断-

0:自上次软件清除该标志位后,未发生过RESPONSE_TX_END事件 -

1:自上次软件清除该标志位后,产生了新的RESPONSE_TX_END事件

-

-

RH:Receive Header End Flag,HEADER_RX_END,由硬件设置,软件清除,使能后触发接收中断-

0:自上次软件清除该标志位后,未发生过HEADER_RX_END事件 -

1:自上次软件清除该标志位后,产生了新的HEADER_RX_END事件

-

-

RR:Receive Response End Flag,

RESPONSE_RX_END,由硬件设置,软件清除,使能后触发发送中断-

0:自上次软件清除该标志位后,未发生过RESPONSE_RX_END事件 -

1:自上次软件清除该标志位后,产生了新的RESPONSE_RX_END事件

-

-

FED:Falling Edge from Level 1 to Level 0 Detected,检测到下降沿,检测到RX Line的下降沿后由硬件设置-

0:未检测到下降沿 -

1:检测到下降沿

-

-

RED:Rising Edge from Level 0 to Level 1 Detected,检测到上升沿,检测到RX Line的上升沿后由硬件设置-

0:未检测到上升沿 -

1:检测到上升沿

-

-

TWRQ:Transmit Wake Request Flag,唤醒发送请求,不会触发中断,唤醒信号发送后该位由硬件清除-

0:不存在挂起的发送唤醒请求 -

1:发送唤醒请求挂起

-

-

THRQ:Transmit Header Request Flag,报文头发送请求,不会触发中断,硬件在报文头开始发送后清除该位-

0:不存在挂起的报文头发送请求 -

1:报文头发送请求挂起

-

-

TRRQ:Transmit Response Request Flag,应答报文发送请求,不会触发中断,硬件在应答报文开始发送后清除该位-

0:不存在挂起的应答报文发送请求 -

1:应答报文发送请求挂起

-

-

PE:Parity Error Flag,校验位错误,如果计算出的奇偶校验位和接收到的不一致则触发校验错误中断-

0:数据正常 -

1:存在奇偶校验位错误

-

-

TC:Transmission Completed Flag,数据传输完成,表示ASC和SPI数据帧传输结束,ASC模式中在停止位发送完毕后由硬件复位,SPI模式中Trailing Delay之后由硬件复位,在LIN模式中,如果该节点传输的是报文头,则该位在每个间隔域、同步域或者PID域之后都会被设置,如果该节点传输的是应答数据,则会在每个字节传输完成后设置该位,该位会触发EX中断,需要由软件清除-

0:没有传输结束信号 -

1:帧传输完毕

-

-

FE:Framing Error Flag,数据帧错误,当停止位为0时会触发帧错误,如果未使用自动波特率检测,则检查同步域是否存在帧错误-

0:无错误 -

1:上一个接收到的消息存在错误

-

-

HT:Header Timeout Flag,报文头超时,会触发错误中断-

0:自上次软件清除该标志位后,未产生HEADER_OVERFLOW错误 -

1:自上次软件清除该标志位后,产生HEADER_OVERFLOW错误

-

-

RT:Response Timeout Flag,应答超时,超时阈值由DATCON.RM定义,会触发错误中断-

0:自上次软件清除该标志位后,未发生超时事件 -

1:自上次软件清除该标志位后,发生超时事件

-

-

BD:Break Detected Flag,检测到间隔域,会触发错误中断,仅在Slave模式下生效-

0:自上次软件清除该标志位后,未发生Break/Wake/Stuck事件 -

1:自上次软件清除该标志位后,发生Break/Wake/Stuck事件

-

-

LP:LIN Parity Error Flag,LIN ID错误,会触发错误中断,仅在LIN模式中使用,如果计算出的奇偶校验位和接收到的不一致则触发校验错误中断-

0:ID正常 -

1:ID存在奇偶校验位错误

-

-

LA:LIN Autobaud Detection Error Flag,LIN自动检测波特率错误,波特率超过BRD.LOWERLIMIT和BRD.UPPERLIMIT定义的范围-

0:波特率范围正常 -

1:自动波特率检测错误

-

-

LC:LIN Checksum Error Flag,LIN校验和错误,会触发错误中断,如果内部计算的校验和与接收到的校验和不一致则触发错误中断-

0:校验和正常 -

1:产生校验和错误

-

-

CE:Collision Detection Error Flag,检测到冲突,检查发送的数据和接收的数据是否一致,如果不一致则触发错误中断,冲突检测仅在LIN 2.1版本可用-

0:正常 -

1:数据不一致

-

-

RFO:Receive FIFO Overflow Flag,接收上溢Overflow,触发错误中断-

0:正常 -

1:存在Overflow

-

-

RFU:Receive FIFO Underflow Flag,接收下溢Underflow,触发错误中断-

0:正常 -

1:存在Underflow

-

-

RFL:Receive FIFO Level Flag,有接收中断产生,根据RXFIFOCON.FM的配置,RXFIFO是否产生Fill中断-

0:无接收中断 -

1:产生接收中断

-

-

TFO:Transmit FIFO Overflow Flag,发送上溢,发送下溢Underflow,触发错误中断.-

0:正常 -

1:存在Overflow

-

-

TFL:Transmit FIFO Level Flag,有发送中断产生,根据TXFIFOCON.FM的配置,TXFIFO是否产生Fill中断-

0:无发送中断 -

1:产生发送中断

-

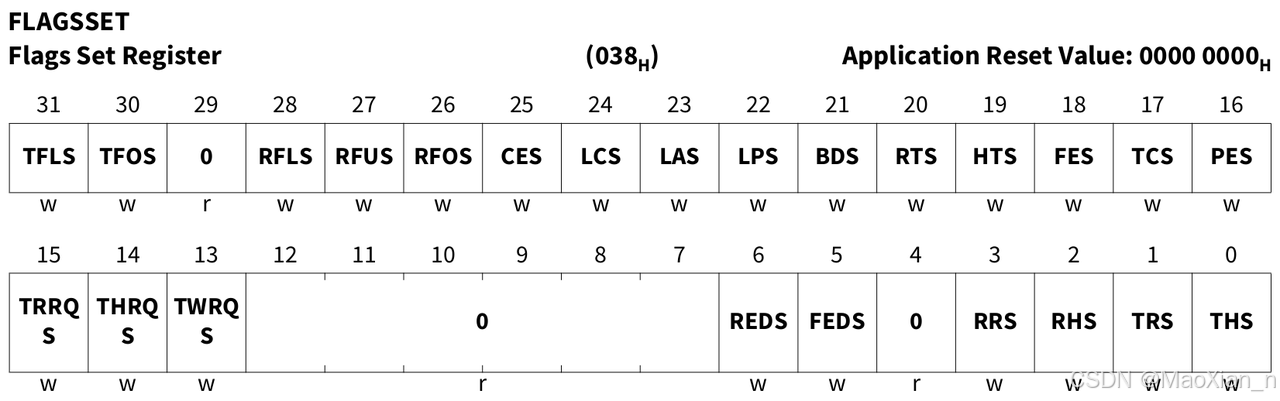

0x38 - FLAGSSET

Flags Set Register - 标志位设置寄存器

设置对应标志位,该寄存器为只写模式,读取只会返回0,向对应的位写1会将FLAGS寄存器的对应位置1,向该寄存器写0不会有任何效果

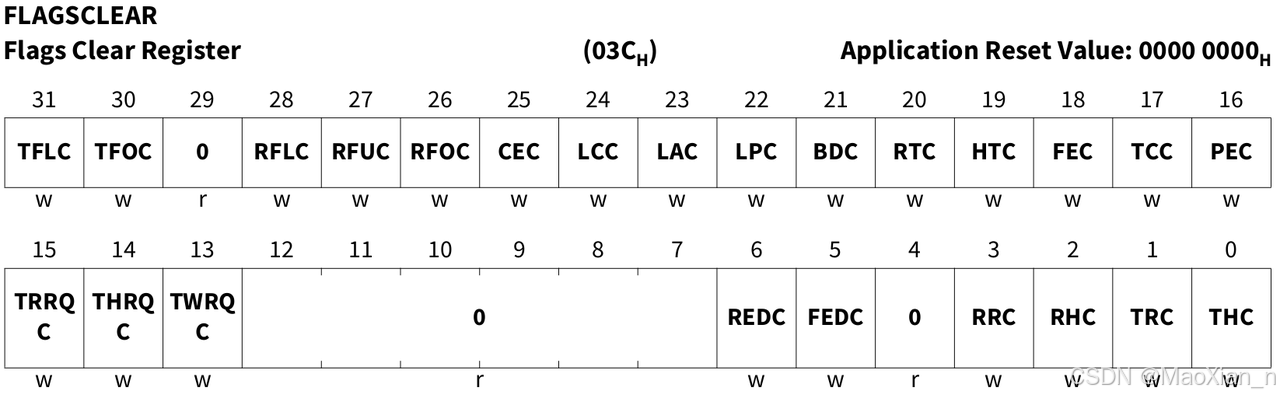

0x3C - FLAGSCLEAR

Flags Clear Register - 标志位清楚寄存器

清除对应标志位,该寄存器为只写模式,读取只会返回0,向对应的位写1会将FLAGS寄存器的对应位置0,向该寄存器写0不会有任何效果

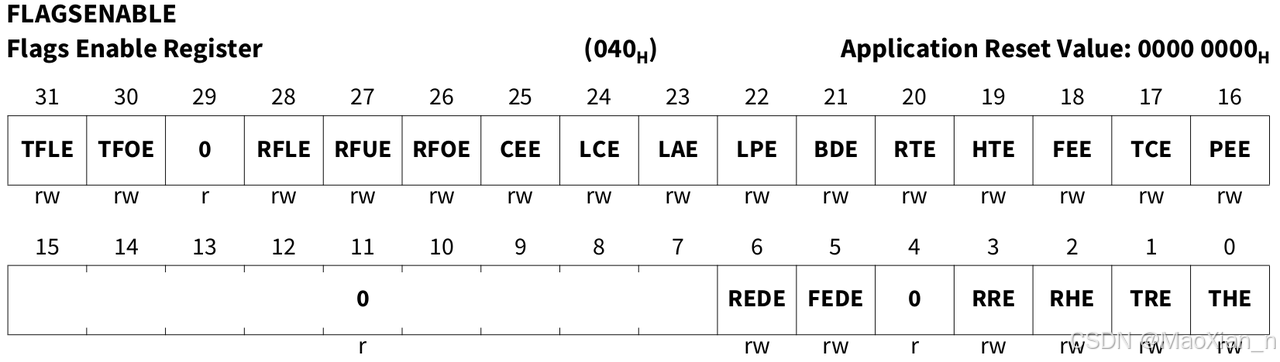

0x40 - FLAGSENABLE

Flags Enable Register - 标志位使能寄存器

一些标志位被设置后可以触发中断,通过该寄存器可以设置FLAGS寄存器中对应的位是否触发中断

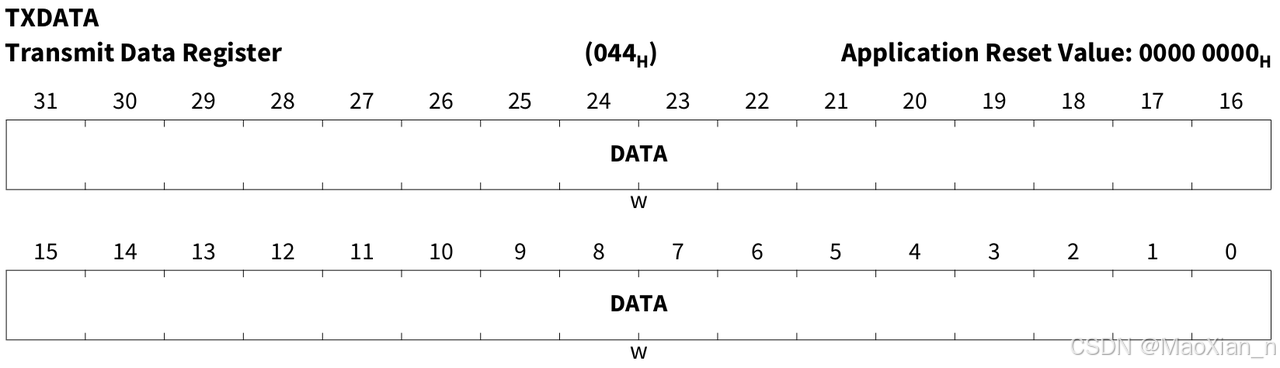

0x44 - TXDATA

Transmit Data Register - 发送数据寄存器

存储用于发送的数据,只写模式,读取只会返回0x0

-

DATA:Data,数据(8、16、32-bit,由TXFIFOCON.INW控制),数据写入该寄存器即为写入TXFIFO

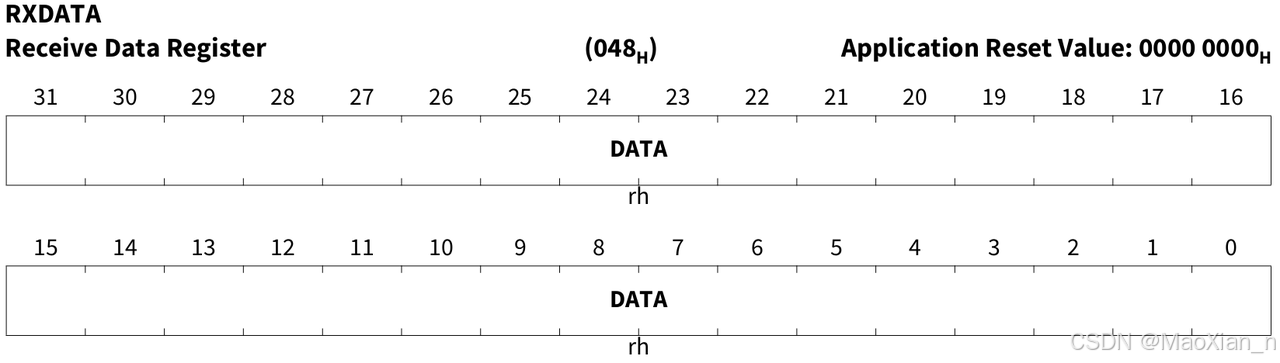

0x48 - RXDATA

Receive Data Register - 接收数据寄存器

存储从RXFIFO中输入的数据,只读模式,向该寄存器中写值无效

-

DATA:Data,数据(8、16、32-bit,RXFIFOCON.OUTW控制),从该寄存器中读取即为读取RXFIFO

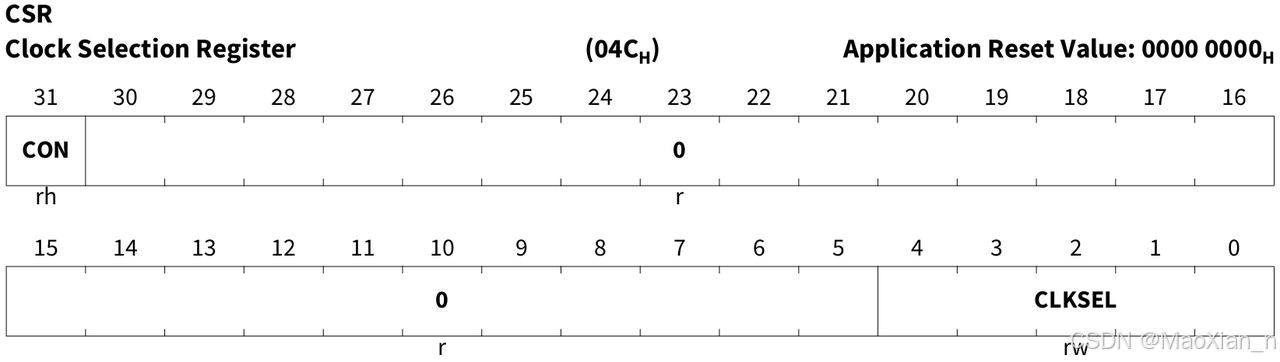

0x4C - CSR

Clock Selection Register - 时钟选择寄存器

波特率发生器、超时检测、SPI延迟中所使用的时钟源选择

-

CLKSEL:Baud Rate Logic Clock Select,波特率时钟源选择-

00:无时钟 -

02:fASCLINF -

04:fASCLINS(以及fOSC0,参考CCU) -

Others:禁止使用

-

-

CON:Clock On Flag,指示时钟状态,部分寄存器只有在时钟状态为OFF的时候才可以写入(IOCR、BITCON、FRAMECON、BRG、BRD、LINCON、LINBTIMER、LINHTIMER)-

0:时钟关闭 -

1:时钟开启

-

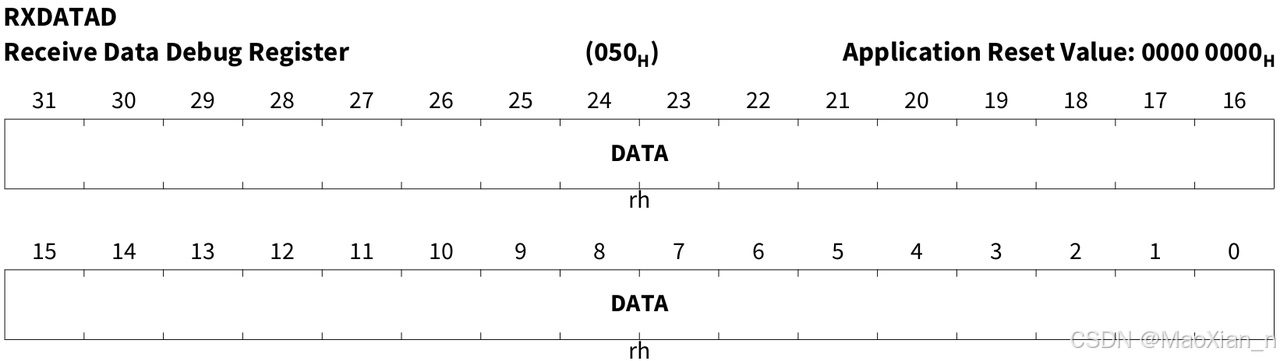

0x50 - RXDATAD

Receive Data Debug Register - 接收数据调试寄存器

从RXFIFO中将数据读取至该寄存器中,但不会改变读取RXFIFO的读取指针(相当于拷贝一份且保留原数据),该寄存器为只读模式,向该寄存器中写值无效

-

DATA:Data,数据(8、16、32-bit,由RXFIFOCON.OUTW控制),从该寄存器中读取即为从RXFIFO中读取数据

0xE8 - OCS

OCDS Control and Status - OCDS控制和状态寄存器

OCDS控制和状态寄存器OCS,控制模块在Suspend模式下的行为(调试时使用),使用Debug Reset可以清空OCS寄存器,只有当OCDS使能时才能读写OCS寄存器,如果OCDS为禁用状态则OCS寄存器中的值不会改变,同时Suspend控制也会失效

-

SUS:OCDS Suspend Control,是否响应OCDS发送的发送的挂起信号-

0:忽略信号 -

1:硬件挂起,立即关闭时钟信号 -

2:软件挂起

-

-

SUS_P:SUS Write Protection,写入保护,仅当SUS_P为1时才可以修改SUS,读取该位返回0 -

SUSSTA:Suspend State,指示模块是否为挂起状态-

0:模块未挂起 -

1:模块已经挂起

-

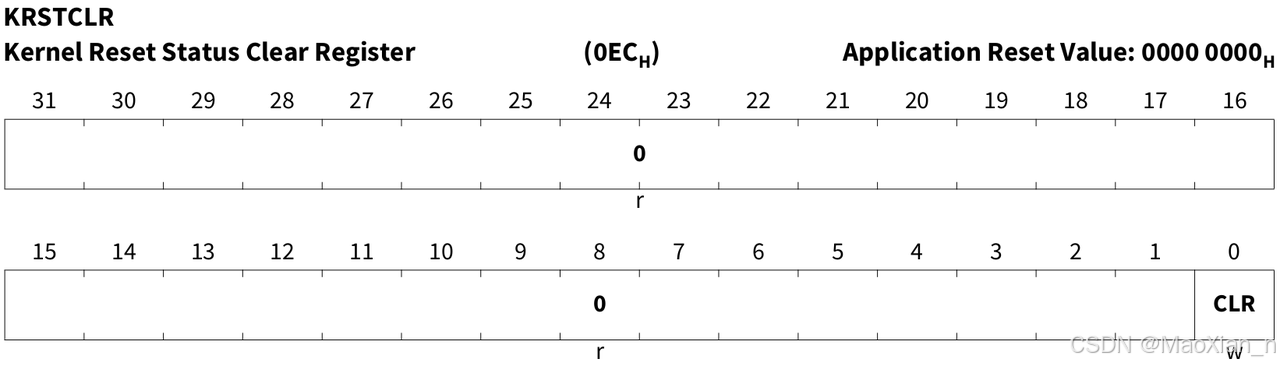

0xEC - KRSTCLR

Kernel Reset Status Clear Register - 内核重置状态清除寄存器

用于清除内核复位状态位KRST0.RSTSTAT

-

CLR:Kernel Reset Status Clear,内核复位状态清除,写1将KRST0.RSTSTAT置0-

0:无操作 -

1:清除内核复位状态KRST0.RSTSTAT

-

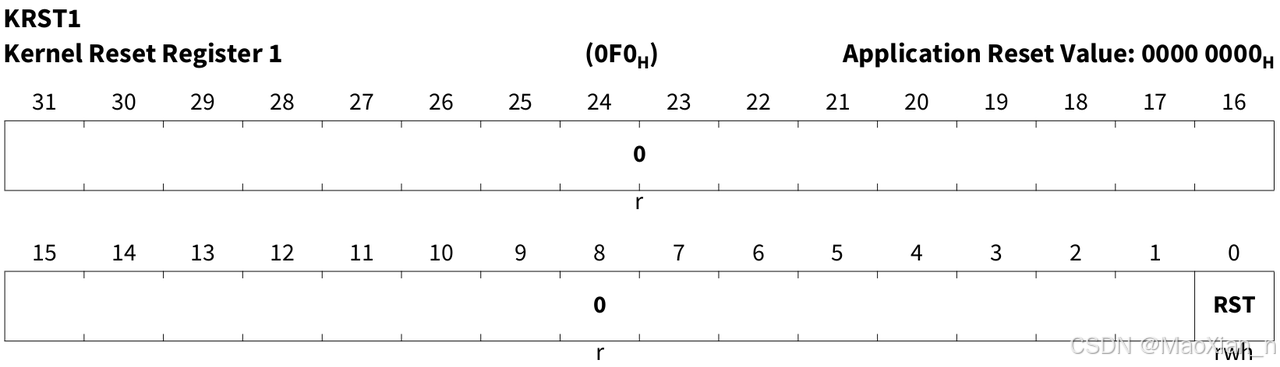

0xF0 - KRST1

Kernel Reset Register 1 - 内核重置寄存器1

用于内核相关模块复位,Debug Reset相关的内核重置寄存器不受影响,复位内核模块时需要向RST位写1,当内核模块复位序列完成后,BPI总线会重置RST位

-

RST:Kernel Reset,内核复位请求,如果两个内核复位寄存器的RST都被设置,则执行内核复位,内核复位执行后,BPI_FPI会重置RST位-

0:没有复位请求 -

1:存在复位请求

-

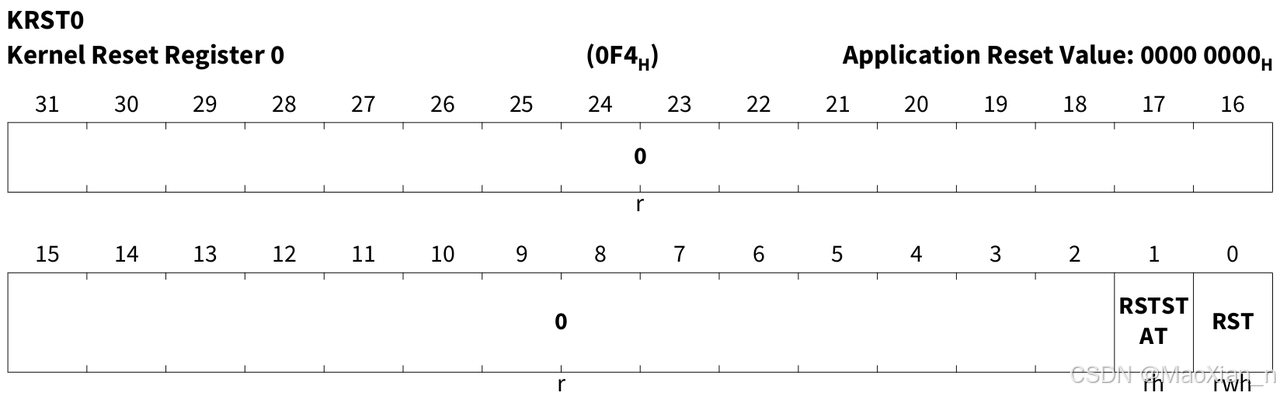

0xF4 - KRST0

Kernel Reset Register 0 - 内核重置寄存器0

用于内核相关模块复位,Debug Reset相关的内核重置寄存器不受影响,复位内核模块时需要向RST位写1,当内核模块复位序列完成后,BPI总线会重置RST位,该寄存器包含一个内核重置状态位,当RST标志位被BPI_FPI复位的同时会将该标志位置1,该标志位可用于检查内核是否被复位,通过向KRSTCLR.CLR写1可以将RSTSTAT标志位置0

注意:内核复位过程中(直至RSTSTAT置1),访问内核寄存器会导致错误

-

RST:Kernel Reset,内核复位请求,如果两个内核复位寄存器的RST都被设置,则执行内核复位,内核复位执行后,BPI_FPI会重置RST位-

0:没有复位请求 -

1:存在复位请求

-

-

RSTSTAT:Kernel Reset Status,指示内核模块是否已执行复位,BPI_FPI在同一时钟周期内执行内核复位后,会重置该位,可以通过向KRSTCLR寄存器的CLR位写1清除该位-

0:未执行过内核复位 -

1:内核复位已执行

-

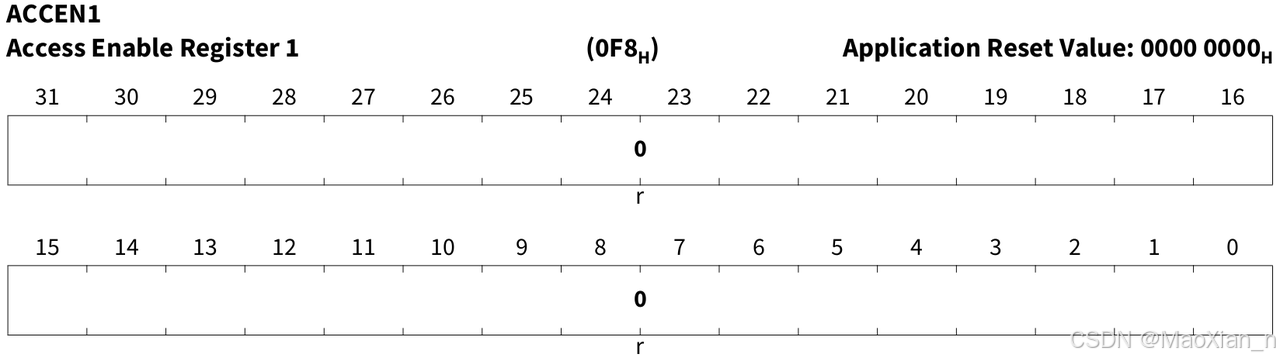

0xF8 - ACCEN1

Access Enable Register 1 - 写入许可寄存器

控制片上总线(TAG ID 100000B~111111B)事务的写入许可,BPI_FPI允许6-bit的TAG ID,ACCEN0寄存器为每一个TAG ID提供了一个使能位

映射关系:EN0 --> 100000B,EN1 --> 100001B,......,EN31 --> 111111B

-

该寄存器未使用

0xFC - ACCEN0

Access Enable Register 0 - 写入许可寄存器

控制片上总线(TAG ID 000000B~011111B)事务的写入许可,BPI_FPI允许6-bit的TAG ID,ACCEN0寄存器为每一个TAG ID提供了一个使能位

映射关系:EN0 --> 000000B,EN1 --> 000001B,......,EN31 --> 011111B

-

ENn:Access Enable for Master TAG ID n,TAG ID n的写入许可,该位使能对内核地址的写入权限-

0:写入操作不被执行 -

1:允许写入操作

-

36.5.使用示例

本小节通过代码示例,描述ASCLIN模块的核心功能,该示例使用ASC LoopBack模式进行数据收发,相关设置如下:

-

示例使用

ASCLIN0模块; -

数据长度:

8-bit; -

波特率:

9600Bd; -

1个停止位、启用奇偶校验、16倍超采样、采样点为数据流的第7/8/9位; -

启用

Rx/Tx中断;

初始化ASCLIN0

按以上配置初始化ASCLIN0的流程如下:

-

复位

ENDINIT(获取受ENDINIT保护的寄存器),这里指ASCLIN0_CLC寄存器; -

设置

CLC寄存器的模块使能位; -

创建

CLC寄存器的临时变量,将当前CLC寄存器的值存入其中,避免多线程影响; -

重新设置

ENDINIT,保护CLC寄存器; -

通过

CSR寄存器设置时钟源,时钟源设置前需要先禁用时钟(CSR [4:0] = 0),完成相关设置后,在步骤20设置时钟源; -

通过输入输出控制寄存器

IOCR设置LoopBack模式; -

清空并使能

TxFIFO,定义每个时钟周期写入的数据长度为1个字节,TxFIFO填充等级(用于中断触发)设置为0,当TxFIFO的填充等级小于等于阈值时会触发Tx中断,在步骤14中使能Tx中断; -

与步骤

7类似,初始化RxFIFO; -

通过

BITCON寄存器配置超采样倍数(16)、采样点(7、8、9)、波特率的预分频倍数(10); -

通过

FRAMECON寄存器配置使用1个停止位、将模块设置为基本模式、启用奇偶校验功能; -

通过

DATCON寄存器设置数据宽度(8-bit); -

通过

BRG寄存器,将波特率时钟分频器的值设置为48/3125;-

注意:对应的

ASCLIN模块的时钟频率fA = 100MHz,prescaler = 10,oversampling = 16,fshift = (fclc/prescaler * 48/3125) / oversampling = 9600Bd;

-

-

设置中断使能标志前,通过

FLAGSCLEAR寄存器清除所有中断标志; -

配置

FLAGSENABLE寄存器,使能Tx/Rx中断; -

配置中断控制器的

SRC_ASCLIN0_Tx寄存器,设置Tx的中断优先级、中断服务对象等; -

配置中断控制器的

SRC_ASCLIN0_Rx寄存器,设置Rx的中断优先级、中断服务对象等; -

调用中断配置函数,根据

Tx的中断优先级,将中断服务程序插入中断向量表; -

调用中断配置函数,根据

Rx的中断优先级,将中断服务程序插入中断向量表; -

设置

ASCLIN0模块为ASC模式;

注意:Tx/Rx ISR的形式类似于void ASC0_TX_ irq(void),其中定义了具体的中断处理程序

初始化ASC接口

SCU_vResetENDINIT (0); // ENDINIT 寄存器 UnLock

ASCLIN0_CLC = 0x000; // 禁用模块

dummy = ASCLIN0_CLC; // 回读 CLC 寄存器

SCU_vSetENDINIT (0); // ENDINIT 寄存器 Lock

ASCLIN0_CSR = 0; // 禁用时钟

ASCLIN0_IOCR = 0x10000001; // LoopBack Mode

ASCLIN0_TXFIFOCON = 0x00000043; // TxFIFO 初始化

ASCLIN0_RXFIFOCON = 0x00000043; // RxFIFO 初始化

ASCLIN0_BITCON = 0x830F0009; // 采样倍数 16、采样点 7,8,9、波特率分频倍数 10

ASCLIN0_FRAMECON = 0x40000200; // 1 个停止位,设置默认模式

ASCLIN0_DATCON = 0x7; // 数据宽度 8-bit

ASCLIN0_BRG = 0x00300C35; // 波特率分频器

ASCLIN0_FLAGSCLEAR = 0xFFFFFFFFF; // 清除所有中断标志

ASCLIN0_FLAGSENABLE = 0xF0000000; // Tx/Rx 中断使能

SRC_ASCLIN0TX = (1 << 10) | ASC0TX_PRIO; // Tx 中断优先级设置

SRC_ASCLIN0RX = (1 << 10) | ASC0RX_PRIO; // Rx 中断优先级设置

interruptHandlerInstall (ASC0TX_PRIO, & ASC0_TX_irq); // 加载 Tx 的中断服务例程

interruptHandlerInstall (ASC0RX_PRIO, & ASC0_RX_irq); // 加载 Rx 的中断服务例程

ASCLIN0_FRAMECON |= 0x00010000; // 将 ASCLIN0 设置为 ASC 模式注意:允许Tx/Rx中断前,必须保证全局中断使能(ICR.IE = 1),ICR.IE控制全局中断使能/禁用,大部分编译器都支持通过__enable()属性设置该bit位

36.6.I/O接口