1、预定义的数据类型

std库的standard包集:定义了位(BIT)、布尔(Boolean)、整数(integer)和实数(real)数据类型。

ieee库的std_logic_1164包集:定义了std_logic和std_ulogic数据类型。

ieee库的std_logic_arith包集:定义了signed和unsigned数据类型。还定义了conv_integer(p),conv_unsigned(p,b)和conv_signed(p,b)

和conv_std_logic_vector(p,b)等数据类型转换函数。

ieee库的std_logic_signed和std_logic_unsigned包集:包含一些函数,这些函数可以使std_logic_vecture类型的数据进行

像signed和unsigned类型数据一样的运算。

位(bit)和位矢量(bit_vector):位值用'0'或'1'表示。

例:

signal x:bit;

将x声明为一个位宽为1的bit类型的信号。

signal y:bit_vector(3 downto 0);

将y声明为一个位宽为4的位矢量,其中最左边的一位是最高位(MSB:most significant bit)。

signal w:bit_vector(0 downto 7);

--将w声明为一个位宽为8的位矢量,它的最右边的一位是MSB。

在定义了上述信号以后,可以采用下面的方式对信号赋值(必须使用"<="操作符给信号赋值)。

x<='1';

--x是位宽为1,值为'1'的信号。注意,当位宽为1时,位值放在单引号中。

y<="0111";

y是位宽为4,值为"0111"(MSB='0')的信号。注意,当位宽大于1时,位矢量值放在双引号中。

w<="01111001"

w的位宽为8,值为"01111001"(MSB='1')的信号。

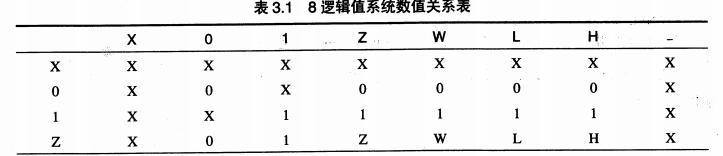

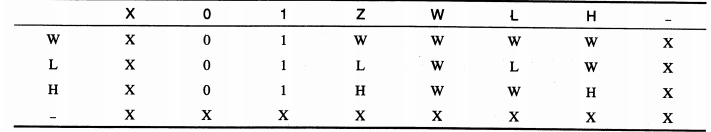

std_logic和std_logic_vector:它们是ieee 1164标准中引入的8逻辑值系统。不同于bit 数据类型,它可以取'0','1',不定态和

高阻态等8种不同的值。

'X' “强” 不确定值(综合后为不确定值)

'0' “强” 0(综合后为0)

'1' “强” 1(综合后为1)

'Z' 高阻态(综合后为三态缓冲器)

'w' “弱” 不确定值

'L' “弱” 0

'H' “弱” 1

'-' 不可能出现的情况

例:

signal x:std_logic;

--声明x是位宽为1的std_logic类型的信号。

signal y:std_logic_vector(3 downto 0) :="0001";

声明y是一个位宽为4的矢量,其中最左边的一位是MSB。

对信号y赋初始值"0001"(可选)。

std_ulogic和std_ulogic_vector:是ieee 1164标准中定义的具有9种逻辑值数据类型