(一)访问 ITCM 和 BIU

- IFU 有两个ICB接口,一个用于访问ITCM(数据宽度为64位),另一个用于访问BIU (数据宽度为32位)

- 根据IFU 访问的地址区间进行判断,如果访问的地址落在ITCM区间,则通过ICB接口进行访问,否则通过BIU的 ICB 对外部存储进行访问。

(1)如果访问的是ITCM,由于ITCM是由SRAM构成的,因此上次访问读过SRAM之后,SRAM的输出值会一直保存住(Hold-up),而无需将ITCM的输出使用DFF 寄存住,可以省略一个64bit的寄存器开销。

(2)而且由于SRAM 是64位,会连续两次或者多次在同一个lane中访问。如果上次已经访问了SRAM,下一次会直接使用保持不变的输出,这样可以省却SRAM重复打开造成的动态功耗。

(3)对于容量不是特别大的SRAM,使用宽度64位的SRAM比32位的SRAM面积更紧凑。

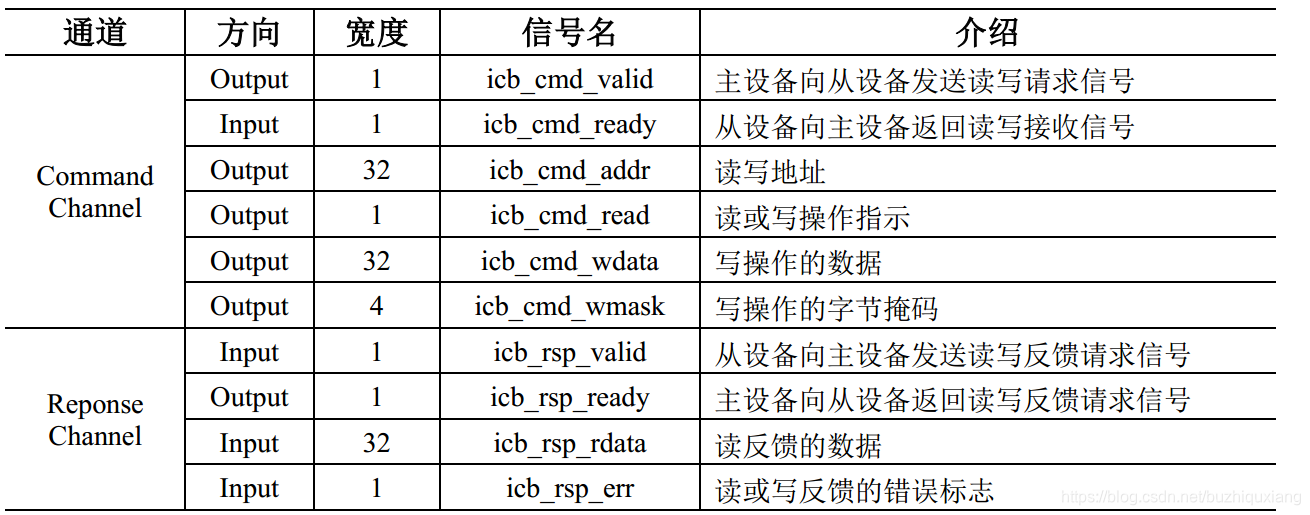

(二)ICB总线

ICB总线具有如下特性:

- ICB仅有两个独立的通道,读和写操作共用 地址通道,共用 结果返回通道

- 与AXI总线一样,采用分离的地址和数据阶段

- 与AXI总线一样,采用地址区间寻址,支持任意的主从数目。

- 与AHB总线一样,读写操作都会在地址通道上产生地址,而非像AXI只产生起始地址

- 与AXI总线一样,支持地址非对齐的数据访问,使用字节掩码(write Mask)来控制部分写操作

- 与AXI总线一样,支持多个outstanding transaction

- 与AHB总线一样,不支持乱序返回乱序完成,必须顺序返回结果

- 与AXI总线一样,易于添加流水线的级数

- 易于转换成其他总线类型,如:AXI、AHB、APB、或者TileLink

写操作:

- 主设备通过ICB的命令通道向从设备发送写操作请求(icb_cmd_read 为低,icb_cmd_valid 为高,发送写地址以及写数据),从设备立即接受该请求(icb_cmd_ready 为高)

- 从设备在同一个周期返回反馈且结果正确(icb_rsp_err 为低,icb_rsp_valid 为高),主设备立即接受该结果(icb_rsp_ready为高)

读操作:

- 主设备通过ICB的命令通道向从设备发送读操作请求(icb_cmd_read 为高,icb_cmd_valid为高,发送读地址),从设备立即接受该请求(icb_cmd_ready为高)

- 从设备在下一个周期返回反馈且结果正确(icb_rsp_err 为低,icb_rsp_valid 为高),主设备立即接受该结果(icb_rsp_ready为高)

(三)ICB总线的硬件实现

对于一主多从而言:

输入命令通道(输入为一个,输出为多个;需要通过地址区间进行分发)

输入反馈通道(输入为一个,输出为多个;需要进行仲裁,而分发信息就是仲裁的标准,而输入命令通道的分发信息到输入反馈通道的选择需要经过一个FIFO,FIFO的深度(默认为一)决定了该模块能够支持的多个滞外交易的个数)

还有一种情况比较特殊,就是FIFO为空时,没有outstanding transaction ,并且分发的ICB交易可以被从设备在同一周期内立即返回结果,则分发信息无需进入FIFO,直接由旁路进入选择)

对于多主一从而言:

输入命令通道(输入为多个,输出为一个;需要仲裁,可以使用轮询或者优先级的仲裁机制)

输入反馈通道(输入为多个,输出为一个;通过FIFO传递仲裁信息,分发给输入反馈通道,FIFO的深度决定了该模块能够支持的多个滞外交易的个数)

还有一种情况比较特殊,就是FIFO为空时,没有outstanding transaction ,并且分发的ICB交易可以被从设备在同一周期内立即返回结果,则分发信息无需进入FIFO,直接由旁路进入分发)

对于多主多从而言,可以由多主一从 - 一主多从构成

(四)BIU模块

- BIU 有两组输入ICB总线接口,分别来自于IFU和LSU单元

- 将两组ICB总线汇合成一组ICB总线,采用仲裁机制是优先级仲裁(LSU具有更高的优先级)

- 加入乒乓缓存(ping-pong Buffer)

- 经过ICB总线通过其命令通道的地址进行判断,产生分发信息

- 分发给

(1)快速IO接口ICB

(2)私有外设接口ICB

(3)系统存储接口ICB

(4)CLINT接口ICB

(5)PLIC接口ICB

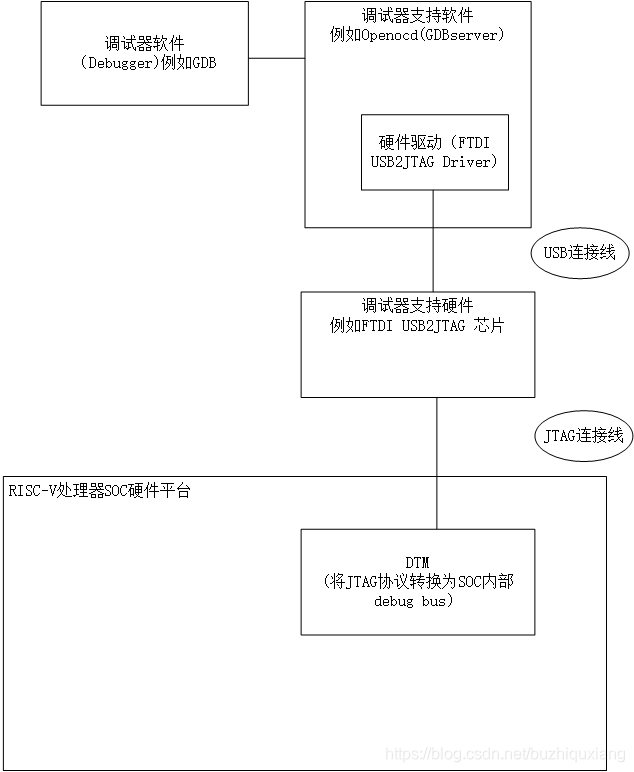

交互调试(Interactive Debug)指调试器软件(例如GDB)能够直接对处理器取得控制权,进而对其以一种交互的方式进行调试。

- 下载或者启动程序

- 通过设定各种特定条件来停止程序

- 查看、改变处理器的运行状态(包括通用寄存器的值、存储器地址的值等)

- 查看、改变程序的状态(包括变量的值、函数的状态等)

在处理器核的硬件中,需要一个硬件调试模块(通过物理介质,如JTAG接口)与主机端的调试软件进行通信接受其控制,然后调试模块对处理器核进行控制。

(1)通过运行于主机端的GDB软件在其软件界面上设置某行程序的断点,GDB软件通过底层驱动JTAG接口访问远程处理器的调试模块,希望在某个PC值处设置一个断点。

(2)调试模块对处理器核进行控制,首先请求处理器核停止,然后修改存储器中那个PC地址的指令,将其替换成一个Breakpoint指令;最后让处理器恢复执行

(3)当处理器执行到那个PC地址时,遇到Breakpoint指令,会产生异常进入调试模式的异常服务程序,并将信息显示出来。

(4)通过GDB软件设置读取某个寄存器的值,GDB软件通过底层驱动JTAG接口访问远程处理器的调试模块

(5)调试模块对处理器核进行控制,从处理器核将那个寄存器的值读取出来。

注意:由于交互性调试的打扰,使得程序在调试模式和全速运行下的结果可能会有差异。(对于高端的处理器,一般采用跟踪调试的方法,即调试器只跟踪处理器核执行过的所有程序指令,而不会打断处理器的执行过程)