一、网络表的作用

OrCAD绘制原理图——》Netlist(语言描述文本)——》allegro

allegro支持两种网络表:一种为allegro方式、另一种other方式

导入allegro进行电路同步,在allegro中产生back annotate转出,并转入OrCAD进行反标回编。

二、网络表的导出、allegro方式

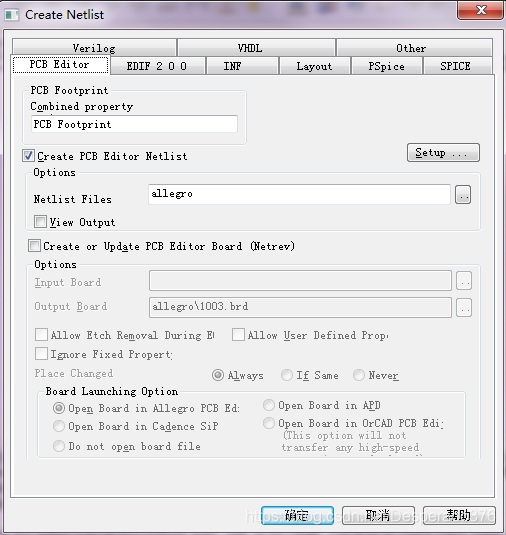

1、选中dsn文件,tools下的create netlist

三、allegro方式网络表解读

allegro网络表文件有三个:pstxnet.dat描述各个元件之间电气连接

pstxprt.dat描述封装信息

pstchip.dat描述元件引脚信息

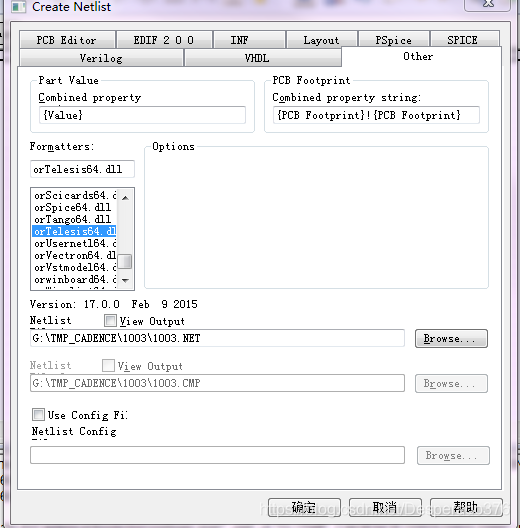

四、网络表的导出、other方式

Create netlist下的other选择ortelesis,

并修改{PCB Footprint}!{PCB Footprint},选择路径进行保存

五、other方式网络表解读

allegro加载netlist基本内容为device和reference

六、device文件

device文件为元件完整的信息:封装构造、元件类型、封装引脚数量、电气特性、各个功能与封装映射关系、PIN use等。

$package部分格式:封装名!device文件名!元件value值

七、文件路径加载

devpath:是device的路径

padpath:是焊盘的路径

psmpath:是symbol的路径

八、allegro方式网络表导入

cadence选项卡中design enty HDL表示导入网表为design enty HDL

Design enty CIS表示导入网表为orCAD capture cis设计的

更新问题:always:总是更新,原理图中修改总是更新到pcb中

never:从不更新,不会自动更新,需要手动

If same symbol:一样时候不更新

Allow etch removal during eco:新导入网络表,改变后引脚多余走线自动删除

Igron fixed property:当满足替换条件时,忽略有fixed属性

Create user-defined properties:根据网络表属性建立电路板属性

Create pcb xml from input data:生成xml文件

导入的过程中没有出现错误,对话框自动关闭

九、other方式网络表导入