作者:AirCity 2020.2.6

[email protected] 本文所有权归作者Aircity所有

PDN设计的目的是降低电源纹波水平,减小电压跌落。我们通常要求LDO的文波水平是30mV,DCDC是50mV,超过这个上限,就需要优化PDN设计。

PDN设计的方法是用不同的容值,合适的总电容量,降低电源平面与地平面之间的交流阻抗,确定容值总量和电容大小的过程,就是PDN设计过程。

1.为什么需要PDN?

不管是LDO供电还是DCDC供电,电源的输出动态响应能力都是有限的,大约是ms~us级别。而负载端,比如CPU,他的电流需求也是在迅速变化的,这个变化的频率可能在几百兆HZ,甚至GHz。当电源输出跟不上负载的电流需求变化时,电源的输出电压会出现跌落。

此外,由于电源走线、焊盘、过孔等阻抗,ESL的影响,变化的电流也会产生电压出现跌落。

用一个公式来表示这种电压变化:

ΔV=Z×ΔI------公式(1)

其中,Z表示电源对GND的阻抗,它的值随频率变化而改变。Z受过孔的R,ESL影响,也受电源和GND之间的电容影响。

2.为什么电容能解决PDN问题?

电容是储能器件,每一个都相当于一个小电池。大电容储能多,小电容储能少。把他们放在负载端附近,相当于放了很多“小电池”或“小水库”,当负载瞬间电流增大,而电源由无法及时提供时,由这些电容为负载提供瞬间电流。我们通常说的“去耦”“退偶”就是这个意思。

3.如何用电容解决PDN问题?

从公式(1)得知,降低Z就可以降低ΔV。Z越低,电源的纹波就越小,但是我们很难在工程项目中获得理想的电源平面和地平面。而且,由于ESL和电容的存在,这个阻抗在不同的频率下是不一样的。

ESL很难被消除,只能在设计中尽量避免,比如缩短走线长度,电容两端到对应电源网络的走线(过孔)尽量短。

电容是很容易增加的,所以必须通过电容解决实际工程中的PDN问题。

PDN的目标是选择合适的容值,使Z所有关心的频率下,都低于目标值,以获得比较小的文波。

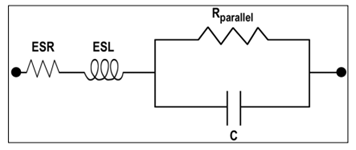

电容的模型如下:

每个电容都有自己的阻抗曲线,下图是几种常见MLCC电容的阻抗曲线,包含0201 0.1uF,0201 1uF,0201 2.2uF,0402 2.2uF,0402 4.7uF,0402 10uF,0402 22uF。陶瓷电容的曲线比较陡峭,容值越大,最低点(谐振频率点)约靠左。

下图是几种钽电容的阻抗曲线,比较平坦,但阻抗明显较高。

下图是几种聚合物电容的阻抗曲线,比较陡峭,并且阻抗很低。

有关电容的介绍参考文章系列文章《深入了解电容》

上图是电容的自身参数的阻抗曲线,如果考虑安装到主板上的寄生参数,特别是ESL,这些曲线都会整体往左移动。

通常会用多个电容去耦,这些电容相当于并联,他们的阻抗也是并联。将这些电容的曲线合并后,得到的曲线,要求在关心的频段内,阻抗小于“目标值”。

4.如何确定阻抗目标值?

参考如下公式:

Rmax=∆V/∆Imax=(V×Ripple)/∆Imax

Ripple指要求的纹波水平,比如2.5%,这个值很容易获得。∆Imax往往不好获得,用如下方法估算:

假设IO的输入电容CIN=30pF,上升时间Tr=2ns,电压3.3V,瞬间电流需求:

I=C×dV/dT=30×3.3/2=49.5mA

这是目标阻抗是:

Rmax=(3.3*2.5%)/49.5=1.7Ω

根据这个目标阻抗选择电容数量吧。

以上只是非常粗略的计算,实际在设计项目时,CPU厂家应该给出关键电源管脚在不同频率下的阻抗要求,然后根据选用的电容,PCB走线仿真出实际的阻抗值,看是是否符合要求。

在此提供一些经验公式和数据:

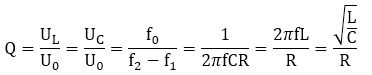

Q值定义为有效电压/加载电压,电容的Q值计算公式如下:

电容的Q值越大,频率选择性越好。

MLCC的ESR很低,对于容值C也很小的电容,Q值很大。

钽电容的ESR比较高,容值也很高,Q值往往很小。

铝电解电容的ESR更高,容值高,Q值更小。

电容的ESL近似值:

1210——980pH

1206——1250pH

0805——1050pH

0603——870pH