DMA ist direkter Speicherzugriff. In FPGA-Systemen gibt es mehrere häufig verwendete DMA-Anforderungen:

1. Es gibt kein PS innerhalb des PL (die CPU wird hier zusammenfassend als PS bezeichnet), um kontinuierlich in die Datenbewegung einzugreifen. Die gängigen Schnittstellenformen sind AXIS und AXI, AXI und AXI;

2. Das Verschieben von Daten zwischen PL und PS ist für ZYNQ einfacher zu verstehen. Es gehört zur internen Schnittstelle eines einzelnen Chips. Bei anderen Schnittstellen wie PCIe ist es etwas komplizierter und gehört zur Schnittstelle zwischen mehreren Chips.

Entdecken Sie den Zweck des DMA-Ansatzes:

1. Verstehen Sie die Methoden der Datenbewegung innerhalb des Chips, die gemeinsamen Schnittstellen und Implementierungsmethoden von DMA;

2. Verstehen Sie die Datenbewegungsmethoden zwischen Chips, gemeinsamen Schnittstellen und Implementierungsmethoden von DMA;

Durch dieses Verständnis kann eine Rahmenstruktur für die Systemdatenmigration erstellt werden. Wenn ein ähnlicher Bedarf entsteht, ist eigentlich nur der Aufruf vorhandener Module zur Umsetzung erforderlich.

Dieser Artikel beginnt mit einer Einführung in jede DMA-IP von Xilinx, hauptsächlich aus der Perspektive der Schnittstellen.

1 AXI4 BIS AXI4

1.1 AXI Central DMA Controller

Der AXI-CDMA bietet einen direkten Speicherzugriff (DMA) mit hoher Bandbreite zwischen einer speicherabgebildeten Quelladresse und einer speicherabgebildeten Zieladresse unter Verwendung des AXI4-Protokolls. Eine optionale Scatter Gather (SG)-Funktion kann verwendet werden, um Steuerungs- und Sequenzierungsaufgaben von der System-CPU zu entlasten. Der Zugriff auf Initialisierungs-, Status- und Steuerregister erfolgt über eine AXI4-Lite-Slave-Schnittstelle, die für den Xilinx MicroBlaze™-Prozessor geeignet ist.

Warum heißt es CDMA? Eigentlich dient es der Datenübertragung innerhalb des auf der CPU montierten AXI-Schnittstellenspeichers. Das typische Szenario ist MicroBlaze. Warum nicht ZYNQ sagen? Der AXI von ZYNQ ist direkt in der CPU montiert und erfordert keinen DMA zur Steuerung. Bei Bedarf wird die Software direkt kopiert, und die Kopieraktion initiiert intern einen AXI-DMA-Vorgang. Wenn ZYNQ jedoch DDR auf der PL-Seite verwenden möchte, muss es für den Betrieb CDMA verwenden, da ZYNQ keine AXI-Master-Schnittstelle, sondern nur SLAVE hat (hier handelt es sich um Hochleistungs-HP-Schnittstellen, nicht um GP-Low-Speed-Schnittstellen). .

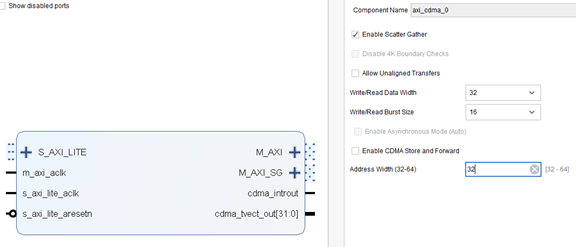

Abbildung 1-1 AXI-CDMA-Schnittstelle und Parameteroptionen, wobei S_AXI_LITE mit der Hauptsteuerungs-CPU verbunden ist, M_AXI mit dem Speicher verbunden ist und M_AXI_SG mit dem Speicher verbunden ist (wird zum Speichern des DMA-Deskriptors im SG-DMA-Modus verwendet).

Abbildung 1-2 CMDA-internes Strukturblockdiagramm

Abbildung 1-3 ZYNQ-Blockdiagramm, nur Hochleistungs-AXI-SLAVE, kein MASTER

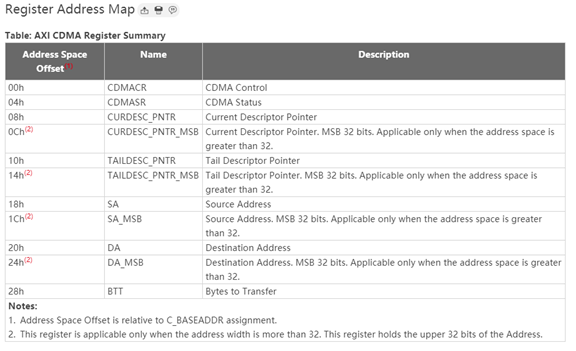

Werfen wir einen Blick auf die internen Register. Diese sind tatsächlich intuitiver und zeigen dem Benutzer, wie das Modul konfiguriert werden soll. Anhand der Konfigurationsmethode können wir einfach die Komplexität der Verwendung des Moduls abschätzen. Die Verwendung von Registerdefinition, Steuerung, Statuserkennung, Deskriptorzeiger von SG DMA, Startadresse, Zieladresse und Länge von einfachem DMA ist nicht kompliziert. Anschließend wird empfohlen, den entsprechenden Softwarecode direkt in den ZYNQ-seitigen Treibercode von Xilinx zu kopieren und ihn dann mit geringfügigen Änderungen zu verwenden.

Werfen wir abschließend einen Blick auf die Ressourcenbelegung. Die Ressourcenbelegung ist proportional zur Bitbreite. Normalerweise belegt sie bei einer 64-Bit-Datenbitbreite etwa 1500 LUTs und 2500 FFs. Aus meiner Sicht ist diese Ressource ziemlich gut.

Abbildung 1-4 Ressourcennutzung

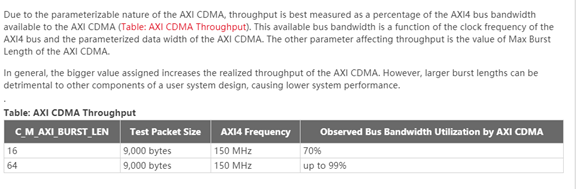

Abbildung 1-5 Übertragungseffizienz und Bandbreite

2 AXI-Stream zu AXI4

2.1 AXI DataMover

Der AXI Datamover ist eine wichtige Interconnect-Infrastruktur-IP, die die Übertragung von Daten mit hohem Durchsatz zwischen der speicherzugeordneten AXI4-Domäne und der AXI4-Stream-Domäne ermöglicht. Der AXI Datamover bietet MM2S- und S2MM-AXI4-Stream-Kanäle, die unabhängig in einem Vollduplex-ähnlichen Verfahren arbeiten. Der AXI Datamover ist ein wichtiger Baustein für den AXI DMA-Kern und ermöglicht den Schutz von 4-Kbyte-Adressgrenzen, die automatische Burst-Partitionierung sowie die Möglichkeit, mehrere Übertragungsanfragen in eine Warteschlange zu stellen und nahezu die volle Bandbreite des AXI4-Stream-Protokolls zu nutzen. Darüber hinaus bietet der AXI Datamover eine Datenneuausrichtung auf Byte-Ebene und ermöglicht Speicherlese- und -schreibvorgänge an jeder Byte-Offset-Position.

AXI Datamover ist eine wichtige Basis-IP. Alle Xilinx DMA IPs enthalten grundsätzlich dieses Modul, das Daten in AXIS- und AXI-Formate konvertieren kann.

Fast alle DMA-IPs wie XDMA, VDMA, AXI DMA, AXI MCDMA usw. enthalten dieses Modul. Wenn diese vorhandenen DMAs von Xilinx die Anforderungen nicht erfüllen, kann der Benutzer selbst einen DMA-Controller entwerfen, um den DMA-Vorgang abzuschließen.

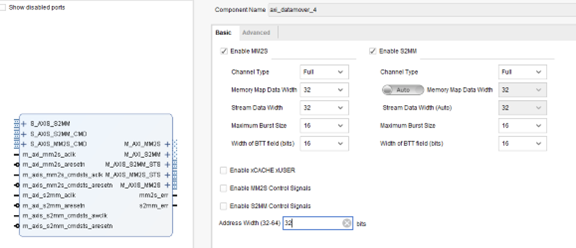

Abbildung 2-1 AXI Datamover-Schnittstelle und Konfigurationselemente

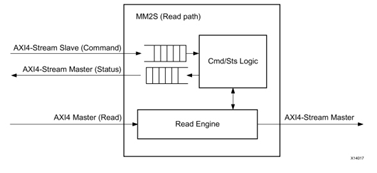

Abbildung 2-2 MM2S liest Datenkanal, liest AXI4-Schnittstellendaten und wandelt sie in AXIS-Datenausgabe um

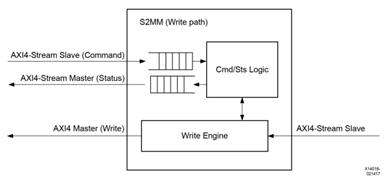

Abbildung 2-3 S2MM-Schreibdatenkanal, AXIS-Dateneingabe, in AXI4-Daten umgewandelt und in den AXI4-Schnittstellenspeicher geschrieben

Abbildung 2-4 Ressourcennutzung

2.2 AXI-DMA-Controller

Das AXI Direct Memory Access (AXI DMA) IP bietet direkten Speicherzugriff mit hoher Bandbreite zwischen Speicher und AXI4-Stream-Zielperipheriegeräten. Seine optionalen Scatter-Gather-Funktionen entlasten in prozessorbasierten Systemen auch Datenbewegungsaufgaben von der Zentraleinheit (CPU). Der Zugriff auf Initialisierungs-, Status- und Verwaltungsregister erfolgt über eine AXI4-Lite-Slave-Schnittstelle.

Kurz gesagt bietet der AXI DMA Controller eine einfache Möglichkeit, die Konvertierung (Datenspeicherung) von AXIS- und AXI4-Schnittstellen per Software (über die AXI Lite-Schnittstelle) zu steuern.

Abbildung 2-5 Internes AXI DMA-Blockdiagramm

Hier muss etwas erklärt werden: Wenn Sie den SG-DMA-Modus nicht aktivieren, sondern den reinen Registersteuerungsmodus für die AXI-DMA-IP verwenden, wird die Ressourcennutzung reduziert und die Leistung verringert (andere Xilinx-DMA-IPs sind es). ähnlich), warum wird die Leistung reduziert? Dies liegt daran, dass der Registermodus keine voreingestellten Übertragungsanweisungen unterstützt und nur auf den Abschluss einer Übertragung warten kann, bevor die nächste Übertragung gestartet wird, was die Bandbreite verringert und den CPU-Eingriff erhöht. Dieser Modus ist jedoch auch der einfachste und hängt immer noch von den Übertragungsanforderungen im Design ab.

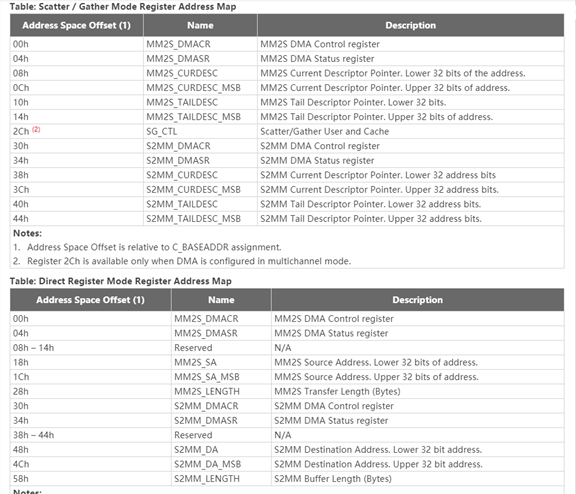

Werfen wir einen Blick auf die Registertabelle. Die Tabelle listet die Register in zwei Modi auf: SG DMA und Register DMA. Wie aus der Tabelle ersichtlich ist, ist es nicht kompliziert, AXI DMA tatsächlich zu verwenden. Ich empfehle jedoch dennoch, das direkt zu kopieren Treibercode des Xilinx SDK, Bare-Metal-Treiber und Beispiel sind ausreichend, einfach, direkt und benutzerfreundlich.

Die Tabelle in Abbildung 2-6 zeigt die relevanten Register und ihre Bedeutung im SG-Modus und im Registermodus.

Abbildung 2-7 In Bezug auf die Ressourcennutzung ist es immer noch ziemlich viel.

Abbildung 2-8 Latenz-, Leistungs- und Bandbreitendaten. Die Bandbreitendaten sind ziemlich gut. Im Allgemeinen ist es gut, 80 % zu erreichen. Das Lesen ist schneller als das Schreiben, daher liegt die Bandbreite von MM2S nahe bei 100 % und die Bandbreite von S2MM beträgt nur 75 %.

2.3 AXI-Mehrkanal-DMA

Einfach ausgedrückt handelt es sich um eine Mehrkanalversion von AXI DMA. Sie ist für die Mehrkanal-Datenübertragung mit niedriger Geschwindigkeit ausgelegt. AXI MCDMA unterstützt bis zu 16 Kanäle in beide Richtungen, und jeder Kanal ist unabhängig voneinander und ermöglicht eine unabhängige Konfiguration. Dies bietet viele langsame, multifunktionale Die Anwendung bietet eine FPGA-Lösung mit kleiner Fläche.

Da es sich bei AXI MCDMA um eine Mehrkanalversion von AXI DMA handelt, wird es nicht allzu häufig vorgestellt.

Der AXI MCDMA erleichtert die Migration großer Datenmengen und entlastet den eingebetteten Prozessor. Es fungiert als Vermittler zwischen einem eingebetteten AXI-Memory-Mapped-Subsystem und einem AXI-Streaming-Subsystem. Die MCDMA-IP ist Vollduplex, Scatter-Gather und unterstützt bis zu 16 Kanäle. Es kann als gewichtetes Round-Robin-Verfahren oder als strikte Priorität konfiguriert werden

Abbildung 2-9 AXI MCDMA-Strukturblockdiagramm

2.4 AXI-Video-DMA

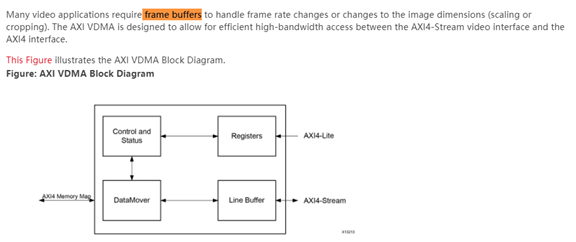

Der AXI Video Direct Memory Access (AXI VDMA)-Kern ist ein Soft-IP-Kern von Xilinx, der einen direkten Speicherzugriff mit hoher Bandbreite zwischen Speicher und Videozielperipheriegeräten vom Typ AXI4-Stream bietet. Der Kern bietet effiziente zweidimensionale DMA-Operationen mit unabhängigen asynchronen Lese- und Schreibkanaloperationen. Der Zugriff auf Initialisierungs-, Status-, Interrupt- und Verwaltungsregister erfolgt über eine AXI4-Lite-Slave-Schnittstelle.

Warum brauchen wir AXI VDMA, wenn wir AXI DMA haben? Der Grund ist aus dem folgenden Absatz ersichtlich. Die Xilinx-Videoverarbeitung verwendet hauptsächlich das AXIS-Format. In praktischen Anwendungen gibt es jedoch viele Anforderungen, die Bildrate und Cache-Frames zu ändern. Es ist nicht unmöglich, AXI DMA direkt zu verwenden, aber nicht gut mit anderen AXIS integrierbar sein Die Video-IP der Schnittstelle stimmt überein, daher wurde AXI VDMA speziell entwickelt, hauptsächlich zum Zwischenspeichern von Bildrahmen. Ein Freund möchte fragen: Kann BRAM nicht zum Zwischenspeichern verwendet werden? Nein, da jeder dem Bild entsprechende Frame sehr groß sein kann und die BRAM-Ressourcen nicht ausreichen.

Die Verwendung von AXI VDMA ähnelt der anderer DMA-IPs. Hier wird keine weitere Einführung gegeben. Wenn Sie es verwenden möchten, können Sie direkt im offiziellen Handbuch nachsehen.

3 PCIe DMA

Xilinx hat außerdem die AXI-DMA-Schnittstelle für die PCIe-Schnittstelle auf den Markt gebracht, die Xilinx DMA für PCIe entspricht. Ähnlich wie bei anderen Schnittstellen wie USB und SRIO können Benutzer auch ähnliche DMA-Lösungen entwerfen, um eine äußerst zuverlässige und flexible systeminterne Architektur aufzubauen .

Der Xilinx® LogiCORE™ DMA für PCI Express® (PCIe) implementiert einen leistungsstarken, konfigurierbaren Scatter Gather DMA zur Verwendung mit dem PCI Express Integrated Block. Das IP bietet eine optionale AXI4-MM- oder AXI4-Stream-Benutzeroberfläche

Abbildung 3-1 XDMA-Schnittstelle und Parameterkonfigurationselemente

Abbildung 3-2 Internes XDMA-Blockdiagramm

Was kann XDMA also? Das ist eine Menge. Mit diesem Modul kann Ihr PCIe-Endpunktgerät auf dem AXI-Bus aufgebaut werden und Sie erhalten eine flexible, zuverlässige und leistungsstarke System-on-Chip-Architektur.

4 Inspiration

Benutzer können ein flexibles und zuverlässiges FPGA-System aufbauen, das auf der Xilinx-DMA-Blockdiagrammarchitektur basiert und mit AXI- und AXIS-Schnittstellen verbunden ist. Wenn diese IPs die Anforderungen nicht erfüllen, können sie auch die Architektur von PCIe XDMA und anderen IPs nachahmen, um ihr eigenes System zu erstellen -On-Chip-Architektur. .