By reading the content of this article, you can clearly understand the relationship between the ability of assembly and machine language and high-level language. Although the 16-bit CPU is discussed in this article, the theory of the latest 64 or later 128 is the same, and the analogy will be fine.

Continue to general-purpose registers-assembly review (1)_luozhonghua2000's blog-CSDN blog is over, content: assembly instructions, physical addresses, CPU with 16-bit structure, 8086CPU The essential meaning of the method of giving physical addresses

assembly instructions

Control the CPU to work through assembly instructions, look at several instructions in the table

Note that in order to enable readers with a high-level language foundation to better understand the meaning of instructions, sometimes the meaning of an assembly instruction is described in two ways: text description and high-level language description. There is no case sensitivity when writing the name of an assembly instruction or a register . For example: mov ax,18 and MOV AX,18 have the same meaning: bx and BX have the same meaning.

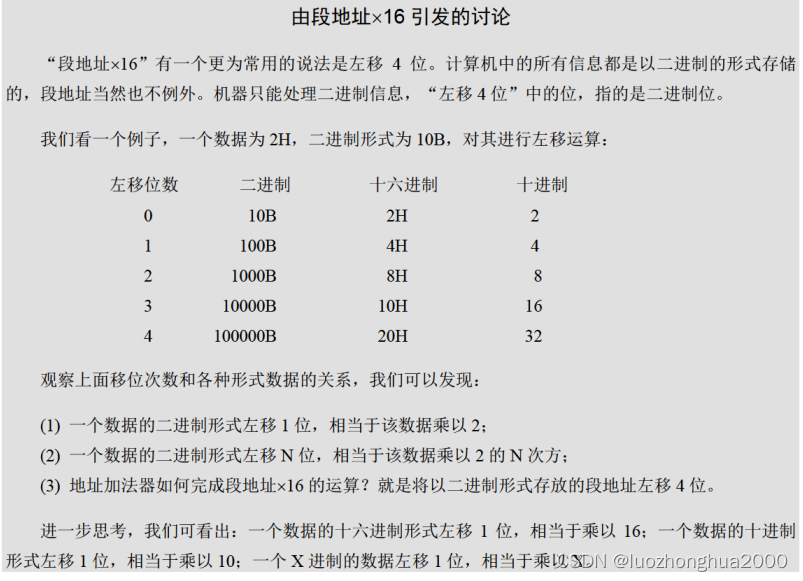

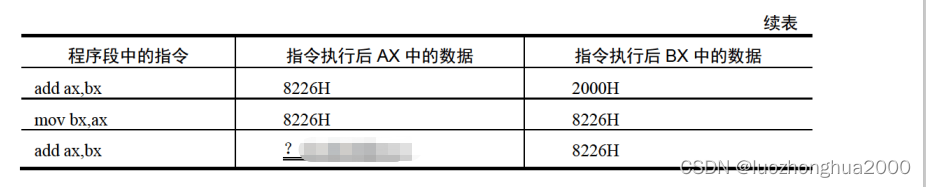

Next, look at the changes made to the data in the register after the CPU executes each instruction in the program segment listed in the table.

How much data is in AX after the instruction is executed? After thinking about it, look at the analysis. Analysis:

the last instruction add ax,bx in the program segment, the data in ax and bx are both 8226H before execution, the value obtained after adding ( converter? ) is: 1 044CH, but ax is a 16-bit register , Only 4 digits of hexadecimal data can be stored (why? Please refer to general registers - assembly review (1)_luozhonghua2000's blog - CSDN blog All registers of 8086CPU are 16 bits ), so the highest bit 1 cannot be in ax ( Why? Why is the highest bit removed? The top of the stack? ), the data in ax is: 044CH .

How much data is in AX after the instruction is executed? After thinking about it, look at the analysis

Analysis:

The last instruction in the program segment is add al,93H. Before execution, the data in al is C5H, and the value obtained after adding is: 158H, but al is an 8-bit register, which can only store two hexadecimal numbers. data, so the highest bit 1 is lost , and the data in ax is: 0058H. ( The loss here means that the carry value cannot be saved in the 8-bit register, but the CPU does not really discard the carry value, follow-up answer) Note

that al is used as an independent 8-bit register at this time, and a does not matter, the CPU thinks a and al are two irrelevant registers when executing this instruction. Don't mistakenly think that the carry generated by an instruction such as add al,93H will be stored in a, and add al,93H performs 8-bit operations.

If add ax,93H is executed, the low 8-bit carry will be stored in ah, and the CPU thinks that there is only one 16-bit register ax when executing this instruction, and the 16-bit operation is performed. It means that after add ax,93H is executed, the value in ax is: 0158H. At this time, the register used is the 16-bit register ax, add ax,93H is equivalent to adding the 16-bit data 00c5H in ax and another 16-bit data 0093H, and the result is 16-bit 0158H

When performing data transmission or operation, it should be noted that the number of bits of the two operands of the instruction should be consistent, for example:

etc. are all wrong instructions, and the reason for the error is that the digits of the two operands of the instruction are inconsistent.

practise:

physical address

We know that when the CPU accesses the memory unit, it needs to give the address of the memory unit. The storage space composed of all memory units is a one-dimensional linear space. Each memory unit has a unique address in this space. We call this unique address the physical address. The CPU sends it to the memory through the address bus. It must

be is the physical address of a memory unit. Before the CPU issues a physical address on the address bus, the physical address must be formed internally. Different CPUs can have different ways of forming physical addresses. We now discuss how the 8086 CPU internally forms the physical addresses of memory cells.

16-bit CPU

We say that the previous generation CPU (8080, 8085) of the 8086CPU is an 8-bit machine, while the 8086 is a 16-bit machine. It can also be said that the 8086 is a CPU with a 16-bit structure. So what is a CPU with a 16-bit structure?

In a nutshell, a 16-bit structure (common expressions such as a 16-bit machine and a word length of 16 bits have the same meaning as a 16-bit structure) describes a CPU with the following structural characteristics .

The 8086 is a CPU with a 16-bit structure, which means that within the 8086, the maximum length of information that can be processed, transmitted, and temporarily stored at one time is 16 bits. Before the address of the memory unit is sent to the address bus, it must be processed, transmitted, and temporarily stored in the CPU. For a 16-bit CPU, 16-bit addresses can be processed, transmitted, and temporarily stored at one time.

The latest 64-bit cpu analogy

8086CPU gives the method of physical address

8086CPU has a 20-bit address bus, which can transmit 20-bit addresses and achieve 1MB addressing capability. The 8086CPU is also a 16-bit structure, and the internal one-time processing, transmission, and temporary storage addresses are 16 bits. From the internal structure of 8086CPU, if the address is simply sent from the inside, then it can only send 16-bit address, and the addressing capability shown is only 64KB.

8086CPU adopts a method of synthesizing two 16-bit addresses internally to form a 20-bit physical address. The logical structure of 8086CPU-related components is shown in Figure 1.

As shown in Figure 1, when the 8086CPU wants to read and write memory:

1) The relevant components in the CPU provide two 16-bit addresses, one is called the segment address and the other is called the offset address;

2) The segment address and the offset address are sent to a component called an address adder through the internal bus :

3) The address adder synthesizes two 16-bit addresses into a 20-bit physical address:

4) The address adder sends the 20-bit physical address to the input and output control circuit through the internal bus:

5) The input and output control circuit converts the 20-bit The physical address is sent to the address bus;

6) The 20-bit physical address is sent to the memory by the address bus.

The address adder adopts the method of physical address=segment address x16+offset address to synthesize the physical address with the segment address and the offset address. For example, 8086CPU wants to access the memory unit whose address is 123C8H. At this time, the working process of the address adder is shown in Figure 2 (the data in the figure are all expressed in hexadecimal).