1.14.1 Commonly used ARM instructions 1: data processing instructions

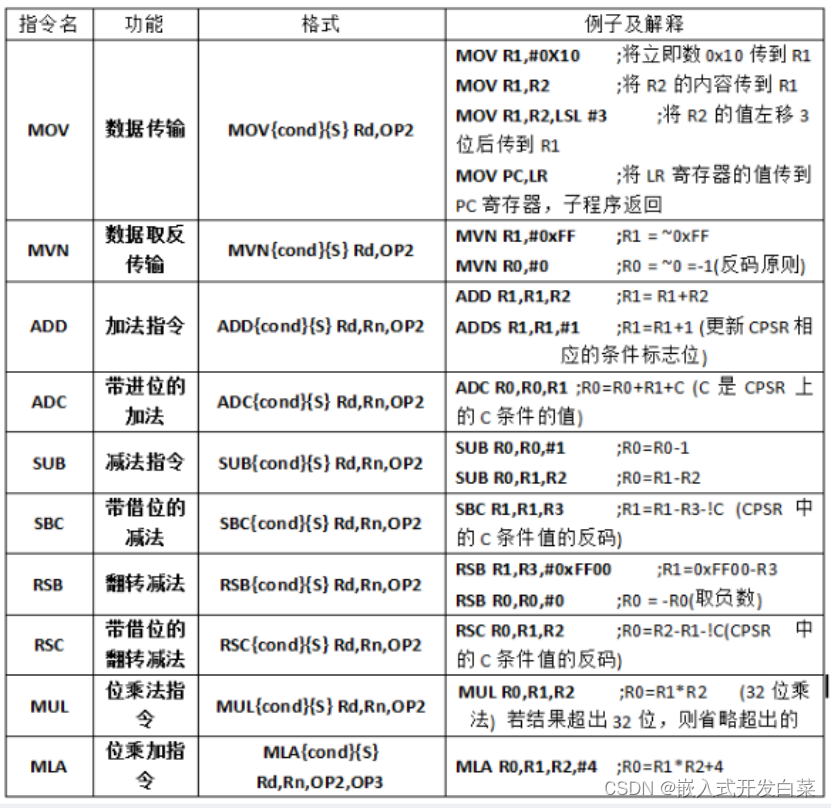

Data transfer instruction mov mvn

Arithmetic instructions add sub rsb adc sbc rsc

logic instruction and orr eor bic

Comparison command cmp cmn tst teq

Multiplication instructions mvl mla umull umlal smull smlal

leading zero count clz

Data transfer instructions:

mov r1, r0 @ data transfer between two registers

mov r1, #0xff @ assign the immediate value to r1

The usage of mvn and mov is the same, the difference is that mvn is passed after bitwise inversion.

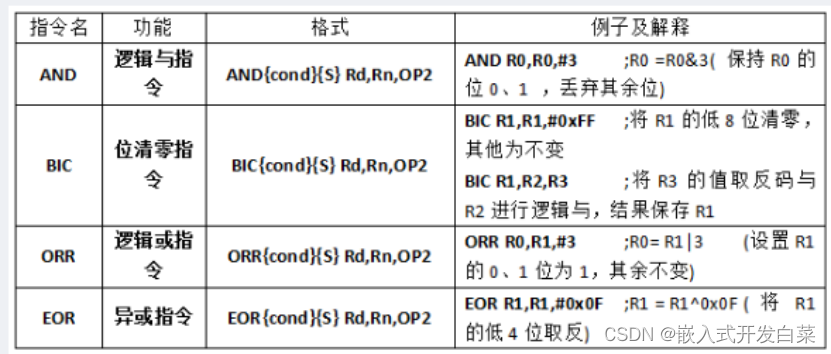

Logic instruction:

and: logic and

orr: logical or

eor: logical exclusive or

bic: bit clear instruction bic r0, r1, #0x1f @clear bit0~bit4 of the number in r1 and assign it to r0

Comparison instruction: The comparison instruction is used to compare the numbers in two registers.

(Note: The comparison instruction can affect the flag bit in cpsr without adding the s suffix. The reason for this is to focus on the process, not the result like mov. For example, after the sentence cmp r0, r1 is executed, the next sentence You can know that the above sentence is equal by the z bit in cpsr being 1.)

cmp: cmp r0, r1 is equivalent to sub r2, r0, r1 (r2 = r0 - r1)

cmn: cmn r0, r1 is equivalent to add r0, r1

tst: tst r0, #0xf @Test whether bit0~bit3 of r0 are all 0

tick:

1.14.2 Commonly used ARM instructions 2: CPSR access instructions

mrs & msr

mrs is used to read cpsr/spsr, msr is used to write cpsr/spsr

The CPSR register is special and requires special instruction access, which are mrs and msr.

1.14.3 Commonly used ARM instruction 3: jump (branch) instruction

b & bl & bx

b Jump directly (if it is not opened, it will be returned)

bl branch and link, put the return address into lr before jumping, so as to return, so as to be used for function calls

The bx jump switches to ARM mode at the same time, which is generally used for exception handling jumps.

1.14.4 Commonly used ARM instructions 4: memory access instructions

ldr/str & ldm/stm & swp (memory and register swap instructions)

Single word/halfword/byte access to ldr/str

Multi-word batch access ldm/stm m (multiple multiple)

swp r1, r2, [r0] Read r0 as the value in the address into r1, and write the value in r2 back into r0.

swp r1, r1, [r0] Read r0 as the value in the address into r1, and write the original value of r1 back into r0.

1.14.5 Commonly used ARM instructions 5

swi(software interrupt)

Soft interrupt instructions are used to implement system calls in the OS

1.14.6 Immediate data in ARM assembly

ARM instructions are all 32-bit, except for instruction flags and operation flags, they can only have immediate values with a small number of digits. Therefore, immediate data can be divided into legal and illegal.

Legal immediate value: After any number of shifts, the non-zero part can be represented by 8 bits, which is the legal immediate value.

Legal immediate data: 0x000000ff 0x00ff0000 0xf000000f

Illegal immediate value: 0x000001ff

For more embedded study notes and practical projects, click here to get free