DMA es acceso directo a la memoria. En los sistemas FPGA, existen varios requisitos de DMA de uso común:

1. No hay ningún PS dentro del PL (aquí la CPU se denomina colectivamente PS) para intervenir continuamente en el movimiento de datos. Las formas de interfaz comunes son AXIS y AXI, AXI y AXI;

2. Para ZYNQ, mover datos entre PL y PS es más fácil de entender, pertenece a la interfaz interna de un solo chip, para otras interfaces como PCIe, será un poco más complicado y pertenece a la interfaz entre múltiples chips;

Explore el propósito del enfoque DMA:

1. Comprender los métodos de movimiento de datos dentro del chip, las interfaces comunes y los métodos de implementación de DMA;

2. Comprender los métodos de movimiento de datos entre chips, las interfaces comunes y los métodos de implementación de DMA;

A través de esta comprensión, se puede establecer una estructura marco para la migración de datos del sistema. Si surge una demanda similar, todo lo que realmente se necesita es llamar a los módulos existentes para implementarla.

Este artículo comienza con una introducción a cada IP DMA de Xilinx, principalmente desde la perspectiva de las interfaces.

1 AXI4 A AXI4

1.1 Controlador DMA central AXI

AXI CDMA proporciona acceso directo a memoria (DMA) de gran ancho de banda entre una dirección de origen asignada en memoria y una dirección de destino asignada en memoria utilizando el protocolo AXI4. Se puede utilizar una función Scatter Gather (SG) opcional para descargar tareas de control y secuenciación de la CPU del sistema. Se accede a los registros de inicialización, estado y control a través de una interfaz esclava AXI4-Lite, adecuada para el procesador Xilinx MicroBlaze™.

¿Por qué se llama CDMA? En realidad, es para manejar la transmisión de datos dentro de la memoria de la interfaz AXI montada en la CPU. El escenario típico es MicroBlaze. ¿Por qué no decir ZYNQ? El AXI de ZYNQ se monta directamente dentro de la CPU y no requiere un DMA para controlarlo. Si es necesario, copie el software directamente y la acción de copia iniciará una operación AXI DMA internamente. Pero si ZYNQ quiere usar DDR en el lado PL, debe usar CDMA para operar, porque ZYNQ no tiene una interfaz AXI Master, solo SLAVE (aquí estamos hablando de interfaces HP de alto rendimiento, no de interfaces GP de baja velocidad) .

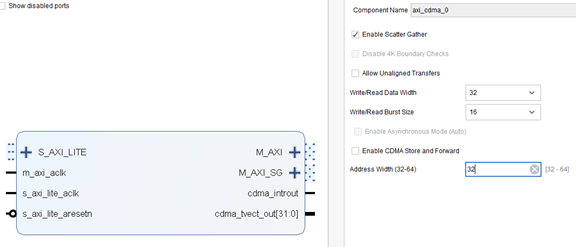

Figura 1-1 Interfaz AXI CDMA y opciones de parámetros, donde S_AXI_LITE está conectado a la CPU de control principal, M_AXI está conectado a la memoria y M_AXI_SG está conectado a la memoria (utilizado para almacenar el descriptor dma en modo SG DMA)

Figura 1-2 Diagrama de bloques de la estructura interna de CMDA

Figura 1-3 Diagrama de bloques ZYNQ, solo AXI SLAVE de alto rendimiento, sin MASTER

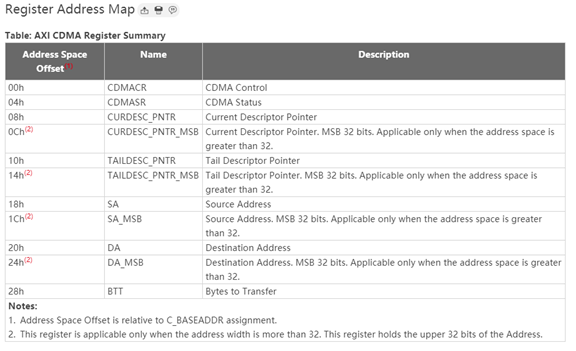

Echemos un vistazo a los registros internos. Esto en realidad es más intuitivo y le dice al usuario cómo configurar el módulo. A partir del método de configuración, podemos simplemente estimar la complejidad de usar el módulo. Desde la definición del registro, el control, la detección de estado, el puntero descriptor de SG DMA, la dirección inicial, la dirección de destino y la longitud de DMA simple no son complicados de usar. Luego, se recomienda copiar directamente el código del controlador lateral ZYNQ de xilinx con el código de software correspondiente, y luego podrá usarlo con una ligera modificación.

Finalmente, echemos un vistazo a la ocupación de recursos. La ocupación de recursos es proporcional al ancho de bits. Normalmente, con un ancho de bits de datos de 64 bits, ocupa alrededor de 1500 LUT y 2500 FF. Desde mi perspectiva, este recurso es bastante bueno.

Figura 1-4 Uso de recursos

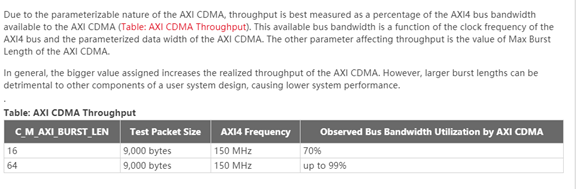

Figura 1‑5 Eficiencia de transmisión y ancho de banda

2 Transmisión AXI a AXI4

2.1 Administrador de datos AXI

AXI Datamover es una IP de infraestructura de interconexión clave que permite una transferencia de datos de alto rendimiento entre el dominio mapeado de memoria AXI4 y el dominio AXI4-Stream. El AXI Datamover proporciona canales MM2S y S2MM AXI4-Stream que funcionan de forma independiente en un método similar al dúplex completo. AXI Datamover es un componente clave para el núcleo AXI DMA y permite protección de límites de direcciones de 4 kbytes, partición automática en ráfagas, además de brindar la capacidad de poner en cola múltiples solicitudes de transferencia utilizando casi todas las capacidades de ancho de banda del protocolo AXI4-Stream. Además, AXI Datamover proporciona realineación de datos a nivel de bytes, lo que permite lecturas y escrituras de memoria en cualquier ubicación de desplazamiento de bytes.

AXI Datamover es una IP básica importante. Todas las IP Xilinx DMA incluyen básicamente este módulo, que puede convertir datos en formatos AXIS y AXI.

Casi todos los DMA IP como XDMA, VDMA, AXI DMA, AXI MCDMA, etc. incluyen este módulo. Si estos DMA existentes de xilinx no pueden satisfacer las necesidades, entonces el usuario puede diseñar un controlador DMA por sí mismo para completar la operación DMA.

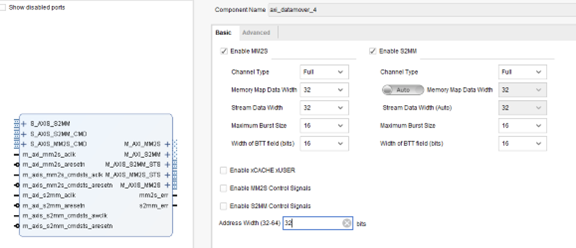

Figura 2‑1 Interfaz de AXI Datamover y elementos de configuración

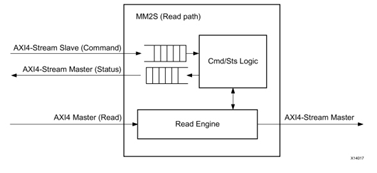

Figura 2-2 MM2S leyendo el canal de datos, leyendo datos de la interfaz AXI4 y convirtiéndolos en salida de datos AXIS

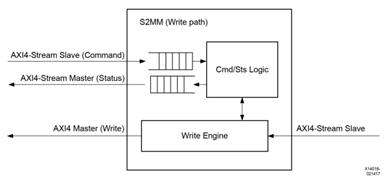

Figura 2‑3 Canal de datos de escritura S2MM, entrada de datos AXIS, convertidos en datos AXI4 y escritos en la memoria de la interfaz AXI4

Figura 2-4 Uso de recursos

2.2 Controlador AXI DMA

La IP de acceso directo a la memoria de AXI (AXI DMA) proporciona acceso directo a la memoria de gran ancho de banda entre la memoria y los periféricos de destino de tipo AXI4-Stream. Sus capacidades opcionales de recopilación de dispersión también descargan tareas de movimiento de datos de la Unidad Central de Procesamiento (CPU) en sistemas basados en procesadores. Se accede a los registros de inicialización, estado y gestión a través de una interfaz esclava AXI4-Lite.

En resumen, AXI DMA Controller proporciona una forma sencilla de controlar mediante software la conversión (almacenamiento de datos) de las interfaces AXIS y AXI4 (a través de la interfaz AXI Lite).

Figura 2‑5 Diagrama de bloques interno de AXI DMA

Es necesario explicar algo aquí: si elige no habilitar el modo SG DMA, pero usa el modo de control de registro puro, para la IP AXI DMA, el uso de recursos se reducirá y el rendimiento se reducirá (otras IP Xilinx DMA son similar), ¿por qué se reducirá el rendimiento? Esto se debe a que el modo de registro no admite instrucciones de transferencia preestablecidas y solo puede esperar a que se complete una transferencia antes de comenzar la siguiente, lo que reduce el ancho de banda y aumenta la intervención de la CPU. Sin embargo, este modo también es el más simple y aún depende de los requisitos de transmisión del diseño.

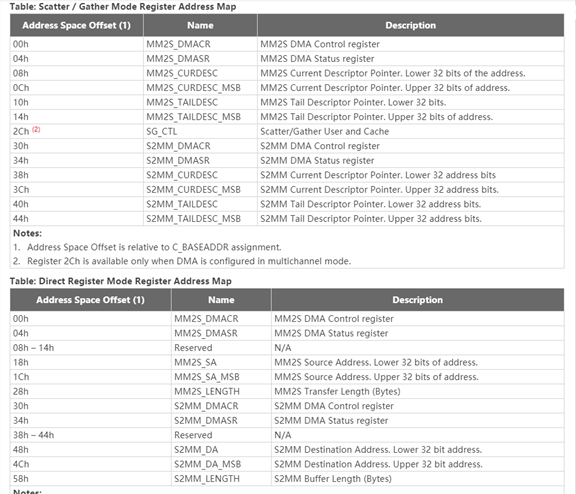

Echemos un vistazo a la tabla de registros. La tabla enumera los registros en dos modos: SG DMA y registro DMA. Como puede verse en la tabla, no es complicado usar AXI DMA. Sin embargo, todavía recomiendo copiar directamente el El código del controlador de Xilinx SDK., el controlador básico y el ejemplo son suficientes, simples, directos y fáciles de usar.

La tabla de la Figura 2-6 muestra los registros relevantes y sus significados en modo SG y modo registro.

Figura 2-7 En términos de uso de recursos, todavía es bastante.

Figura 2-8 Datos de latencia, rendimiento y ancho de banda. Los datos de ancho de banda son bastante buenos. En términos generales, es bueno alcanzar el 80%. La lectura es más rápida que la escritura, por lo que el ancho de banda de MM2S está cerca del 100% y el ancho de banda de S2MM es sólo del 75%.

2.3 DMA multicanal AXI

En pocas palabras, es una versión multicanal de AXI DMA. Está diseñada para hacer frente a la transmisión de datos multicanal a baja velocidad. AXI MCDMA admite hasta 16 canales en ambas direcciones, y cada canal es independiente entre sí y permite la configuración independiente, lo que proporciona muchas aplicaciones multifuncionales de baja velocidad que proporcionan una solución FPGA de área pequeña.

Dado que AXI MCDMA es una versión multicanal de AXI DMA, no se presentará demasiado.

AXI MCDMA facilita la migración de datos de gran tamaño, descargando la tarea del procesador integrado. Actúa como intermediario entre un subsistema integrado AXI Memory-Mapped y un subsistema AXI Streaming. El MCDMA IP es full-duplex, scatter-gather y admite hasta 16 canales. Se puede configurar como round robin ponderado o prioridad estricta.

Figura 2‑9 Diagrama de bloques estructural de AXI MCDMA

2.4 DMA de vídeo AXI

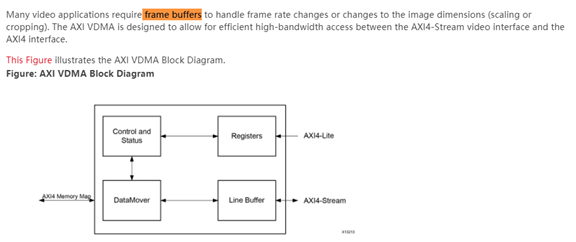

El núcleo AXI Video Direct Memory Access (AXI VDMA) es un núcleo IP Xilinx suave que proporciona acceso directo a la memoria de gran ancho de banda entre la memoria y los periféricos de destino de video tipo AXI4-Stream. El núcleo proporciona operaciones DMA bidimensionales eficientes con operación de canal de lectura y escritura asincrónica independiente. Se accede a los registros de inicialización, estado, interrupción y gestión a través de una interfaz esclava AXI4-Lite.

¿Por qué necesitamos AXI VDMA cuando tenemos AXI DMA? La razón se puede ver en el siguiente párrafo. El procesamiento de video Xilinx usa principalmente el formato AXIS. Sin embargo, en aplicaciones prácticas, hay muchas necesidades para cambiar la velocidad de cuadros y los cuadros de caché. No es imposible usar AXI DMA directamente, pero no estar bien integrado con otros AXIS La IP de video de la interfaz coincide, por lo que AXI VDMA fue desarrollado especialmente, principalmente para almacenar en caché cuadros de imágenes. Un amigo quiere preguntar, ¿no se puede usar BRAM para el almacenamiento en caché? No, porque cada fotograma correspondiente a la imagen puede ser muy grande y los recursos BRAM no son suficientes.

El uso de AXI VDMA es similar al de otras IP DMA. No se dará más introducción aquí. Si desea utilizarlo, puede consultar directamente el manual oficial.

3 PCIe DMA

Xilinx también ha lanzado la interfaz AXI DMA para la interfaz PCIe, que corresponde a Xilinx DMA para PCIe. De manera similar, al igual que otras interfaces como USB y SRIO, los usuarios también pueden diseñar soluciones DMA similares para construir una arquitectura interna de sistema altamente confiable y flexible. .

Xilinx® LogiCORE™ DMA para PCI Express® (PCIe) implementa un DMA Scatter Gather configurable y de alto rendimiento para su uso con el bloque integrado PCI Express. El IP proporciona una interfaz de usuario opcional AXI4-MM o AXI4-Stream

Figura 3‑1 Elementos de configuración de parámetros y interfaz XDMA

Figura 3‑2 Diagrama de bloques interno de XDMA

Entonces, ¿qué puede hacer XDMA? Eso es mucho. Con este módulo, su dispositivo PCIe Endpoint se puede construir en el bus AXI y tendrá una arquitectura de sistema en chip flexible, confiable y de alto rendimiento.

4 inspiración

Los usuarios pueden construir un sistema FPGA flexible y confiable basado en la arquitectura del diagrama de bloques Xilinx DMA e interconectado con las interfaces AXI y AXIS. Si estas IP no pueden cumplir con los requisitos, también pueden imitar la arquitectura de PCIe XDMA y otras IP para construir su propio sistema. -arquitectura en chip. .