Le DMA est un accès direct à la mémoire. Dans les systèmes FPGA, il existe plusieurs exigences DMA couramment utilisées :

1. Il n'y a pas de PS à l'intérieur du PL (le CPU est collectivement appelé PS ici) pour intervenir en permanence dans le déplacement des données. Les formes d'interface courantes sont AXIS et AXI, AXI et AXI ;

2. Le déplacement des données entre PL et PS est plus facile à comprendre pour ZYNQ. Il appartient à l'interface interne d'une seule puce. Pour d'autres interfaces telles que PCIe, ce sera légèrement plus compliqué et appartient à l'interface entre plusieurs puces ;

Découvrez l’objectif de l’approche DMA :

1. Comprendre les méthodes de déplacement des données au sein de la puce, les interfaces communes et les méthodes de mise en œuvre du DMA ;

2. Comprendre les méthodes de déplacement des données entre les puces, les interfaces communes et les méthodes de mise en œuvre du DMA ;

Grâce à cette compréhension, une structure-cadre pour la migration des données du système peut être établie. Si une demande similaire se présente, il suffit en réalité d'appeler les modules existants pour la mettre en œuvre.

Cet article commence par une introduction à chaque IP DMA de Xilinx, principalement du point de vue des interfaces.

1 AXI4 À AXI4

1.1 Contrôleur DMA central AXI

L'AXI CDMA fournit un accès direct à la mémoire (DMA) à large bande passante entre une adresse source mappée en mémoire et une adresse de destination mappée en mémoire à l'aide du protocole AXI4. Une fonctionnalité facultative Scatter Gather (SG) peut être utilisée pour décharger les tâches de contrôle et de séquençage du processeur du système. Les registres d'initialisation, d'état et de contrôle sont accessibles via une interface esclave AXI4-Lite, adaptée au processeur Xilinx MicroBlaze™.

Pourquoi s'appelle-t-il CDMA ? Il s'agit en fait de gérer la transmission de données au sein de la mémoire d'interface AXI montée sur le CPU. Le scénario typique est MicroBlaze. Pourquoi ne pas dire ZYNQ ? L'AXI de ZYNQ est directement monté à l'intérieur du CPU et ne nécessite pas de DMA pour le contrôler. Si nécessaire, copiez directement le logiciel et l'action de copie lancera une opération AXI DMA en interne. Mais si ZYNQ veut utiliser du DDR côté PL, il doit utiliser CDMA pour fonctionner, car ZYNQ n'a pas d'interface AXI Master, seulement SLAVE (on parle ici d'interfaces HP hautes performances, pas d'interfaces GP bas débit) .

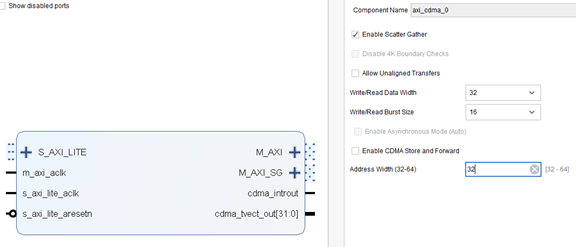

Figure 1-1 Interface AXI CDMA et options de paramètres, où S_AXI_LITE est connecté au CPU de contrôle principal, M_AXI est connecté à la mémoire et M_AXI_SG est connecté à la mémoire (utilisé pour stocker le descripteur dma en mode SG DMA)

Figure 1-2 Schéma fonctionnel de la structure interne du CMDA

Figure 1-3 Schéma fonctionnel ZYNQ, uniquement AXI SLAVE hautes performances, pas de MASTER

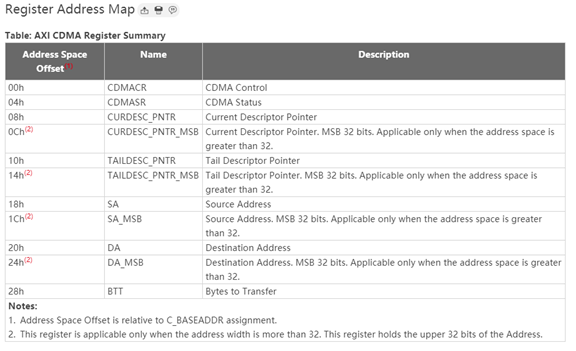

Jetons un coup d'œil aux registres internes. C'est en fait plus intuitif et indique à l'utilisateur comment configurer le module. A partir de la méthode de configuration, nous pouvons simplement estimer la complexité d'utilisation du module. À partir de la définition du registre, le contrôle, la détection d'état, le pointeur de descripteur du SG DMA, l'adresse de départ, l'adresse cible et la longueur du DMA simple ne sont pas compliqués à utiliser. Ensuite, il est recommandé que le code du logiciel correspondant copie directement le code du pilote côté ZYNQ de Xilinx, puis vous pouvez l'utiliser avec une légère modification.

Enfin, examinons l'occupation des ressources. L'occupation des ressources est proportionnelle à la largeur de bits. Généralement, sous une largeur de bits de données de 64 bits, elle occupe environ 1 500 LUT et 2 500 FF. De mon point de vue, cette ressource est plutôt bonne.

Figure 1-4 Utilisation des ressources

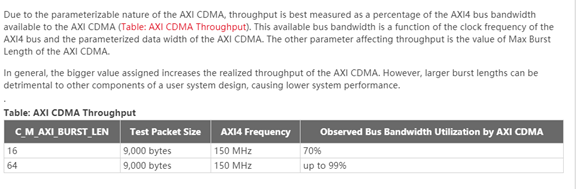

Figure 1‑5 Efficacité de transmission et bande passante

2 Flux AXI vers AXI4

2.1 DataMover AXI

L'AXI Datamover est une IP d'infrastructure d'interconnexion clé qui permet un transfert de données à haut débit entre le domaine mappé en mémoire AXI4 et le domaine AXI4-Stream. L'AXI Datamover fournit des canaux AXI4-Stream MM2S et S2MM qui fonctionnent indépendamment selon une méthode de type duplex intégral. L'AXI Datamover est un élément clé du cœur AXI DMA et permet une protection des limites d'adresse de 4 Ko, un partitionnement automatique en rafale, ainsi que la possibilité de mettre en file d'attente plusieurs demandes de transfert en utilisant presque toutes les capacités de bande passante du protocole AXI4-Stream. De plus, l'AXI Datamover fournit un réalignement des données au niveau de l'octet, permettant des lectures et des écritures en mémoire vers n'importe quel emplacement de décalage d'octet.

AXI Datamover est une IP de base importante. Toutes les IP Xilinx DMA incluent essentiellement ce module, qui peut convertir les données aux formats AXIS et AXI.

Presque toutes les IP DMA telles que XDMA, VDMA, AXI DMA, AXI MCDMA, etc. incluent ce module. Si ces DMA existants de xilinx ne peuvent pas répondre aux besoins, alors l'utilisateur peut concevoir lui-même un contrôleur DMA pour terminer l'opération DMA.

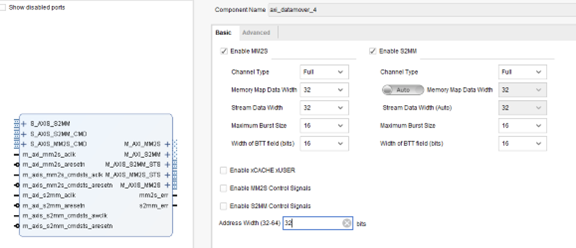

Figure 2‑1 Interface et éléments de configuration de l'AXI Datamover

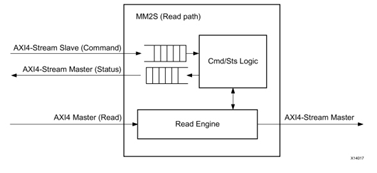

Figure 2-2 Canal de données de lecture MM2S, lecture des données de l'interface AXI4, conversion en sortie de données AXIS

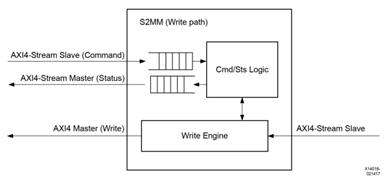

Figure 2‑3 Canal de données d'écriture S2MM, entrée de données AXIS, converties en données AXI4 et écrites dans la mémoire de l'interface AXI4

Figure 2-4 Utilisation des ressources

2.2 Contrôleur AXI-DMA

L'IP AXI Direct Memory Access (AXI DMA) fournit un accès mémoire direct à large bande passante entre la mémoire et les périphériques cibles de type AXI4-Stream. Ses capacités facultatives de collecte de données déchargent également les tâches de déplacement de données de l'unité centrale de traitement (CPU) dans les systèmes basés sur un processeur. Les registres d'initialisation, d'état et de gestion sont accessibles via une interface esclave AXI4-Lite.

En bref, AXI DMA Controller fournit un moyen simple pour la conversion (stockage de données) des interfaces AXIS et AXI4 d'être contrôlée par logiciel (via l'interface AXI Lite).

Figure 2‑5 Schéma fonctionnel interne de l'AXI DMA

Quelque chose doit être expliqué ici : si vous choisissez de ne pas activer le mode SG DMA, mais d'utiliser le mode de contrôle de registre pur, pour l'IP AXI DMA, l'utilisation des ressources sera réduite et les performances seront réduites (d'autres IP Xilinx DMA sont similaire), pourquoi les performances seront-elles réduites ? En effet, le mode registre ne prend pas en charge les instructions de transfert prédéfinies et ne peut qu'attendre la fin d'un transfert avant de démarrer le transfert suivant, ce qui réduit la bande passante et augmente l'intervention du processeur. Cependant, ce mode est également le plus simple et dépend toujours des exigences de transmission lors de la conception.

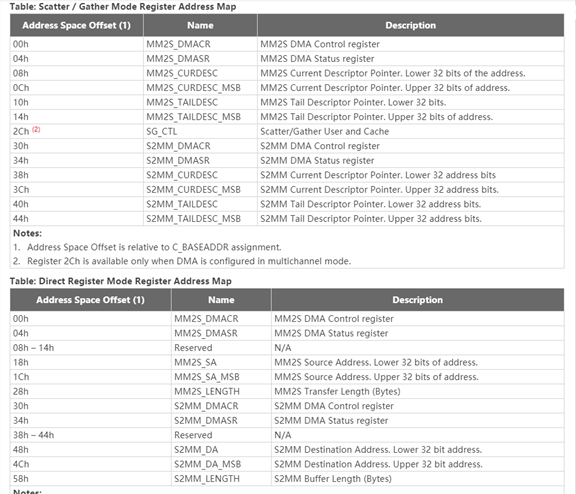

Jetons un coup d'oeil à la table des registres. La table répertorie les registres en deux modes : SG DMA et registre DMA. Comme le montre le tableau, il n'est pas compliqué d'utiliser réellement AXI DMA. Cependant, je recommande quand même de copier directement le Le code du pilote du SDK Xilinx, le pilote nu et l'exemple suffisent, simples, directs et faciles à utiliser.

Le tableau de la figure 2-6 montre les registres pertinents et leurs significations en mode SG et en mode registre.

Figure 2-7 En termes d'utilisation des ressources, cela représente encore beaucoup.

Figure 2-8 Données de latence, de performances et de bande passante. Les données de bande passante sont plutôt bonnes. De manière générale, il est bon d'atteindre 80 %. La lecture est plus rapide que l'écriture, donc la bande passante de MM2S est proche de 100 %, et la bande passante de S2MM ne représente que 75 %.

2.3 DMA multicanal AXI

En termes simples, il s'agit d'une version multicanal d'AXI DMA. Il est conçu pour gérer la transmission de données multicanal à faible vitesse. AXI MCDMA prend en charge jusqu'à 16 canaux dans les deux sens, et chaque canal est indépendant l'un de l'autre et permet une configuration indépendante.Cela fournit de nombreuses solutions FPGA à faible vitesse et multifonctionnelles.

Étant donné qu'AXI MCDMA est une version multicanal d'AXI DMA, elle ne sera pas trop présentée.

L'AXI MCDMA facilite la migration de données volumineuses, en déchargeant la tâche du processeur intégré. Il sert d'intermédiaire entre un sous-système intégré AXI Memory-Mapped et un sous-système AXI Streaming. L'IP MCDMA est en duplex intégral, à diffusion groupée et prend en charge jusqu'à 16 canaux. Il peut être configuré en round robin pondéré ou en priorité stricte

Figure 2‑9 Schéma fonctionnel structurel AXI MCDMA

2.4 DMA vidéo AXI

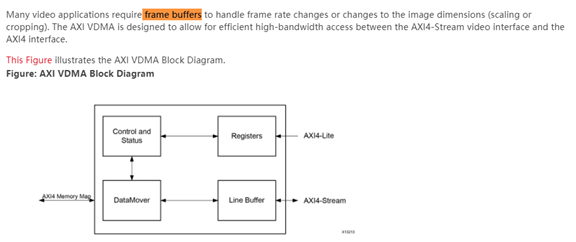

Le cœur AXI Video Direct Memory Access (AXI VDMA) est un cœur IP Xilinx logiciel qui fournit un accès mémoire direct à large bande passante entre la mémoire et les périphériques cibles vidéo de type AXI4-Stream. Le noyau fournit des opérations DMA bidimensionnelles efficaces avec un fonctionnement de canal de lecture et d'écriture asynchrone indépendant. Les registres d'initialisation, d'état, d'interruption et de gestion sont accessibles via une interface esclave AXI4-Lite.

Pourquoi avons-nous besoin d’AXI VDMA alors que nous avons AXI DMA ? La raison peut être vue dans le paragraphe suivant. Le traitement vidéo Xilinx utilise principalement le format AXIS. Cependant, dans les applications pratiques, il existe de nombreux besoins pour modifier la fréquence d'images et les images du cache. Il n'est pas impossible d'utiliser directement AXI DMA, mais ce n'est pas possible. être bien intégré avec d'autres AXIS L'IP vidéo de l'interface correspond, donc AXI VDMA a été spécialement développé, principalement pour mettre en cache les images d'image. Un ami veut demander, BRAM ne peut-il pas être utilisé pour la mise en cache ? Non, car chaque frame correspondant à l'image peut être très volumineuse et les ressources BRAM ne suffisent pas.

L'utilisation d'AXI VDMA est similaire à celle des autres IP DMA. Aucune autre introduction ne sera donnée ici. Si vous souhaitez l'utiliser, vous pouvez directement consulter le manuel officiel.

3 PCIe DMA

Xilinx a également lancé l'interface AXI DMA pour l'interface PCIe, qui correspond à Xilinx DMA pour PCIe. De même, à l'instar d'autres interfaces telles que USB et SRIO, les utilisateurs peuvent également concevoir des solutions DMA similaires pour construire une architecture interne de système hautement fiable et flexible. .

Le Xilinx® LogiCORE™ DMA pour PCI Express® (PCIe) implémente un DMA Scatter Gather configurable et hautes performances à utiliser avec le bloc intégré PCI Express. L'IP fournit une interface utilisateur AXI4-MM ou AXI4-Stream en option

Figure 3‑1 Éléments de configuration de l'interface et des paramètres XDMA

Figure 3‑2 Schéma fonctionnel interne du XDMA

Alors, que peut faire XDMA ? C'est beaucoup. Avec ce module, votre périphérique PCIe Endpoint peut être construit sur le bus AXI et vous disposerez d'une architecture système sur puce flexible, fiable et hautes performances.

4 inspirations

Les utilisateurs peuvent créer un système FPGA flexible et fiable basé sur l'architecture de schéma fonctionnel Xilinx DMA et interconnecté avec les interfaces AXI et AXIS. Si ces IP ne peuvent pas répondre aux exigences, ils peuvent également imiter l'architecture de PCIe XDMA et d'autres IP pour construire leur propre système. Architecture sur puce. .