嵌入式开发的通信协议

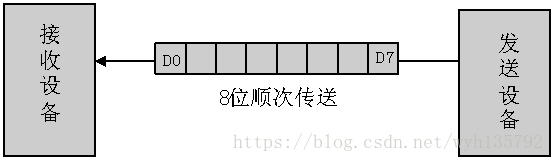

串行通信

将数据字节分成一位一位的形式在一条传输线上逐位地发送。

优点:成本低,控制复杂

异步通信

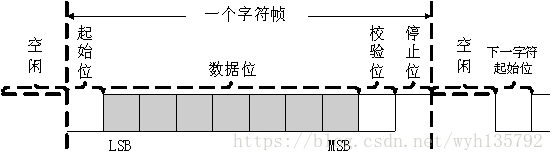

异步通信是指通信的发送与接收设备使用各自的时钟控制数据的发送和接收过程。为使双方的收发协调,要求发送和接收设备的时钟尽可能一致。 异步通信的两个关键:

第一,数据单元——帧,它是双方约定好的数据格式;

第二,波特率,它决定了‘帧’里每一位的时间长度。

异步通信的特点:不要求收发双方时钟的严格一致,实现容易,设备开销较小,但每个字符要附加2~3位用于起止位,各帧之间还有间隔,因此传输效率不高。

注:波特率表示每秒传送的字符数,是UART协议中的一个关键数据,即发送数据的速度;

发送器和接受器的波特率应该匹配,通常,我们将波特率定为9600或115200。

同步通信

在数据传输过程中,需要一根时钟线同步,如 IIC总线,SPI总线 。

UART

定义

UART是一种通用串行数据总线,用于异步通信。该总线双向通信,可以实现全双工传输和接收。

UART通信方式

1.起始位:先发出一个逻辑”0”的信号,表示传输字符的开始。

2.数据位:紧接着起始位之后。资料位的个数可以是4、5、6、7、8等,构成一个字符。通常采用ASCII码。从最低位开始传送,靠时钟定位。

3.奇偶校验位:资料位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验),以此来校验资料传送的正确性。

4.停止位:它是一个字符数据的结束标志。可以是1位、1.5位、2位的高电平。

5.空闲位:处于逻辑“1”状态,表示当前线路上没有资料传送。

UART与COM口的区别

【1】UART,COM指的物理接口形式(硬件), 而TTL、RS-232是指的电平标准(电信号).

【2】UART有4个pin(VCC, GND, RX, TX), 用的TTL电平, 低电平为0(0V),高电平为1(3.3V或以上)。

COM口是我们台式机上面常用的口(下图),9个pin, 用的RS232电平, 它是负逻辑电平,它定义+5~+12V为低电平,而-12~-5V为高电平

【3】接设备的时候,一般只接GND RX TX。不会接Vcc或者+3.3v的电源线,避免与目标设备上的供电冲突。

【4】我们常用UART口进行调试,但是UART的数据要传到电脑上分析就要匹配电脑的接口,通常我们电脑使用接口有COM口和USB口(最终在电脑上是一个虚拟的COM口),但是要想连上这两种接口都要需要进行硬件接口转换和电平转换。

(1) 如果连接电脑COM口, 需要一个类似下图的转换小板, 它实现了TTL电平和RS232电平互转, 我之前使用过, 但是现在很少用了。

如果要连接USB接口, 需要类似下面的小板, 它实现了TTL电平和USB电平的转换, 这种使用的较多。

SPI

定义

SPI是一种高速的,全双工,同步的通信总线;

全双工:可以同时接收和发送数据。

同步:接收端和发送端必须在同一时刻接收和发送。

简单的主从SPI连接图

接口

SCLK:串行时钟,用来同步数据传输,由主机输出

MISO:主机输入从机输出(Master In Slave Out)

MOSI:主机输出从机输入(Master Out Slave In)

CS:片选线,低电平有效,由主机输出

在SPI总线上,某一时刻可以出现多个从机,但只能存在一个主机,主机通过片选线来确定要通信的从机。这就要求从机的MISO口具有三态特性,使得该口线在器件未被选通时表现为高阻抗。

SPI的相位和极性

在SPI操作中,最重要的两项设置就是时钟极性(CPOL)和时钟相位(CPHA)。

时钟极性设置时钟空闲时的电平,时钟相位设置读取数据和发送数据的时钟沿。

主机和从机的发送数据是同时完成的,两者的接收数据也是同时完成的。所以为了保证主从机正确通信,应使得它们的SPI具有相同的时钟极性和时钟相位。

CPOL极性:

当CPOL为0时,SCLK在空闲时为低电平,有效时即为高电平即active-high;当CPOL为1时,SCLK空闲时为高电平,有效时为低电平即active-low。

SCLK时钟的空闲时刻指的是当SCLK在发送8个bit比特数据之前和之后的状态,

与此对应的,SCLK在发送数据的时候,就是正常的工作的时候即有效active的时刻。

CPHA相位:

当CPHA为0时,在SCLK的前一边沿采样,后一边沿输出。当CPHA为1时,在SCLK的前一边沿输出,后一边沿采样。

CPOL=0时

【1】CPHA=0时,第一个边沿就是从低变到高,所以是上升沿;

【2】CPHA=1时,第二个边沿就是从高变到低,所以是下降沿;

CPOL=1时

【1】CPHA=0时,第一个边沿就是从高变到低,所以是下降沿;

【2】CPHA=1时,第二个边沿就是从低变到高,所以是上升沿;

如何看懂和记忆CPHA和CPOL

首先看时序图,如果时钟SCLK的起始电平是0,那么CPOL=0,如果是1,那么CPOL=1。

然后看数据采样时刻,即时序图数据线上的数据矩形区域的中间所对应的位置,对应到上面SCLK时钟的位置,对应着是第一个边沿或是第二个边沿,即CPHA是0或1。(对应的是上升沿还是下降沿,要根据对应的CPOL的值,才能确定)。

软件中如何设置SPI的极性和相位

【1】固定的,设备硬件决定

SPI从设备,具体是什么模式,相关的datasheet中会有描述,需要自己去datasheet中找到相关的描述,即:

关于SPI从设备,在空闲的时候,是高电平还是低电平,即决定了CPOL是0还是1;

然后再找到关于设备是在上升沿还是下降沿去采样数据,这样就是,在定了CPOL的值的前提下,对应着可以推算出CPHA是0还是1了。如AD7928(自我认为)

【2】可配置的,由软件自己设定

数据传输

在一个SPI时钟周期内,会完成如下操作:

1) 主机通过MOSI线发送1位数据,从机通过该线读取这1位数据;

2) 从机通过MISO线发送1位数据,主机通过该线读取这1位数据。

这是通过移位寄存器来实现的。如图2所示,主机和从机各有一个移位寄存器,且二者连接成环。随着时钟脉冲,数据按照从高位到低位的方式依次移出主机寄存器和从机寄存器,并且依次移入从机寄存器和主机寄存器。当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。

SPI优缺点

优点:1) 支持全双工操作;2) 操作简单;3) 数据传输速率较高

缺点:1) 需要占用主机较多的口线(每个从机都需要一根片选线);2) 只支持单个主机。

I2C

基本过程

1.主机发出开始信号

2.主机接着发出一字节的从机地址信息,其中最低位为读写控制码(1为读、0为写), 高七位为从机器件地址

3.从机发出应答信号

4.主机开始发送信号,每发完一字节后,从机发出应答信号给主机

5.主机发出停止信号

注解:

【1】 开始信号:在时钟线为高电平期间,数据线由高变低,将产生一个开始信号

【2】 停止信号:在时钟线为高电平期间,数据线由低变高,将产生一个停止信号

【3】 应答信号:主机写从机时,每写完一个字节,如果正确从机将在下一个时钟周期将数据线拉低,以告诉主机操作有效。在主机读从机的时候,正确读完一个字节后,主机在下一个时钟周期同样也要将数据线拉低,发出应答信号,告诉从机所发数据已经收妥(注:读从机时主机在最后一个字节数据接收完后,不发应答,直接发停止信号)

注意:任何在时钟线为高电平期间的数据线上的电平改变都被认为是起始和停止信号,所以数据改变必须要在时钟为低电平时改变。