一个用verilog实现抢答器的程序

有没有大佬帮我看一下我的源代码和测试文件有没有什么问题,为什么仿不出来一个想要的波形。。

//主程序部分

module responder (

input clk,

input set,

input reset,

input wire in_a,

input wire in_b,

output wire q_a,

output wire q_b,

output en

);

wire clr;

wire[27:0] cnt;

wire clk_10;

wire timeout;

reg[27:0] n=28'h1ffffff;

assign clr = reset||timeout;

trig trigger(

.set(set),

.clk(clk_10),

.clr(clr),

.en(en)

);

count counter(

.clk(clk_10),

.clr(clr),.en(en),

.cnt(cnt)

);

comp comparator(

.cnt(cnt),

.n(n),

.timeout(timeout)

);

fpga_2 main(

.in_a(in_a),

.in_b(in_b),

.clk(clk_10),

.reset(clr),

.q_a(q_a),

.q_b(q_b),

.en(en)

);

endmodule

//触发器 trigger 部分

module trig(

input set,

input clk,

input clr,

output reg en

);

always@(posedge clk)

begin if(clr) en=0;

else

begin if(set) en=1; else en=en; end

end

endmodule

//计数器 counter 部分

module count(

input clk,

input clr,

input en,

output reg[27:0] cnt);

always @(posedge clk) begin

if(clr)

cnt=0;

else if(en)

cnt=cnt+1;

end

endmodule

//比较器 comparator 部分

module comp(input wire[27:0] cnt, input wire[27:0] n, output reg timeout);

always @(*)

if(cnt==n)

timeout=1;

else

timeout=0;

endmodule

//抢答器部分

module fpga_2( input wire in_a, input wire in_b, input wire clk, input wire reset, input en,

output reg q_a, output reg q_b );

always @(posedge clk) begin

if ( (q_b==1) ||(reset) ) q_a=0;

else if(in_a&&en) q_a=1;

end

always @(posedge clk) begin if ((q_a==1) ||(reset) ) q_b=0;

else if(in_b&&en)

q_b=1;

end

endmodule

以上是源代码,下面是测试代码

module ceshi;

// Inputs

reg set;

reg reset;

reg in_a;

reg in_b;

// Outputs

wire q_a;

wire q_b;

wire en;

reg clk;

// Instantiate the Unit Under Test (UUT)

responder uut (

.clk(clk),

.set(set),

.reset(reset),

.in_a(clk),

.in_b(clk),

.q_a(q_a),

.q_b(q_b),

.en(en)

);

// Initialize Inputs

initial begin

clk=0;

set = 1;

reset = 0;

in_a=1;

#1000 in_a=0;

#100 in_b=1;

#1000 reset=1;

#100 in_b=0;

#100 reset=0;

in_b=1;

#1000 in_b=0;

#100 in_a=1;

#1000 reset=1;

#100 in_a=0;

#100 reset=0;

end

always #10 clk=~clk;

endmodule

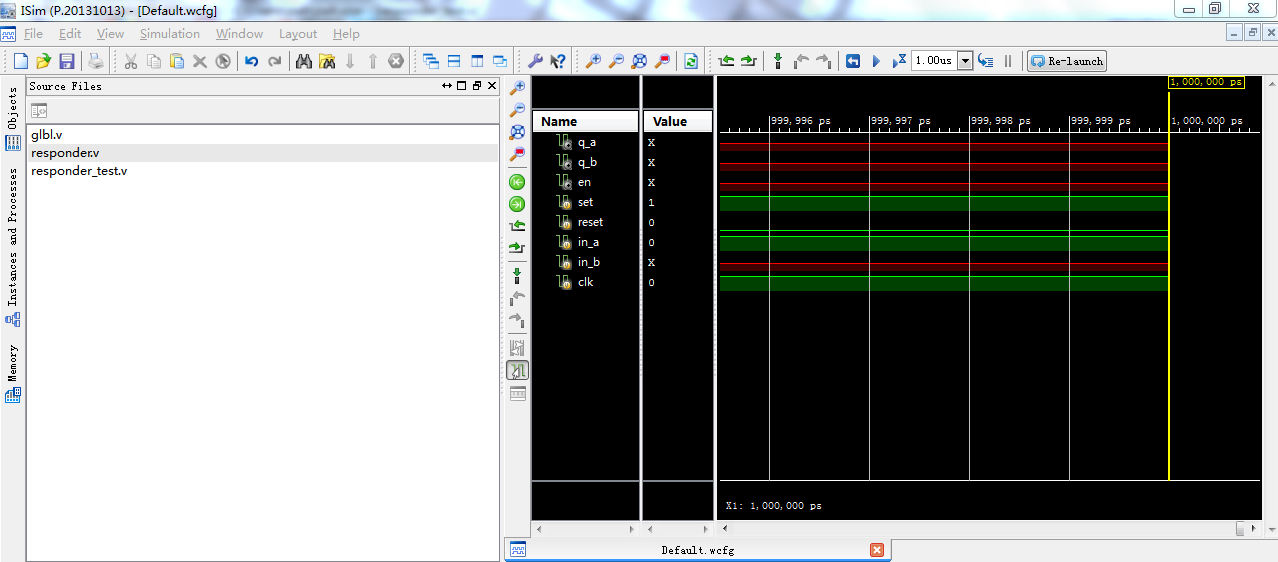

然后仿了一下,结果是这个样子的。。

有没有大佬帮帮忙啊。。一直解决不了