目录

前言

详细地了解这些简单的计数器并非毫无意义的,因为它是组成大型计数器的小模块,如果大型的计数器不太好理解,那么分解出来分别研究,不也是一种好的办法吗?

这篇博文的意义就在如此。我将仿真加综合去详细的认清楚这些小零件。

模6计数器

模6计数器比较关键的一点是从0开始计数,计数到5(0101)时,产生一个进位信号1(注意这个进位信号1可以由第0位与第2位的与来得到,这在设计电路中比较重要,下面会有体现),并且此时,计数状态清零。

Verilog HDL语言描述

//模6计数器的Verilog HDL设计

module counter6(clk, rst_n, en, dout, co);

input clk, rst_n, en;

output[3:0] dout;

reg [3:0] dout;

output co;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

dout <= 4'b0000; //系统复位,计数器清零

else if(en)

if(dout == 4'b0101) //计数值达到5时,计数器清零

dout <= 4'b0000;

else

dout <= dout + 1'b1; //否则,计数器加1

else

dout <= dout;

end

assign co = dout[0]&dout[2]; //当计数达到5(4'b0101)时,进位为1,计数值为其他,都没有进位

endmodule

测试文件

//模6计数器的测试文件

`timescale 1ns/1ps

module counter6_tb;

reg clk, rst_n, en;

wire[3:0] dout;

wire co;

//时钟设计周期为2ns

always

begin

#1 clk = ~clk;

end

//初始化

initial

begin

clk = 1'b0;

rst_n = 1'b1;

en = 1'b0;

#2 rst_n = 1'b0;

#2 rst_n = 1'b1; en = 1'b1; //计数使能信号有效,且不复位

end

counter6 u1(.clk(clk), .rst_n(rst_n), .en(en), .dout(dout), .co(co));

endmodule

仿真电路图

从仿真电路图可以看出,模6计数器从0开始计数,计数到5,计数器清零,然后重新计数。

RTL Schematic

从这里可以看到模6计数器整理的外部输入输出情况,展开后如下:

这个门级的原理图不复杂但是挺不好理解的,哪位壮士看的明白,麻烦给我说一声。

反正这个模6计数器综合出来的寄存器传输级原理图就是这样的。

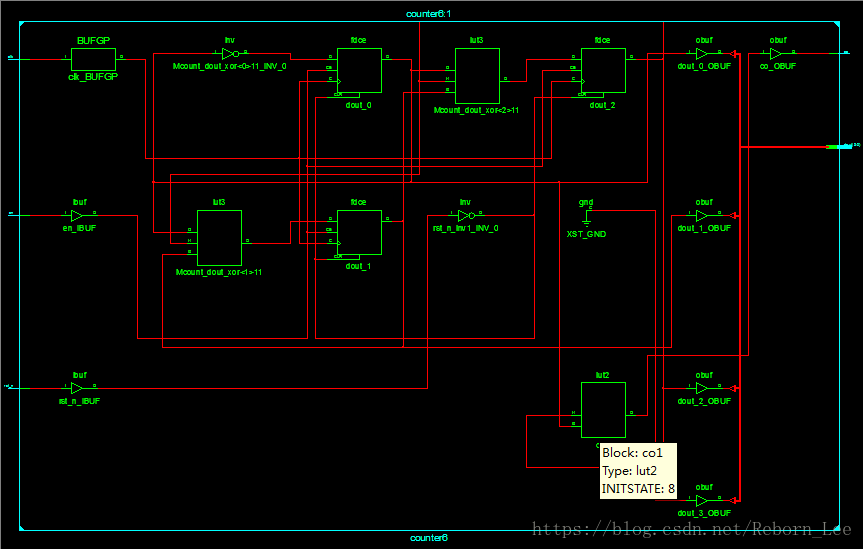

Technology Schematic

也就是在FPGA中是怎么样的一个电路图:

用到了LUT(查找表)、各种BUF以及D触发器资源。

模6计数器就认识到这里吧。

模10计数器

模10计数器的设计和模6计数器的设计如出一辙,甚至说仅仅一点儿变化,也就是把计数值改变一下,计数到9然后清零而已。但我还是把它仿真了个遍。

Verilog HDL语言描述

//模10计数器的Verilog HDL设计

module counter10(clk, rst_n, en, dout, co);

input clk, rst_n, en;

output[3:0] dout;

reg [3:0] dout;

output co;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

dout <= 4'b0000; //系统复位,计数器清零

else if(en)

if(dout == 4'b1001) //计数值达到5时,计数器清零

dout <= 4'b0000;

else

dout <= dout + 1'b1; //否则,计数器加1

else

dout <= dout;

end

assign co = dout[0]&dout[3]; //当计数达到5(4'b1001)时,进位为1,计数值为其他,都没有进位

endmodule

测试文件

//模10计数器的测试文件

`timescale 1ns/1ps

module counter10_tb;

reg clk, rst_n, en;

wire[3:0] dout;

wire co;

//时钟设计周期为2ns

always

begin

#1 clk = ~clk;

end

//初始化

initial

begin

clk = 1'b0;

rst_n = 1'b1;

en = 1'b0;

#2 rst_n = 1'b0;

#2 rst_n = 1'b1; en = 1'b1; //计数使能信号有效,且不复位

end

counter10 u1(.clk(clk), .rst_n(rst_n), .en(en), .dout(dout), .co(co));

endmodule

仿真波形

RTL Schematic

Technology Schematic

用的资源好像比模6计数器要多。