高级定时器简介

STM32F103ZET6中有TIM1,TIM8两个高级定时器,每一定时器都有

- 一个16位向上、向下、向上/下自动装载计数器

- 一个16位预分频器和四个独立从输入输出通道

- 每一个通道都可用于输入捕获、输出比较、PWM和单脉冲模式(除了基本定时器,高级定时器和通用定时器都能产生PWM)

单片机中没有时间的概念,因此定时器本质是一个以单位时间为准的计数器,计数值可以从0开始累加,也可以从一个设定值(ARR)的值递减,每隔一个固定的时间(由psc和时钟周期控制)计数器的值+1或-1,加到或减到头时会产生一个溢出信号,此时计数器的计数值清零或补充成初值,重新开始计数

高级定时器框图

1. 时钟源

由四个时钟来源,分别是

- 内部时钟源 CK_INT

- 外部时钟模式 1:外部输入引脚 TIx(x=1,2,3,4)

- 外部时钟模式 2:外部触发输入 ETR

- 内部触发输入(ITRx)

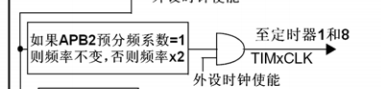

我们一般只用内部时钟源CK_INT,对于高级定时器,其时钟是由APB2总线时钟决定的

其他类型的定时器同理可以参考参考手册的RCC部分的时钟框图

对于其他时钟来源,参考参考手册的13.3.4小节

2. 控制器

用来控制和发送命令的

相关的寄存器有

- CR1(control register 1 )控制寄存器1

- CR2(control register 2 )控制寄存器2

- SMCR(slave mode control register)从模式控制寄存器

宏观上来讲,主模式:就是主CPU作为主机,向从机(挂载器件)发送接收数据。

从模式:就是主CPU作为从机,接收和发送主机(挂载器件)数据。

- CCER(capture/compare enable register)捕获比较寄存器

等等寄存器

3. 时基单元Time-base unit

时基单元的组成:

(1)1-16位的预分频器 PSC

对控制计数器的时钟进行分频,分配系数可以为1~65536

(2)16位的计数器CNT

每经过一个计数器时钟周期这里变化1(+1或-1)

(3)4-16位的自动重装载寄存器ARR

- 向上计数时,但计数器的值CNT从0计数到ARR的值的时候,会产生溢出中断(也叫更新中断,update interrupt),然后会清零重新计数

- 向下计数时,当计数器的值CNT从ARR的值计数到0的时候会产生溢出中断,然后会重新填充ARR的值

(4)8位的重复计数器RCR(高级定时器独有的,基本和基础定时器都没有)

向上计数时,我们把REO的值设置成10,如果有设置当计数器溢出的时候,那么此时不会产生中断,而是RCR的值+1,当加到10的时候才产生中断,向下 计数原理类似,只不过是从10减到0

4.输入捕获

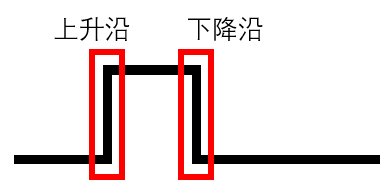

- 输入捕获可以对输入的信号的上升沿,下降沿或者双边沿进行捕获,常用的有测量输入信号的脉宽和测量 PWM 输入信号的频率和占空比这两种

- 输入捕获的大概原理:

输入引脚检测到电平跳变时(上升沿或下降沿),把计数器CNT的值锁存到捕获寄存器CCRx中,把前后两次捕获到的 CCR x寄存器中的值相减,就可以算出脉宽或者频率

(1)输入通道引脚

需要测量的信号从TIMx_CH1~4进入

(2)输入滤波器和边沿检测器

- 信号受到干扰时,滤波器可以对输入信号进行滤波,即进行重新采样

- 滤波器的配置由 CR1 寄存器的位 CKD[1:0]和 CCMR1/2 的位 ICxF[3:0]控制

- 边沿检测器用来设置信号在捕获的时候是什么边沿有效,可以是上升沿,下降沿,或

者是双边沿,由 CCER 寄存器的位 CCxP 和 CCxNP 决定

(3)捕获通道

- 捕获通道就是图中的 IC1/2/3/4,每个捕获/比较通道都有相对应的捕获寄存器 CCR1/2/3/4,

当发生捕获的时候,计数器 CNT 的值就会被锁存到捕获寄存器中

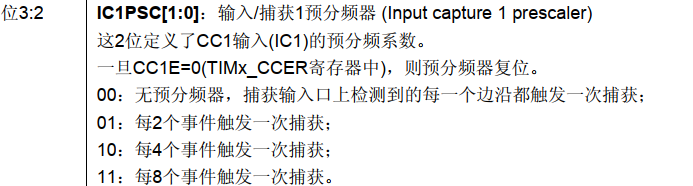

(4)预分频器

- ICx 的输出信号会经过一个预分频器,用于决定发生多少个事件时进行一次捕获。具

体的由寄存器 CCMRx 的位 ICxPSC 配置 - 如果希望捕获信号的每一个边沿,则不分频

(5)捕获寄存器

- 经过预分频器的信号 ICxPS 是最终被捕获的信号

- 当发生捕获时(第一次),计数器CNT 的值会被锁存到捕获寄存器 CCR 中,还会产生 CCxI 中断,相应的中断位 CCxIF(在SR 寄存器中)会被置位,通过软件或者读取 CCR 中的值可以将 CCxIF 清 0。

- 如果发生第二次捕获(即重复捕获: CCR 寄存器中已捕获到计数器值且 CCxIF 标志已置 1),则捕获

溢出标志位 CCxOF(在 SR 寄存器中)会被置位, CCxOF 只能通过软件清零

5.输出比较

- 通过定时器的外部引脚对外输出控制信号

- 有八种模式,主要使用的是其PWM1和PWM2模式

- 具体使用哪种模式由寄存器 CCMRx 的位 OCxM[2:0]配置

(1)比较寄存器

- 比较寄存器与捕获寄存器是同一个寄存器

- 计数器 CNT 的值跟比较寄存器 CCR 的值相等的时候,输出参考信号 OCxREF 的信

号的极性就会改变( OCxREF=1(高电平)称之为有效电平, OCxREF=0(低电平)

称之为无效电平) - 会产生比较中断 CCxI,相应的标志位 CCxIF(SR 寄存器中(状态寄存器,里面有各种状态或中断标记))会置

位

(2)死区发生器

- 在生成的参考波形 OCxREF 的基础上,可以插入死区时间,用于生成两路互补的输出

信号 OCx 和 OCxN(OCxN的波形与OCx的相反)

- 死区时间的大小具体由 BDTR 寄存器的位 DTG[7:0]配置

这里的T_ DTS是由内部时钟T_CK_INT经过分频得到的,由CR1寄存器上的CKD[9:8]位控制的

(3)输出控制

参考参考手册13.3.5小节

(4)输出引脚

输出比较的输出信号最终是通过定时器的外部 IO 来输出的,分别为 CH1/2/3/4,其中

前面三个通道还有互补的输出通道 CH1/2/3N