1、任务和函数必须在模块中定义,也只能在定义它们的模块中使用。

2、任务用于代替普通Verilog代码,可包含延迟、时序、事件等;函数用于代替表示纯组合逻辑的Verilog代码。

-任务:关键字task-endtask。必须使用任务而不能使用函数的条件:1.程序中包含延迟、时序、事件控制结构;2.没有输出、输出变量数目大于1;3.没有输入变量。

任务使用示例:

或者:

-自动(可重入)任务:task后加关键字automatic。由于任务中声明项的地址空间是静态分配的,若是同时并发执行的多个任务共享存储区。若两个任务被同时调用,则会对同一个地址空间进行操作,产生冲突。使用自动任务,可以将存储空间动态分配给声明项,每个任务调用独立变量副本进行操作。

task automatic bitwise_xor;

……

endtask

-函数:关键字function-endfunction。函数使用必须同时满足如下条件:不含延迟、时序、控制结构;只有一个返回值;至少有一个输入变量;没有输出或双向变量;不含非阻塞赋值语句。

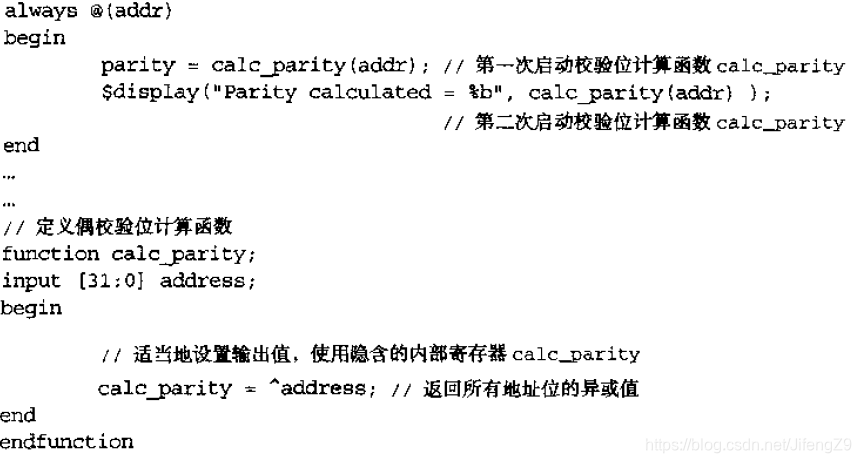

函数使用示例:

-自动(递归)函数:关键字automatic。同自动任务,仿真器为每一次函数调用动态地分配新的地址空间。自动函数声明的局部变量不能通过层次名进行访问,自动函数本身可以通过层次名进行调用。

自动函数使用示例:

-常量函数:带有某些限制的常规函数,能够又来引用复杂值,可代替常量。

-带符号函数:带符号函数的返回值可以作为带符号数进行运算。