主页: 元存储博客

全文 3000 字

文章目录

1. 声明格式

1.1 模块声明

module module_name (input_list, output_list);

// 模块内部的代码

endmodule

1.2 输入输出声明

input input_name;

output output_name;

1.3 内部信号声明

wire wire_name;

reg reg_name;

1.4 内部逻辑声明

assign wire_name = expression; // 组合逻辑

always @(posedge clk) begin // 同步逻辑

// 时序逻辑代码

end

1.5 连接声明

module_name instance_name (input_list, output_list);

1.6 数据类型声明

logic [n-1 : 0] signal_name; // n位逻辑类型

wire [n-1 : 0] signal_name; // n位有线类型

reg [n-1 : 0] signal_name; // n位寄存器类型

1.7 运算符和表达式

expression1 + expression2; // 加法

expression1 - expression2; // 减法

expression1 * expression2; // 乘法

expression1 / expression2; // 除法

expression1 & expression2; // 与运算

expression1 | expression2; // 或运算

expression1 ^ expression2; // 异或运算

~expression; // 取反

1.8 控制结构

if (condition) begin

// 条件为真时执行的代码

end else begin

// 条件为假时执行的代码

end

for (initialization; condition; increment) begin

// 循环执行的代码

end

case (expression)

value1: begin

// 执行代码

end

value2: begin

// 执行代码

end

default: begin

// 执行代码

end

endcase

这只是Verilog语言的基本书写格式,Verilog文本文件通常以.v扩展名保存。实际应用中,还有其他更高级的功能和语法规则,可以根据具体需求进行学习和使用。

2. 书写格式

2.1 大小写

Verilog是一种区分大小写的编程语言。

2.2 换行

在Verilog中,编程格式是自由的,可以在一行内编写,也可以跨多行编写。

因此,下面两种编程方式是等效的。

不换行(不推荐的写法):

module myModule;output reg out;input a,b,c;always@(a or b or c)beginout=a&b|c;endendmodule

换行

module myModule;

output reg out;

input a,b,c;

always @ (a or b or c) begin

out = a & b | c;

end

endmodule

为什么推荐换行

可读性:在代码中适当的换行可以增加代码的可读性,使代码更易于理解和维护。长长的一行代码可能会导致阅读不便,特别是当代码中包含多个操作符或函数调用时。

错误排查:如果代码出现错误,换行可以帮助更精确定位错误的位置。如果一行代码太长,错误信息可能会显示为超出屏幕范围,让开发者难以找到具体的错误。

2.3 语句结束符

每个Verilog语句必须以分号作为结束符。空白符(换行、制表、空格)在编译阶段可以被忽略。

2.4 注释

在Verilog中,有两种注释方式:单行注释和多行注释。

单行注释:使用"//"符号来注释单行代码。例如:

reg [3:0] count; // 这是一个单行注释

多行注释:使用"/“和”/"符号来注释多行代码。例如:

/*

定义了一个10位宽的有符号整数类型(wire [9:0])的变量age。然后通过赋值语句(assign)将age赋值为10位宽的二进制数10'b1。因为10'b11表示二进制数11,它的十进制值是3。

*/

wire [9:0] age;

assign age= 10'b11 ;

2.5 标识符

- 标识符只能包含字母、数字和下划线,不能以数字开头。

- 标识符区分大小写。

- 标识符的长度可以是任意的,但是一般不超过1024个字符。

- Verilog有一些保留字,如always、module等,不能作为标识符使用。

- 标识符不能包含特殊字符,如空格、制表符等。

- 在Verilog中,常见的命名规范是使用小写字母和下划线,多个单词之间使用下划线分隔,例如:data_out、counter。

需要注意的是,虽然在Verilog中允许使用Unicode字符,但是为了保持代码的可读性,一般不建议在标识符中使用非ASCII字符。

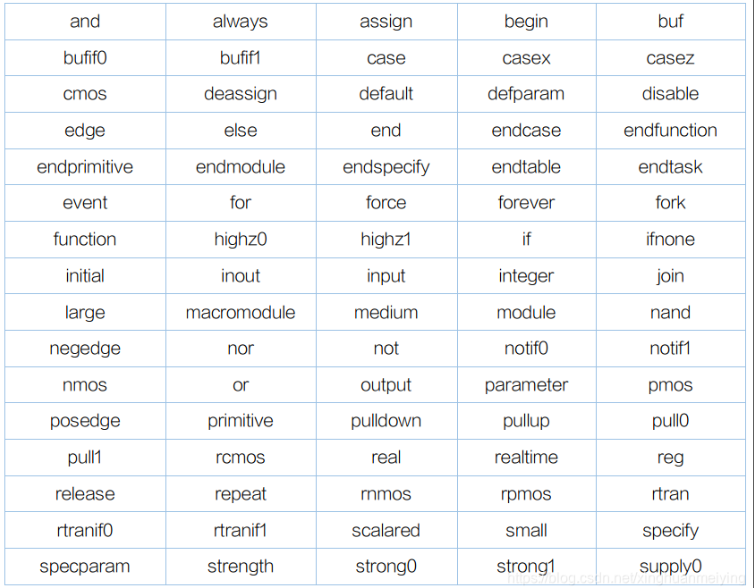

2.6 关键字

Verilog的关键字包括以下内容:

and、always、assign、automatic、begin、buf、bufif0、bufif1、case、casex、casez、cmos、deassign、default、defparam、disable、edge、else、end、endcase、endfunction、endmodule、endprimitive、endspecify、endtable、endtask、event、for、force、forever、fork、function、highz0、highz1、if、ifnone、initial、inout、input、integer、join、large、macromodule、medium、module、nand、negedge、nmos、nor、not、notif0、notif1、or、output、packed、parameter、pmos、posedge、primitive、pull0、pull1、pulldown、pullup、rcmos、real、reg、release、repeat、rnmos、rpmos、rtran、rtranif0、rtranif1、scalared、signed、small、specify、specparam、strong0、strong1、supply0、supply1、table、task、time、tran、tranif0、tranif1、tri、tri0、tri1、triand、trior、trireg、unsigned、use、vectored、wait、wand、weak0、weak1、while、wire、wor、xnor、xor等。

参考文献

声明

本文仅为学习交流目的。

文中部分文字和图片来源于互联网,列在参考的文献,但可能有遗漏。如有侵权,请告知我删除。