主要内容:

1. 4位流水线乘法器

2. 8位流水线乘法器

3. 16位流水线乘法器

1. 4位流水线乘法器

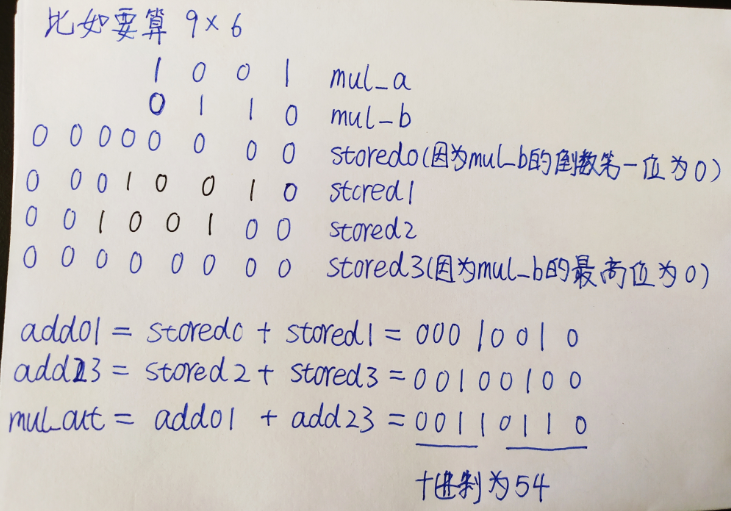

1 module multi_4bits_pipelining(mul_a, mul_b, clk, rst_n, mul_out); 2 3 input [3:0] mul_a, mul_b; 4 input clk; 5 input rst_n; 6 output [7:0] mul_out; 7 8 reg [7:0] mul_out; 9 10 reg [7:0] stored0;//stored0,...stored3用来存逐位相乘的中间结果 11 reg [7:0] stored1; 12 reg [7:0] stored2; 13 reg [7:0] stored3; 14 15 reg [7:0] add01;//中间结果变量 16 reg [7:0] add23; 17 18 always @(posedge clk or negedge rst_n) begin 19 if(!rst_n) begin 20 mul_out <= 0; 21 stored0 <= 0; 22 stored1 <= 0; 23 stored2 <= 0; 24 stored3 <= 0; 25 add01 <= 0; 26 add23 <= 0; 27 end 28 else begin 29 stored0 <= mul_b[0]? {4'b0, mul_a} : 8'b0;//如果被乘数倒数第一位不为零,则与乘数相乘结果为{4'b0,mul_a} 30 stored1 <= mul_b[1]? {3'b0, mul_a, 1'b0} : 8'b0; 31 stored2 <= mul_b[2]? {2'b0, mul_a, 2'b0} : 8'b0; 32 stored3 <= mul_b[3]? {1'b0, mul_a, 3'b0} : 8'b0; 33 34 add01 <= stored1 + stored0; 35 add23 <= stored3 + stored2; 36 37 mul_out <= add01 + add23;//最终结果 38 end 39 end 40 41 endmodule

1.1 4位流水线乘法器案例

2. 8位流水线乘法器

1 module multiplier_8(clk,rst_n,mul_a,mul_b,result 2 ); 3 input clk; 4 input rst_n; 5 input[7:0] mul_a; 6 input[7:0] mul_b; 7 output[15:0] result; 8 reg[15:0] result; 9 reg[15:0] store7; 10 reg[15:0] store6; 11 reg[15:0] store5; 12 reg[15:0] store4; 13 reg[15:0] store3; 14 reg[15:0] store2; 15 reg[15:0] store1; 16 reg[15:0] store0; 17 reg[15:0] add01; 18 reg[15:0] add23; 19 reg[15:0] add45; 20 reg[15:0] add67; 21 reg[15:0] add0123; 22 reg[15:0] add4567; 23 always @ (posedge clk or negedge rst_n) 24 25 begin 26 if(!rst_n) 27 begin 28 store7 <= 16'b0; 29 store6 <= 16'b0; 30 store5 <= 16'b0; 31 store4 <= 16'b0; 32 store6 <= 16'b0; 33 store2 <= 16'b0; 34 store1 <= 16'b0; 35 store0 <= 16'b0; 36 add01 <= 16'b0; 37 add23 <= 16'b0; 38 add45 <= 16'b0; 39 add67 <= 16'b0; 40 add0123 <= 16'b0; 41 add4567 <= 16'b0; 42 end 43 else 44 45 begin 46 store0 <= mul_b[0] ? {8'b0,mul_a}:16'b0; 47 store1 <= mul_b[1] ? {7'b0,mul_a,1'b0}:16'b0; 48 store2 <= mul_b[2] ? {6'b0,mul_a,2'b0}:16'b0; 49 store3 <= mul_b[3] ? {5'b0,mul_a,3'b0}:16'b0; 50 store4 <= mul_b[4] ? {4'b0,mul_a,4'b0}:16'b0; 51 store5 <= mul_b[5] ? {3'b0,mul_a,5'b0}:16'b0; 52 store6 <= mul_b[6] ? {2'b0,mul_a,6'b0}:16'b0; 53 store7 <= mul_b[7] ? {1'b0,mul_a,7'b0}:16'b0; 54 55 add67 <= store7+store6; 56 add45 <= store5+store4; 57 add23 <= store3+store2; 58 add01 <= store1+store0; 59 add0123 <= add01 + add23; 60 add4567 <= add45 + add67; 61 result <= add0123 + add4567; 62 end 63 end 64 endmodule

3. 16位流水线乘法器

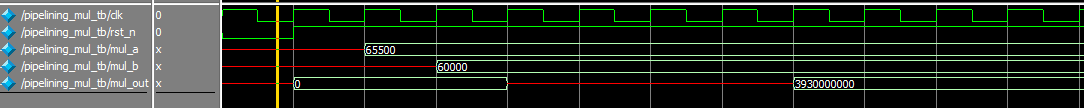

1 module pipelining_mul(clk,rst_n,mul_a,mul_b,mul_out); 2 input clk,rst_n; 3 input [15:0] mul_a; 4 input [15:0] mul_b; 5 output [31:0] mul_out; 6 7 reg [31:0] mul_out; 8 reg [31:0] store15,store14,store13,store12,store11,store10,store9,store8, 9 store7,store6,store5,store4,store3,store2,store1,store0; 10 reg [31:0] add01,add23,add45,add67,add89,add1011,add1213,add1415; 11 reg [31:0] add0123,add4567,add891011,add12131415; 12 reg [31:0] add01234567,add89101112131415; 13 always @ (posedge clk or negedge rst_n) 14 begin 15 if(!rst_n) 16 begin 17 store15 <= 32'b0; 18 store14 <= 32'b0; 19 store13 <= 32'b0; 20 store12 <= 32'b0; 21 store11 <= 32'b0; 22 store10 <= 32'b0; 23 store9 <= 32'b0; 24 store8 <= 32'b0; 25 store7 <= 32'b0; 26 store6 <= 32'b0; 27 store5 <= 32'b0; 28 store4 <= 32'b0; 29 store6 <= 32'b0; 30 store2 <= 32'b0; 31 store1 <= 32'b0; 32 store0 <= 32'b0; 33 add01 <= 32'b0; 34 add23 <= 32'b0; 35 add45 <= 32'b0; 36 add67 <= 32'b0; 37 add89 <= 32'b0; 38 add1011 <= 32'b0; 39 add1213 <= 32'b0; 40 add1415 <= 32'b0; 41 add0123 <= 32'b0; 42 add4567 <= 32'b0; 43 add891011 <= 32'b0; 44 add12131415 <= 32'b0; 45 add01234567 <= 32'b0; 46 add89101112131415 <= 32'b0; 47 end 48 else 49 begin 50 store15 <= mul_b[15] ? {1'b0,mul_a,15'b0}:32'b0; 51 store14 <= mul_b[14] ? {2'b0,mul_a,14'b0}:32'b0; 52 store13 <= mul_b[13] ? {3'b0,mul_a,13'b0}:32'b0; 53 store12 <= mul_b[12] ? {4'b0,mul_a,12'b0}:32'b0; 54 store11 <= mul_b[11] ? {5'b0,mul_a,11'b0}:32'b0; 55 store10 <= mul_b[10] ? {6'b0,mul_a,10'b0}:32'b0; 56 store9 <= mul_b[9] ? {7'b0,mul_a,9'b0}:32'b0; 57 store8 <= mul_b[8] ? {8'b0,mul_a,8'b0}:32'b0; 58 store7 <= mul_b[7] ? {9'b0,mul_a,7'b0}:32'b0; 59 store6 <= mul_b[6] ? {10'b0,mul_a,6'b0}:32'b0; 60 store5 <= mul_b[5] ? {11'b0,mul_a,5'b0}:32'b0; 61 store4 <= mul_b[4] ? {12'b0,mul_a,4'b0}:32'b0; 62 store3 <= mul_b[3] ? {13'b0,mul_a,3'b0}:32'b0; 63 store2 <= mul_b[2] ? {14'b0,mul_a,2'b0}:32'b0; 64 store1 <= mul_b[1] ? {15'b0,mul_a,1'b0}:32'b0; 65 store0 <= mul_b[0] ? {16'b0,mul_a}:32'b0; 66 add1415 <= store15+store14; 67 add1213 <= store13+store12; 68 add1011 <= store11+store10; 69 add89 <= store9+store8; 70 add67 <= store7+store6; 71 add45 <= store5+store4; 72 add23 <= store3+store2; 73 add01 <= store1+store0; 74 add0123 <= add01 + add23; 75 add4567 <= add45 + add67; 76 add891011 <= add89 + add1011; 77 add12131415 <= add1213 + add1415; 78 add01234567 <= add0123 + add4567; 79 add89101112131415 <= add891011 + add12131415; 80 mul_out <= add01234567 + add89101112131415; 81 end 82 end 83 endmodule

1 `timescale 1ns/1ps 2 `define clock_period 20 3 4 module pipelining_mul_tb; 5 6 reg clk; 7 reg rst_n; 8 reg [15:0] mul_a; 9 reg [15:0] mul_b; 10 wire [31:0] mul_out; 11 12 initial begin 13 clk = 1'b1; 14 rst_n = 1'b0; 15 # 20 //一个周期 16 rst_n = 1'b1; 17 # 20 18 mul_a <= 65500; 19 # 20 20 mul_b <= 60000; 21 # 200 22 23 $stop; 24 end 25 always #(`clock_period/2) clk = ~clk; //50M 26 27 pipelining_mul pipelining_mul_0( 28 .clk(clk), 29 .rst_n(rst_n), 30 .mul_a(mul_a), 31 .mul_b(mul_b), 32 .mul_out(mul_out) 33 ); 34 endmodule

参考:

https://blog.csdn.net/Reborn_Lee/article/details/80329823

https://www.cnblogs.com/shengansong/archive/2011/05/23/2054401.html

https://www.cnblogs.com/hclmcu/archive/2010/08/23/1806213.html