第一种:

先随便写一个程序,有输入,有时钟,有输出

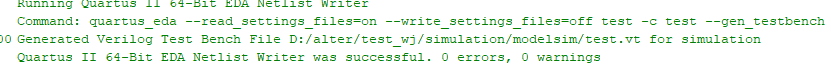

再点击processing-->start-->start test bench template writer

然后就会在modlsim的文件中生成一个.vt的文件

然后打开这个文件

接下来就是再initial和always里面添加信号

保存,再点击

首先看仿真软件是不是modelsin-altera,再看语言是不是verilog hdl,然后选择compile test bench,再点击test benches...

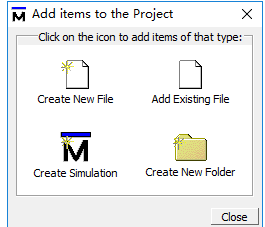

点击new

test bench name 为仿真文件的名字,top level module in test bench 为仿真文件内的模块名,最后点击flie name的...

找到.vt的文件

再点击add

再一路ok

然后全编译一下

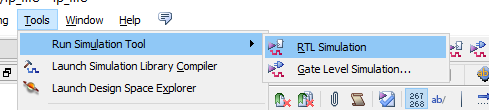

最后点击tool --> run simulation tool -->rtl simulation

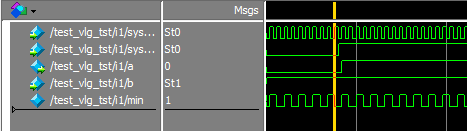

最后就生成了仿真波形

可以通过这些工具进行查看波形

![]()

![]()

第二种方法:

先随便写个文件,有时钟,有输入,有输出

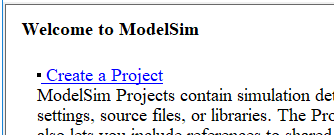

再直接打开modelsim altera的软件,点击jumpstart

再点击create a project

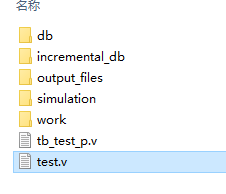

选择仿真文件路径,一般就是自己创建verilog文件的路径再加一个文件夹,project name 就为一个仿真文件的名.再点击ok

先点击creat new file

自己选择路径和取名,注意要是verilog的,别选错,再ok

再点击add existing file

选择自己写的那个verilog文件

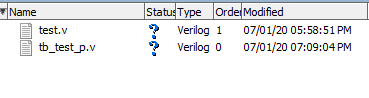

最后为这样

双击tb_test_p.v

开始写自己的仿真测试代码,我的就写这样,跟上面的一样

再保存一下

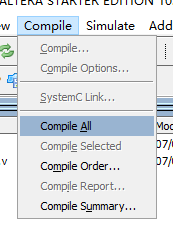

再点击compile all,全编译一下

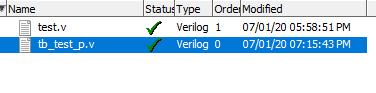

编译好了=就这样了

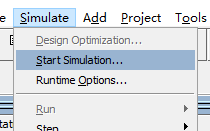

再点击simulate-->start simulation

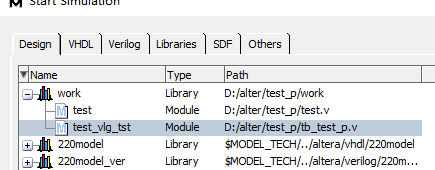

再点击work里面的test_vlg_tst,这个是仿真文件的模块名,再点击ok

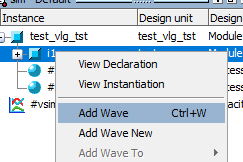

右键,add ware

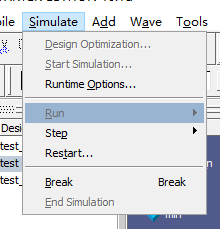

再点击simulate-->run-->run all 我是已经点击,所以点击不了

最后生成: