首先说一下SignalTap和ModuleSim的区别,很显然这是两个不同的东西,SignalTap是集成于Quartus II的,是通过JTAG来抓取实际信号用于分析的,而ModuleSim则是独立于Quartus II,是用于进行功能仿真的一个软件。

一般的话,用ModuleSim进行功能仿真肯定是第一步,功能验证正确之后,再将代码烧写到板子里去,查看运行结果,这时候我们就需要用到SignalTap这个工具。这个工具位于Tools->SignalTap II Logic Analyzer里面。

操作过程简单如下:

1、完成对工程的单次编译;

2、打开signaltap图形界面,添加信号,并作相关设置;然后保存成.stp文件,添加到工程。

3、重新编译并下载到FPGA;

4、打开之前的stp文件,连接jtag就可以触发,并观察信号。

打开SignalTap这个软件,可以看到它大致分为以下几部分。

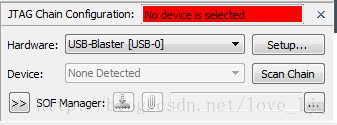

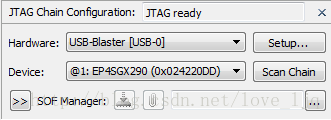

这部分是JTAG Chain,用于显示JTAG的连接情况、FPGA芯片的名称以及sof文件的下载。

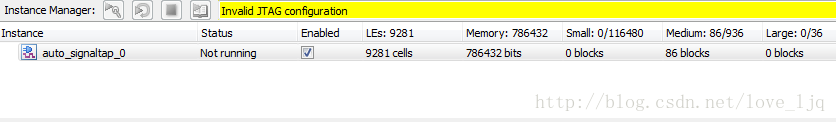

这部分是用于显示当前的状态以及资源消耗等信息。

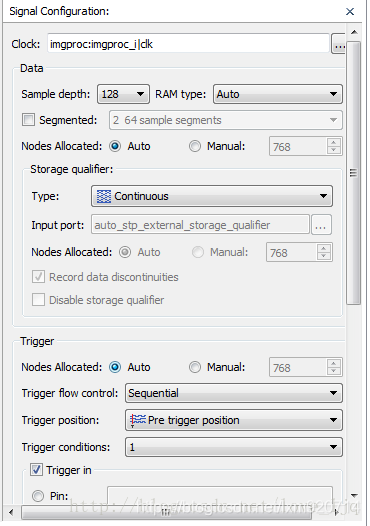

这部分用于显示配置信息。Sample depth就是采集的数据的个数,采集的个数越多则需要的RAM的数量就越多,RAM type则是使用的RAM的类型。因为SignalTap需要占用资源,所以设置不当有可能导致板子上布线布不下。

----------------------------------------------------------------------------------------------------------------

clock:采样时钟,选择设计中的时钟或者从外部输入。数据的每一上升沿被采样,并存入到RAM中,频率越高,对一个点附近采样的数据就越多,信号就越保真;Sample depth:采样深度,就是给采样数据分配的存储空间的大小。这两个参数决定了一个问题,Sample depth固定,采样频率越高,那么在触发点附近,采样的时间跨度就很小,只能采样触发点很短时间范围内的信号变化。所以这两个参数选择时斟酌斟酌。

segmented:这个设置允许我们分段缓存,也就是说可以同时查看多个触发点,例如将128kb的采样深度分为64k x 2的两个缓冲区,在同一个显示区间,可以查看两个连续的触发点的触发结果。

storage qualifier:这个设置项,帮助在调试时,指定存储器中存储的数据类型(the type of data stored in memory),默认模式下,signalTap II的此选项为“continuously”,即连续捕获并存储每一个时钟沿的数据,另外在此模式下,可以指定捕获并存储设计中的某几个信号。其他选项如下:

Input Port:当输入信号是高电平时,捕获数据。这个模式下会生成一个端口,我们需要给他赋予一个信号

Transitional:在指定的数据发生变化时,捕获并存储数据。

Conditional:允许通过设置一个存储使能信号作为存储的条件,这个信号同时作为触发输入信号。

也就是说当触发条件发生时,那些信号会被存储到ram中有这些设置来决定,一般就直接选择continuously

---------------------------------------------------------------------------------------------------------

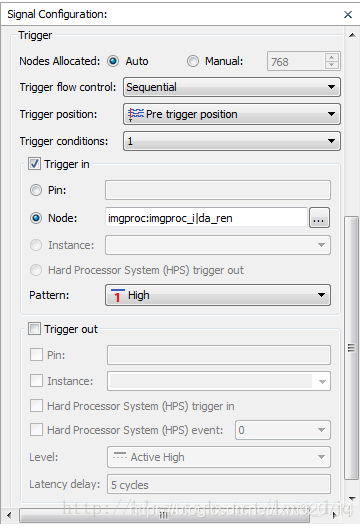

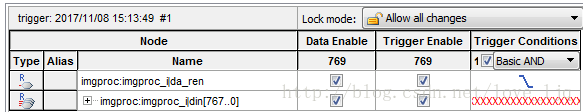

这里很重要的一个地方就是Trigger,就是设置触发状态,比如你要监视的是某个FIFO的输出,如果你不设置触发,那么你一次只能看到FIFO的一个值输出,而不是一连串的值输出。这边的Node就是设置的触发信号,下面的Pattern就是触发的条件,这里的触发条件选的是da_ren这个信号置高。当然也可以选择某个信号上升沿或者下降沿的情况下进行信号捕捉。

------------------------------------------------------------------------------------------------------------------

再来看看触发条件的设置:

trigger flow:触发流,也即是触发的顺序控制。其可选参数是:sequential 和state-based;

sequential:在触发采集缓冲区之前,顺序计算所有的触发条件,即当一个触发条件满足后,判断第二个触发条件是否满足,以此类推,所有都满足时触发。

state-based:此模式下,可自行定制触发的顺序,当你对你的设计进行调试时,使得你对触发的条件有更进一步的控制。你可以查看每一个状态下的触发条件,并可以在“state-based trigger flow”的状态机编辑器中编辑他们。

triggle position:设置采样位置,有以下三个采样位置可选

Pre-trigger position:保存触发信号发生之后的信号状态信息(88%触发后数据,12%触发前数据)。

Center-trigger position:保存触发信号发生前后各50%的数据。

post-trigger position:保存触发信号发生之前的信号状态信息(88%触发前数据,12%触发前数据)。

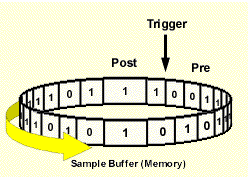

上述的这个设置,我当时没理解,我一直以为是当触发信号发生后,采样时钟才啪啪啪开始采样触发点后面的数据,直到采样存储的RAM慢为止;其实不是,采样的数据放置在一个循环采集buffer(sample depth设置的大小)中,采样时钟总是在采样被观测的信号,这个buffer总是用最新的数据代替后来的旧的数据。当触发条件发生后,signaltap继续采集触条件发生后的数据,以便作为触发后的数据。上述三个设置就是设置到底在触发后,保留触发条件发生前多少点,并还需要采集多少点。理解可参考下图:

trigger conditions:触发级数

多级触发功能提供了更为精确的触发条件。多级触发中,SignalTap Ⅱ首先对第一级的触发表达式进行判断,结果为TRUE时,再对第二级的触发表达式进行判断,直到所有的触发条件都成立时,SignalTap Ⅱ开始捕获信号。

-------------------------------------------------------------------------------------------------------------

这里是选择信号的地方,你要选择什么信号,就需要在这里进行添加。

下面讲一下具体的使用方法。

首先需要将工程编译一下,然后进入这个界面,在Signal Configuration的Clock处进行基准时钟的选择。

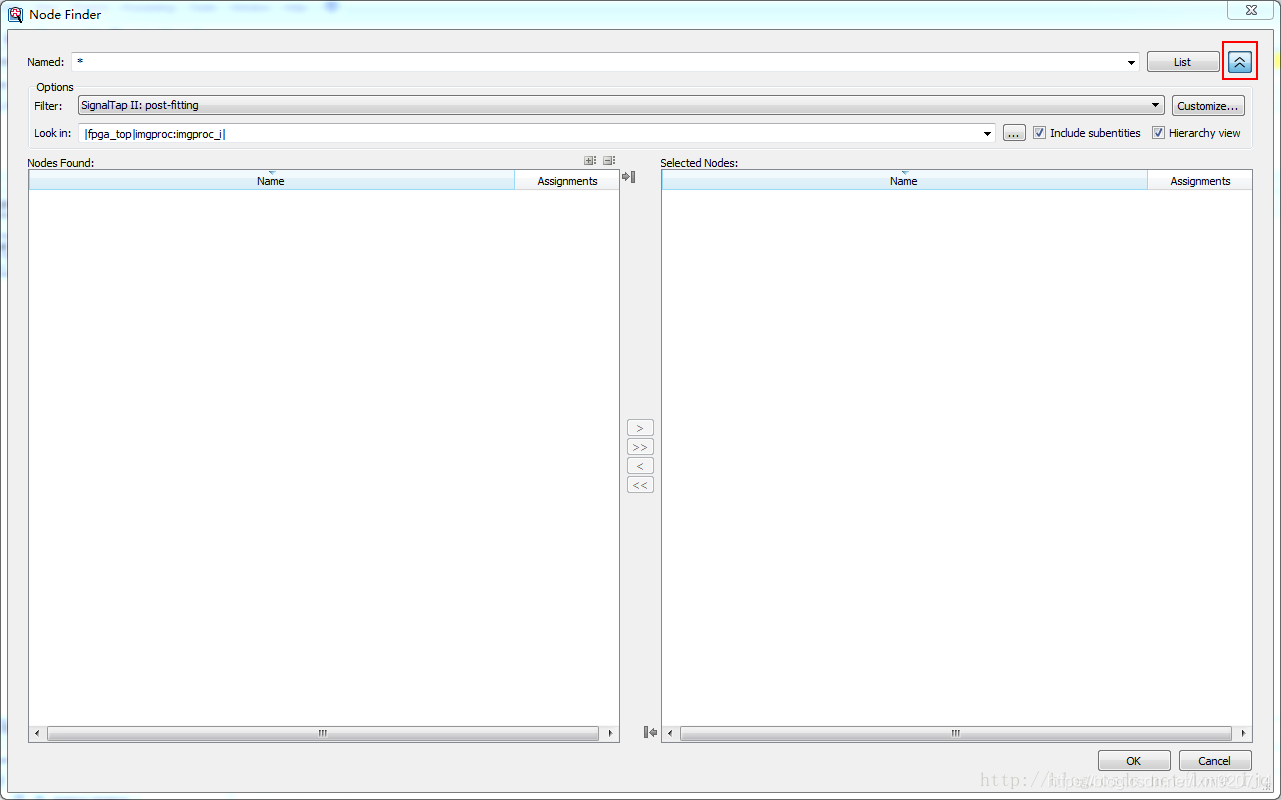

Options这一栏默认是隐藏的,点击图中红框的位置,可以进行显示。Filter中的几个选项具有有什么区别,我也不太清楚,默认的值是SignalTap II:post-fitting,但是这样的话就会有一些信号找不到,而且信号后面有~,不清楚具体什么含义。如果要查看所有的信号的话,就选择SignalTap II: pre-synthesis,暂时不知道这个选项会对结果产生什么影响,等后续了解了会在博客上进行更新。Look in就是将范围缩小,如果是一个大工程的话,直接点击List会得到太多的信号,要找到想要的信号就会比较麻烦,Include subentities是说是否包含子模块,Hierarchy view则是说是否以树状展示。一般两者我们都会进行勾选。

----------------------------------------------------------------------------------------------------------------------------------

A、对工程的编译有两种方式,一种是全编译(start compilation),另一种只是做编译(start analysis & synthesis),不做映射(mapping),这两种方式,会对应两种网络节点(node),也就是我们的信号名称,signaltap观察点的增加就是以这些node作为用户的交互信息,“全编译”后根据全编译的网表,相应的node信息选择signaltap II:post-fitting;“start analysis & synthesis”编译后,signaltap选择signaltap II:pre-synthesis;那么这两种有什么区别呢?

选择pre-synthesis:以“start analysis & synthesis”综合后的网表中的node信息做为signaltap的信息节点,并且将其添加到工程后,再次编译工程,会重新综合并重新布局布线整个工程的所有逻辑。

选择post-fitting:官方文档中给过这个node的使用场景,大概意思是当我们的工程编译完成后,下载到FPGA中,发现工程项目有问题,此时想加入signaltap来分析问题,但又不想改变之前的布局布线的结果,此时选择这个node来作为观察信息的来源,quartus会自动启动增量编译来编译增加的signaltap逻辑,保留之前的逻辑布线和布局结果。

按我的理解就是,有“预谋”的使用signaltap就使用pre-synthesis,“意外”情况就使用post-fitting。

------------------------------------------------------------------------------------------------------------------------------------

在Signal Configuration的Data部分,选择Sample depth和RAM,这个按照默认值就行了,如果剩余的RAM还很多,可以多采样。

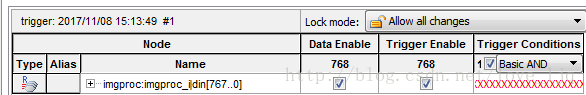

这是添加信号的图示,后面的Trigger Conditions意思是当满足某个条件的时候,进行数据采集,否则不采集。把这些设置完了之后,点击QuartusII界面的Save all,然后进行重新编译。

接上板子之后,会看到下面这个图,图中有显示当前的芯片名称。

编译完成之后进行下载,如果你要下载的是.sof文件,那么就在上图的SOF Manager处进行文件下载,如果下载的是.jic文件,那么就在Programmer中进行下载,其实道理都一样。

点击连续运行按钮,就是上图中红框的位置,就可以看到如上图所示的界面。

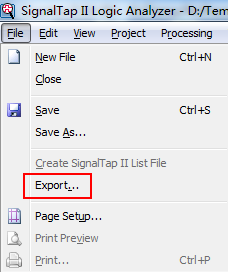

可以点击File->Export将数据导出以进一步分析。导出的数据格式有.csv,.bmp等多种。当然通过停止运行的方式也是可以用来分析数据的。

1、使用的注意点

a) 逻辑分析仪需要硬件支持,所以不是所有的FPGA芯片都支持。

b) 一般流程是:完成设计——编译工程——建立SignalTapII (.stp)文件并加入工程——重新编译——下载设计到FPGA——在Quartus II软件中显示被测信号的波形;在测试完毕后将该逻辑分析仪从项目中删除。

c) 采样时钟决定了显示信号波形的分辨率,此时钟应该大于被测信号的最高频率。

d) 逻辑分析仪的有些信号不可测量,如下:逻辑单元的进位信号(进位链)/PLL的时钟输出/JTAG引脚信号/LVDS信号

2、在设计中增加signalTap II,引起的问题和解决方法

FPGA的资源是有限的。设计已经占用了可观的资源(%的LE,%的MB),signaltap还要和设计抢占资源。“抢占”在这里是很贴切的,既包括抢占LE、MB,还包括布局资源和布线资源。我把“抢占”造成的影响叫做“测不准原理”。这一原理是贯穿signaltap调试始终的一条基本原理。一句话来说,就是“对信号的观察会对信号引入影响”。这些影响绝大部分表现不出来,或者是没有刻意去观察;但是表现出来的影响是原有的设计功能发生了变化。有的变化是原有的bug不出现了(这应该看作是坏的变化),有的变化是新的bug出现了。

据我分析,造成这些影响的可能原因有以下几个:

1)signaltap工具本身存在bug。这一点我无法证实,只是猜想。signaltap的原理是在设计的网表中插入触发逻辑和存储逻辑以及用于和PC机通讯的虚拟JTAG链路实现嵌入式逻辑分析仪功能的。这一插入过程是由QUARTUS软件完成的,对用户是不可见的。由于用户无法控制和约束这一过程,加入signaltap后的电路功能与用户设计初衷相违背也是可能的。

2) 被观察的信号扇出变大,造成设计的时序余量发生变化。实现触发逻辑需要在信号路径上加入触发器和组合逻辑,这样一来必然造成被观察信号的扇出变大,信号的输出延时增大。如果被观察信号的时序很紧张的话,加大信号的延时可能使时序关系变好(原有的bug不出现了),也可能恶化其时序(bug出现得频繁了或新的bug出现了)。

3) 由于“抢占”的存在,造成设计的时序余量发生变化。由于触发逻辑和存储逻辑的加入,FPGA的资源要重新分配。原设计在FPGA内的布局位置和布线资源会发生变化,时序也会受到影响。往往加入signaltap后,布局布线后的时序分析结果会比原来差。

解决上述矛盾的方法是尽可能少地添加被观察信号,常用的几个方法是:

1) 在每次重新编译之前,对信号的保留做一个评估,如果被观察信号被证明与要查找的问题无关,就删除这个信号。

2) 在每次编译成功之后,要查看编译报告,如果系统的逻辑资源利用比例在95%以上,就要考虑去除一些被观察信号或去除几个触发级别,或者减小采样深度。

3) 如果有必要的话,把仅需要作为触发条件的信号的采样使能关闭也能显著减少逻辑资源的占用。

4) 系统存储资源的占用比例也要考虑在内,不可占用太多。与此相关的选项是采样深度、信号个数、信号的采样使能是否关闭。

5) 编译成功后,要查看时序分析报告。如果系统时序下降很大或者被观察信号的时序不能满足,要考虑采用上面的方法减少对逻辑资源的占用。

另外,采样时钟的选择对系统的整体时序影响也很大。选取的原则是:

1) 尽可能从设计的顶层选择信号作为采样时钟,而不是随便把哪个module的输入时钟作为采样时钟,以利于QUARTUS优化全局时钟资源的利用。

2) 在保证观察精度的前提下,选择较低频率的时钟。

采样时钟本质上是触发条件之一(最基本的触发条件),如果恰当的选取非时钟信号(没有确定频率的信号)作为采样时钟,可以起到事半功倍的效果。