使用Quartus设计FPGA,简单包括以下流程:

- 新建工程,写代码

- 编译工程,找错误

- 分配引脚,重编译

- 下载配置,到硬件

为保证设计的正确性,在编译后,一般还需要做仿真验证,然后下载至硬件,有两种仿真方式:

- 功能仿真

- 时序仿真

新建工程,写代码

-创建工程文件夹

在电脑上新建一个文件夹,例如E:\Lianxi_1。工程的文件将全都存在这个文件夹内,便于管理。一个工程对应一个文件夹。

-新建工程

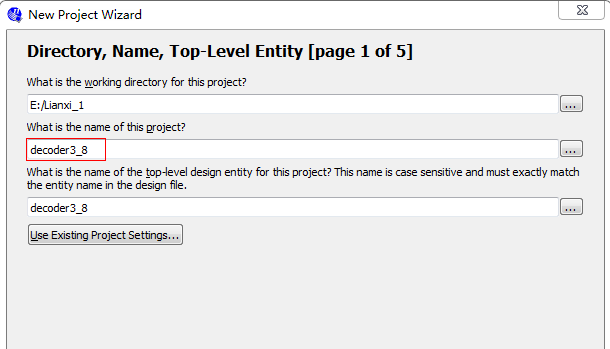

打开QuartusII,File->New Project Wizard…如下图:

第1个,选择工作目录:选刚才建立的空文件夹.

第2个,填入工程名称。要有意义,比如要做一个38译码器,工程名就叫decoder3_8,不要使用中文。

第3个,顶层设计实体名,默认。

↓

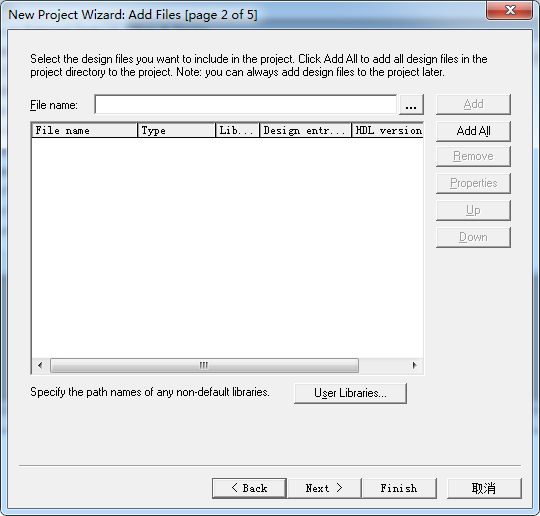

Next… 下图,添加已有的源代码文件,没有的话,点Next

↓

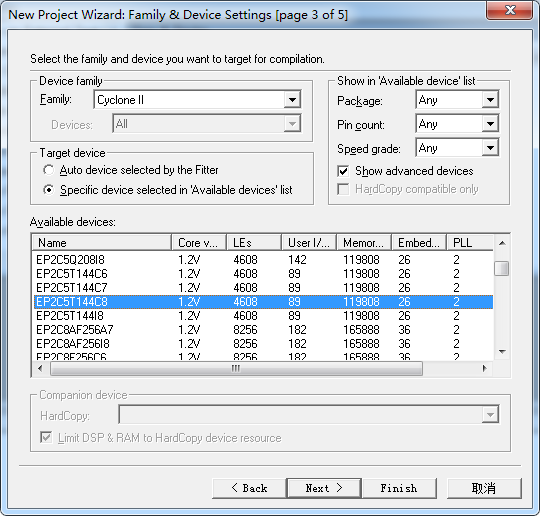

下图,选FPGA型号,根据你FPGA芯片上印刷的型号选择。

比如,我使用的芯片型号如下:

Family: Cyclone II

Device:EP2C5T144C8

↓

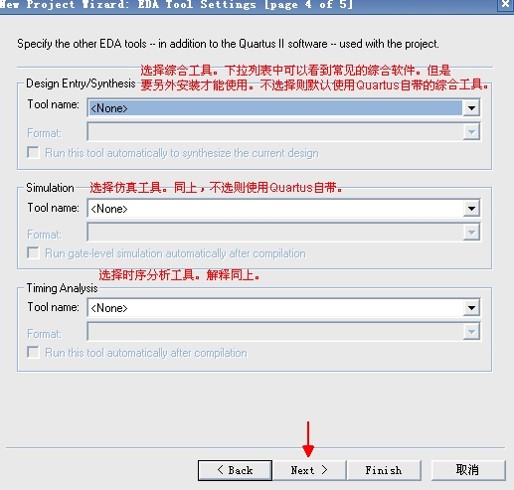

Next…下图,选择综合、仿真、时序分析工具. 此处如果全部选择None,表示用Quartus自带的工具。

注:Quartus 9.1以后的版本不再自带仿真工具,需要安装Modelsim之类的软件来仿真。

↓

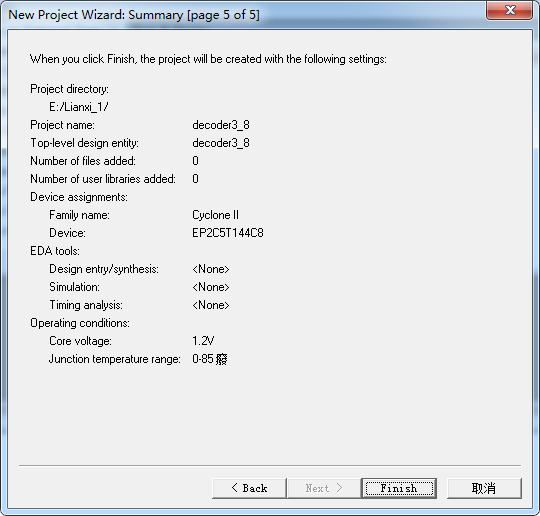

Next.. 下图,是前面设置的信息的总览,检查无误就点Finish

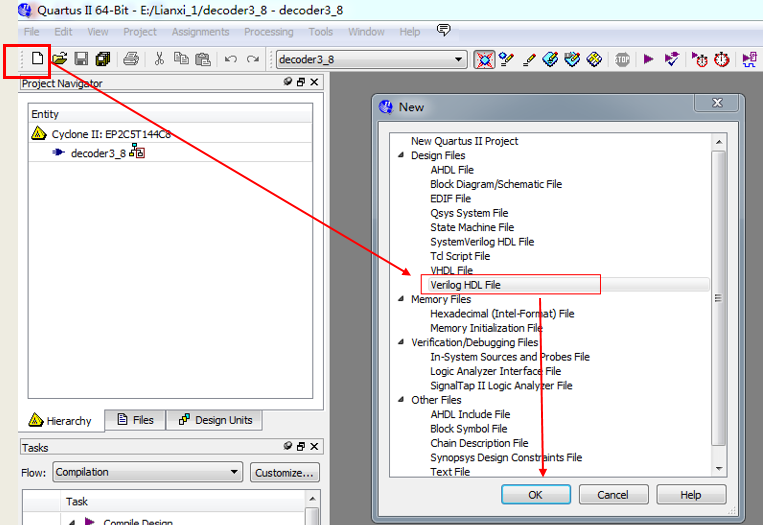

- 写代码

↑

新建VerilogHDL文件,写代码,保存时,文件名要与module后面定义的实体名一致。即,保存decoder3_8.v到你的工程文件夹内。

module decoder3_8 (data_out, data_in ) ;

input [2:0] data_in;

output [7:0] data_out;

reg [7:0] data_out;

always @(data_in)

begin

case (data_in )

3'b000: data_out=8'b11111110;

3'b001: data_out=8'b11111101;

3'b010: data_out=8'b11111011;

3'b011: data_out=8'b11110111;

3'b100: data_out=8'b11101111;

3'b101: data_out=8'b11011111;

3'b110: data_out=8'b10111111;

3'b111: data_out=8'b01111111;

default: data_out=8'bxxxxxxxx;

endcase

end

endmodule保存为 decoder3_8.v

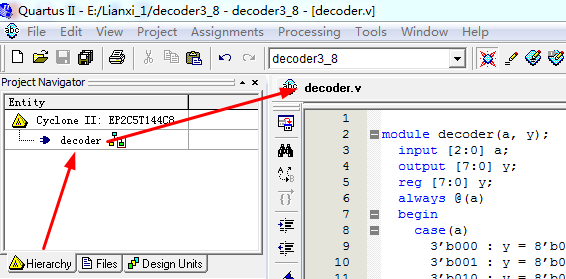

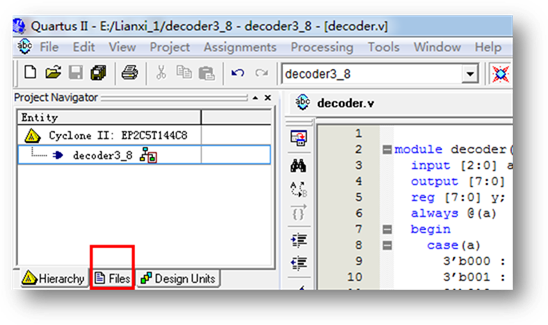

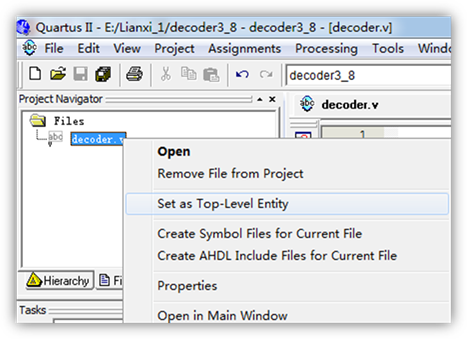

将此源文件设置为顶层文件,如下图:

导航窗口Project Navigator下边→点Files

右击文件decoder3_8.v

设为顶层实体Set Top-Level Entity

再点击工程架构Hierachy,检查顶层架构是否为当前顶层文件。

说明:一个工程内,可以有多个源代码文件。但只有一个是顶层文件,代表最顶层设计,它可以引用工程目录内的其他源文件。

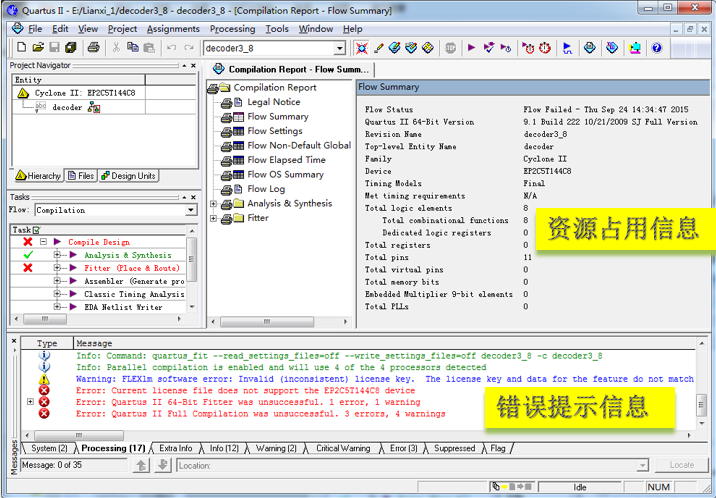

编译工程,找错误

编译:Processing–>Start Compilation

编译不成功时,下方会有红色提示信息,请仔细检查语法,双击红色提示信息,可以直接定位到错误代码附近位置。

修改后重新编译,直至修改完所有错误。

编译成功,只是语法没有错误,但并不代表设计就是完全正确的。

我们可以通过仿真来检查设计是否符合预计的功能。

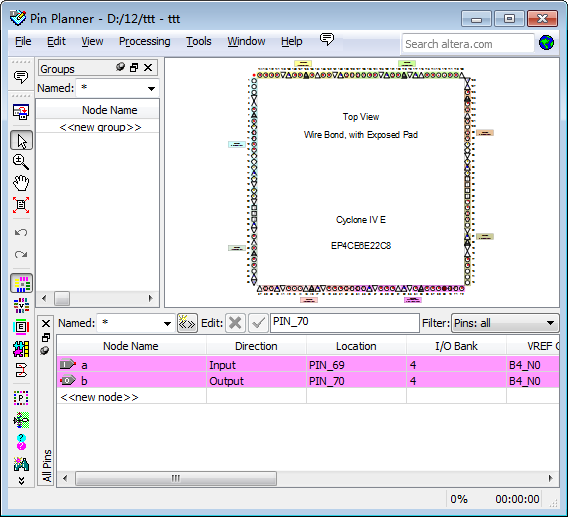

分配引脚,重编译

前面的设计完成后,开始分配引脚

说明:FPGA引脚众多,大部分引脚都可以任意设置为输入或输出,我们可以将本工程中输入输出分配到任意可分配的引脚上。当然,对于已经做好的硬件开发版来说,有些按键、显示灯等已经事先与FPGA连接好了,所以分配引脚的时候要根据硬件电路原理图正确分配引脚。

分配引脚操作:Assignment -> Pin Planner,如图。分配完引脚,关闭窗口,重新编译工程。

下载配置,到硬件

下载程序到FPGA,有多种方式,我们一般用USB-Blaster。

-连接下载器

• 将USB-Blaster的USB端插电脑上,另一端10针接头接FPGA板上的JTAG插座。

• 用一根USB线给FPGA板供电。

如果你的电脑第一次使用USB-Blaster下载器,需要为它安装驱动:

方法:我的电脑右键->设备管理器->USB-Blaster右键->更新驱动->定位到Quartus安装目录C:\altera\9.0\quartus\drivers\usb-blaster,等待安装完成。

-下载

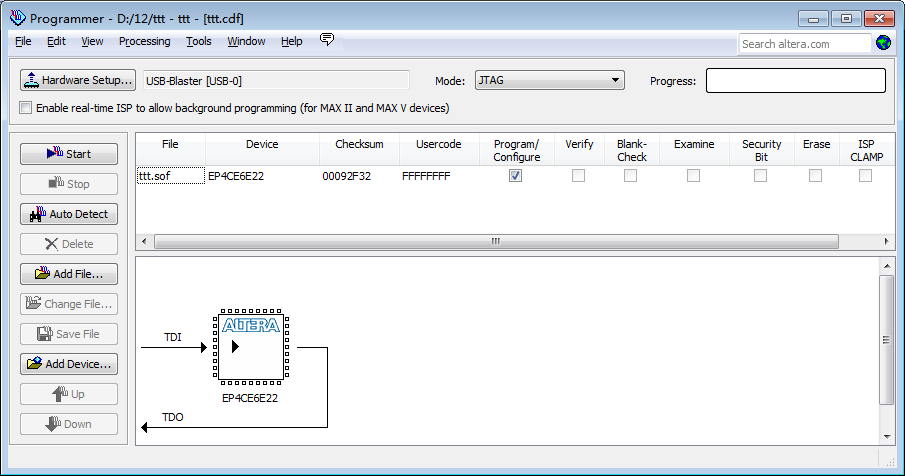

菜单Tools -> Programmer,下图

左上方,点Hardware Setup…->下拉选择USBBlaster->Close.

界面顶部中间选下载方式,Mode: JTAG

左侧,按Start下载 .sof文件。

OK,测试硬件功能是否正确吧。