FPGA学习之嵌入式硬件系统(SOPC)概述(软硬件设计)

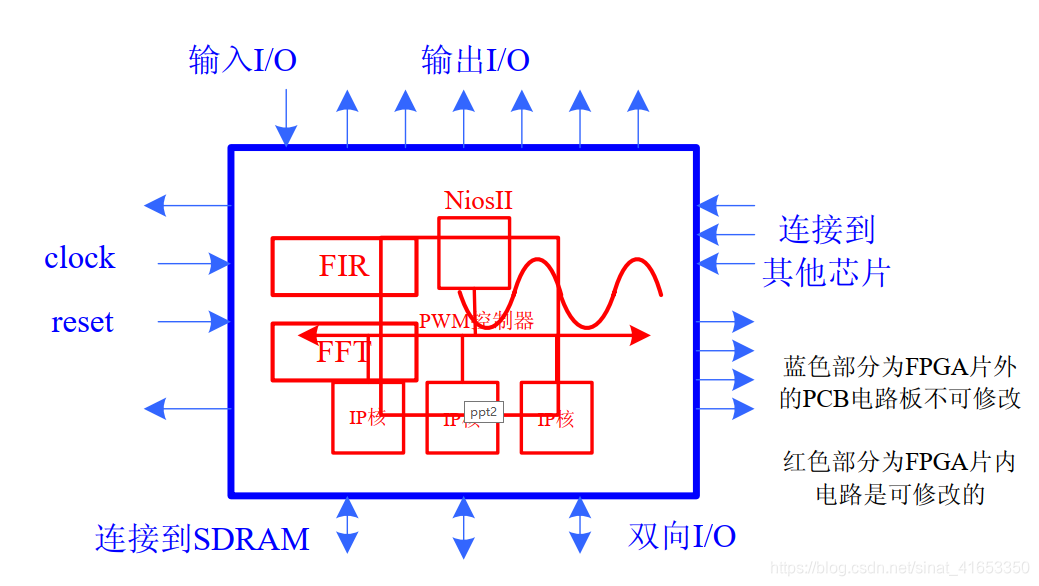

首先我们知道FPGA可以实现充当完整微处理器的逻辑,并且提供许多灵活性选项。下图体现出FPGA器件为何是现场可编辑门阵列器件。

为了使基于FPGA的嵌入式系统能够充当微处理器的系统,那么我们就必须要学习NIOS II (SOPC)系统设计,而且在设计之时系统应包括以下内容,这是因为微处理器和FPGA之间的区别就是FPGA上电时不包含任何逻辑(基于SDRAM工艺所致),我们需要系统运行之前来配置FPGA处理器。

(1)JTAG接口支持FPGA配置以及硬件和软件调试

(2)上电FPGA配置机制

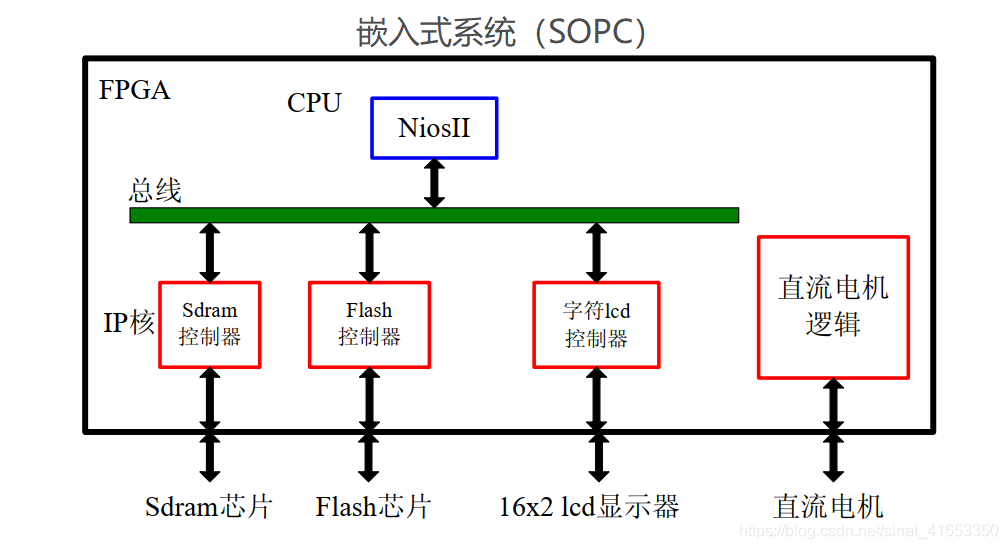

那什么是FPGA嵌入式系统呢?

简单的说,就是在FPGA器件内部放置了一个或多个CPU。

FPGA本身是硬件处理,放置在FPGA内部的CPU就需要软件处理,这样建立的系统就可以协调软硬件之间的联系。

而且这样的系统是可以裁剪的。

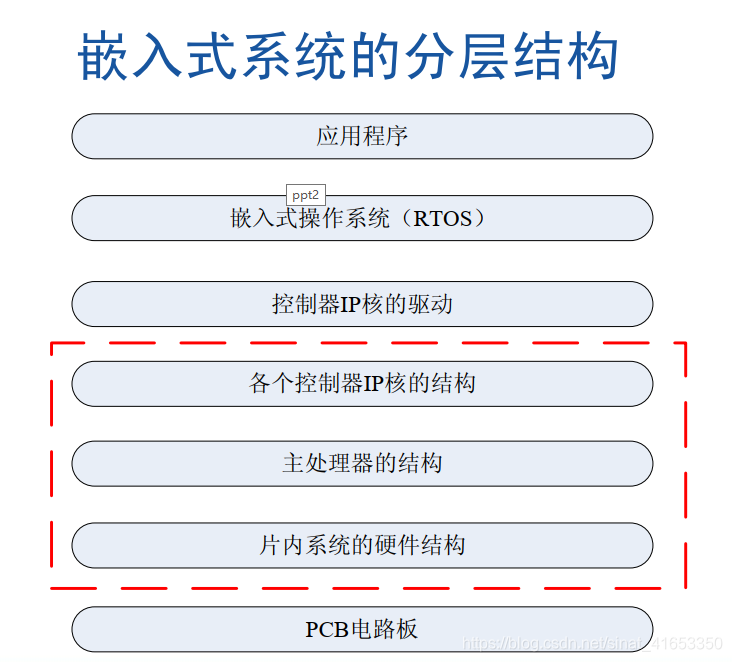

那么SOPC和SOC区别是什么呢?P代表了什么?

一字之差竟是两种不同的模式,而这个可编程性“P”的灵活性有以下两方面:

(1)CPU本身可修改

- CPU规模:三种模式,经济型,标准型和快速型。

- 频率:默认50MHz,可提高或降低

- MMU------Yes/No

- Cache-------iCache指令缓存,dCache数据缓存

- 指令。复杂的数据处理用一条指令完成,起到加速作用

(2)自定义总线的外设

但是在今天的发展中ARM系列编程好像更加吃香,在实际工业应用中NIOS II系统似乎要被淘汰了

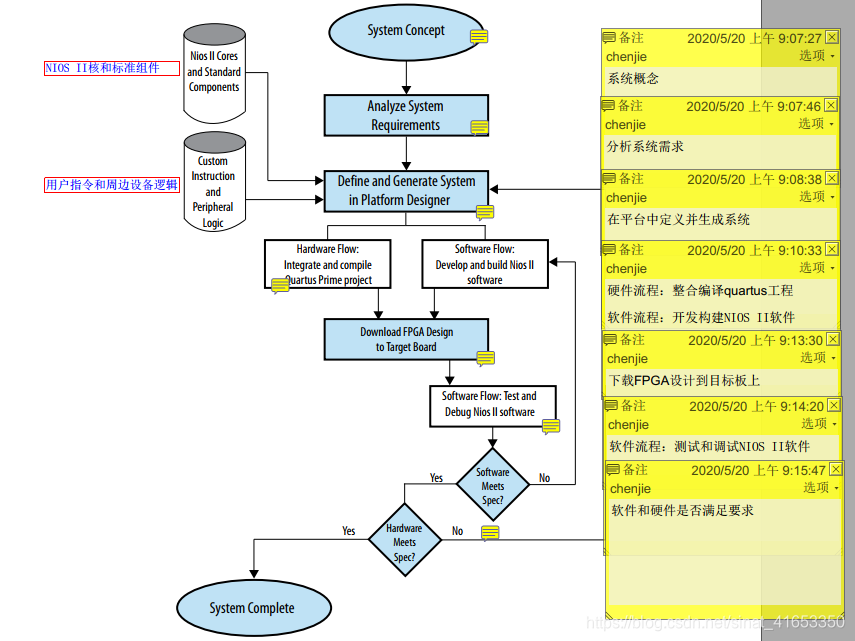

下图是NIOS II系统通用设计流程

由上图流程展示可知在平台中定义和生成系统包含两个方面:一个是硬件设计流程和软件设计流程。而且两个流程所需要的资源是完全不同的,硬件设计需要NIOS II核和标准组件来实现的,软件设计就需要单间用户指令和周边设备系统软件。

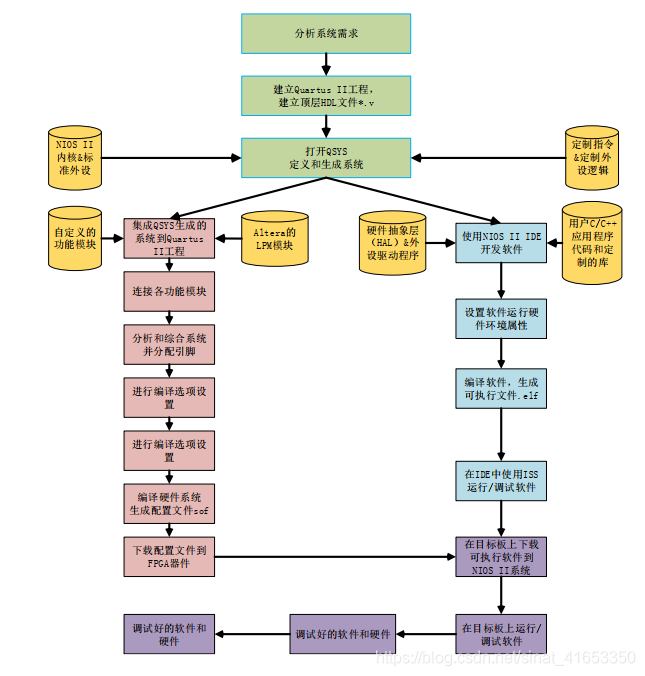

下图是NIOS II 系统硬件设计流程

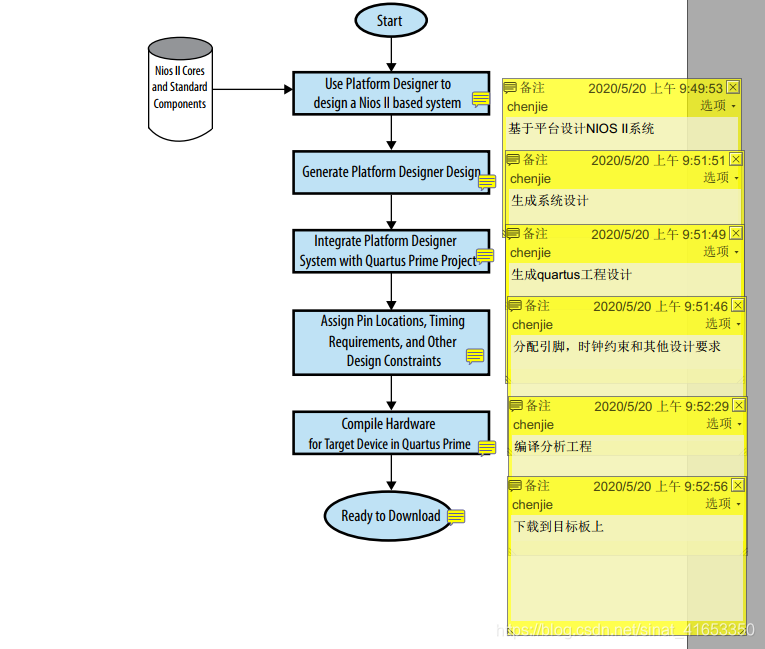

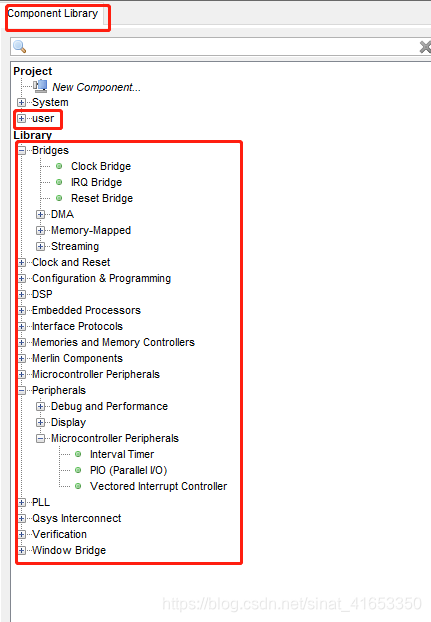

由上图可知在平台设计NIOS II系统硬件时,需要使用NIOS II核和标准组件,可以看出即SOPC系统设计中标准组件即IP核必不可少,而且quartus软件自带基础常用的一些ip核,目录结构如下图,可以看出在组件库里包含如PIO,Bridges等ip核,也有用户自定义的user分组的ip核。具体ip核如何使用及如何自定义ip核将在后期学习记录。

在上述硬件设计流程中还看出我们需要对系统进行时钟约束,而且这一步是必不可少的,因此在对NIOS II系统设计时我们会开始进入时钟约束这一单元学习,因为在之前的Verilog语法实现的简单系统,时钟约束可有可无,显得不怎么重要,但是在NIOS II硬件系统中时钟约束是系统成败的关键所在,关系整个NIOS II系统能否正常运行。

由于NIOS II系统软件开发流程涉及到C或C++编程语言,个人对此不太熟练,因此在后期开发过程中,只会涉及到对NIOS II系统软件的介绍,比如如何调用接口,Avalon总线上的静态和动态地址该如何寻找?不会介绍如何进行软件具体设计。