前 言

本文档主要提供评估板FPGA端案例测试方法,适用的开发环境为Windows 7 64bit和Windows 10 64bit。

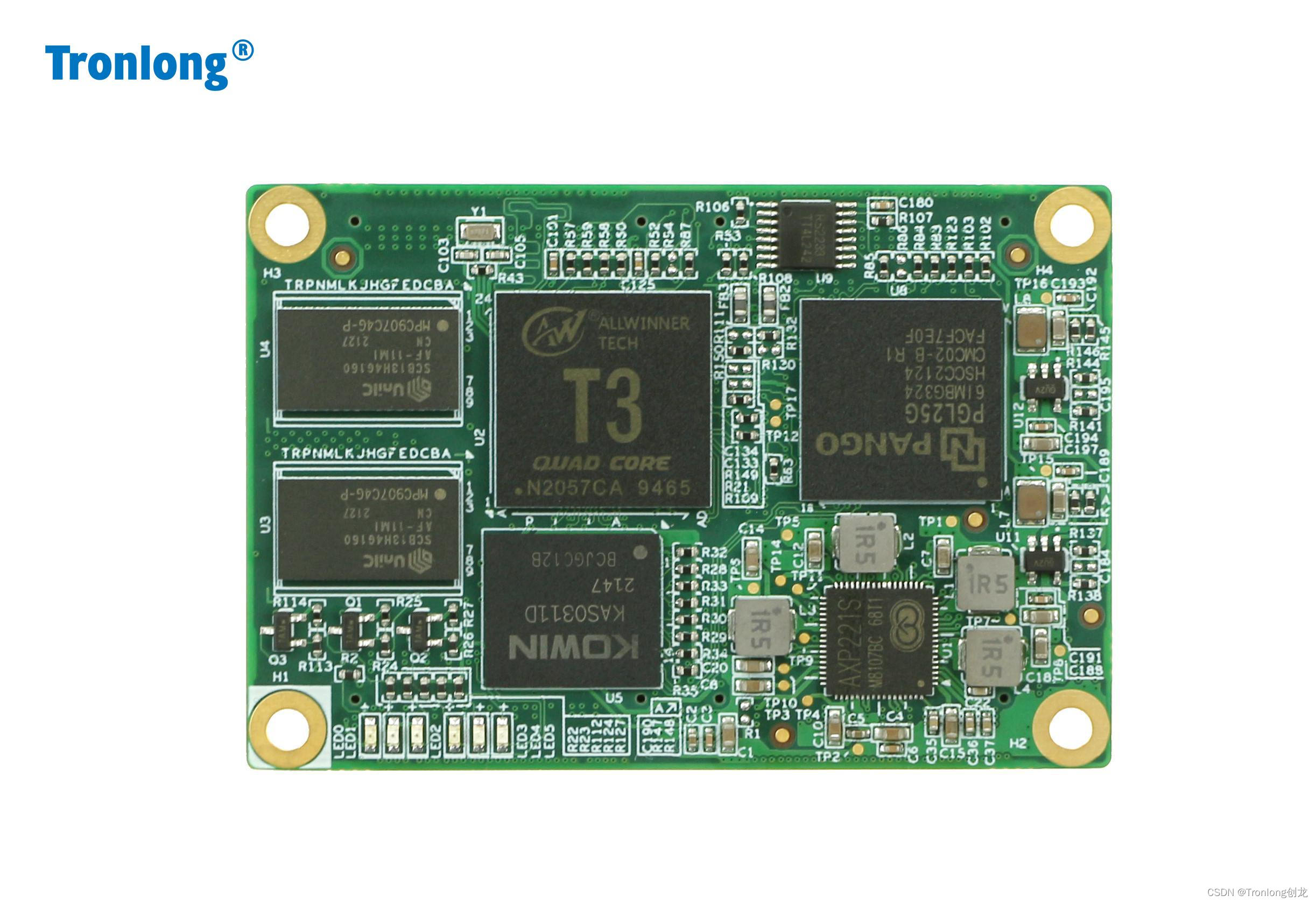

本文案例基于创龙科技的全志T3+Logos FPGA核心板,它是一款基于全志科技T3四核ARM Cortex-A7处理器 + 紫光同创Logos PGL25G/PGL50G FPGA设计的异构多核全国产工业核心板,ARM Cortex-A7处理单元主频高达1.2GHz。核心板CPU、FPGA、ROM、RAM、电源、晶振、连接器等所有器件均采用国产工业级方案,国产化率100%。

核心板内部T3与Logos通过SPI、CSI、I2C通信总线连接,并通过工业级B2B连接器引出LVDS DISPLAY、RGB DISPLAY、MIPI DSI、TVOUT、TVIN、CSI、GMAC、EMA