今天这篇博客,笔者向大家简单介绍Xilinx FPGA中的Vivado时序约束基础知识,也为后续的学习打好铺垫。

Xilinx Design Constraints (XDC) 概述

• XDC 在本质上就是Tcl 语言,但其仅支持基本的Tcl 语法,如变量、列表和运算符等等,对其他复杂的循环以及文件I/O 等语法可以通过在 Vivado中source 一个Tcl 文件的方式来补充。

• XDC 可以像UCF一样作为一个整体文件被工具读入,也可以在实现过 程中被当作一个个单独的命令直接执行。这就决定了XDC也具有Tcl命 令的特点,即后面输入的约束在有冲突的情况下会覆盖之前输入的约束。

• 不同于UCF是全部读入再处理的方式,在XDC中约束是读一条执行一条,所以先后顺序很重要。设置IO 约束之前,相对应的clock 一定 要先创建好。

• UCF是完全以FPGA的视角看问题,所以缺省认为所有的时钟之间除非预先声明是同步的,否则就视作异步而不做跨时钟域时序分析。

• XDC恰恰相反,ASIC世界的血缘背景决定了在其中,所有的时钟缺省视作全同步,在没有时序例外的情况下,工具会主动分析每一条跨时钟域的路径。

XDC的基本时序约束可以分为时钟约束、I/O 约束以及时序例外约束三大类。

时钟约束

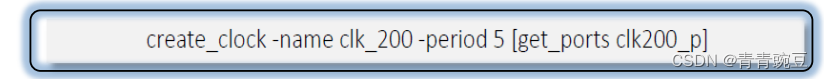

首先时钟约束必须最早创建,对于7系列FPGA来说,端口进来的时钟和GT的输出RXCLK/TXCLK都必须用create_clock自主创建为主时钟,如果是差分输入的时钟,可以仅仅在差分对的P侧用get_ports获取端口,并使用create_clock创建。

其次Vivado自动推导的衍生时钟,MMCM/PLL/BUFR的输出作为衍生时钟,可以由Vivado自动推导无需用户创建。

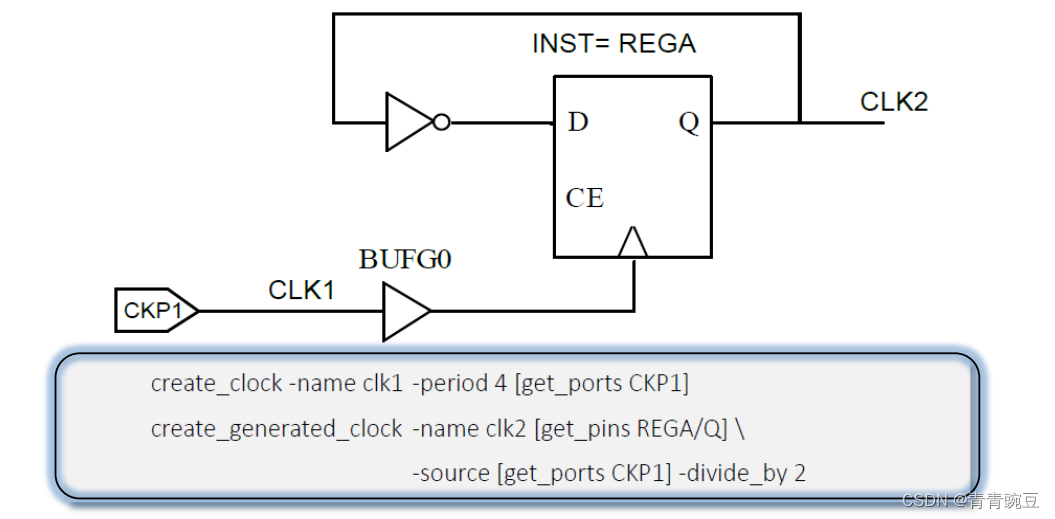

再次存在用户自定义的衍生时钟,工具不能自动推导出衍生钟的情况,包括使用寄存器和组合逻辑搭建的分频器等,必须由用户使用creat_generate_clock来创建,举例说明:

I/O约束

在设计的初级阶段,可以不加I/O约束,让工具专注于满足FPGA内部的时序要求,当时序要求基本满足后,再加上I/O约束跑实现。XDC中的I/O约束有以下几点需要注意:

- 不添加I/O约束的端口时序要求被视为无穷大;

- XDC中的set_input_delay/set_output_delay是从系统的角度来进行约束;

- 典型的I/O时序,包括系统同步、源同步、SDR和DDR等等,在Vivado图形界面的XDC templates中都有示例;

时序例外约束

时序例外约束包括set_max_delay/set_min_delay,set_multicycle_path,set_false_path等,这类约束除了要满足XDC的先后顺序优先级外,还受到自身优先级的限制,不同的时序例外约束和同一约束中的不同条件优先级如下图所示: