时序约束

本文参考:

《综合与时序分析的设计约束—Synopsys设计约束(SDC)实用指南》

《vivado从此开始—to learn vivado from here》

一、时钟周期约束

在设计中说明时钟的SDC指令是create_clock,该指令的BNF(Backus-Naur Form,巴斯科范式)为:

create_clock -period period_value

[source_objects]

[-name clock_name]

[-waveform edge_list]

[-add]

[-comment comment_string]

1、确定主时钟

create_clock 的对象必须是主时钟(Primary clock),通常主时钟有两种情况:

- 时钟由外部时钟源提供,通过时钟引脚进入FPGA。

- 高速收发器(GT)的时钟RXOUTCLK或TXOUTCLK。

vivado 中提供Tcl命令查看未约束的主时钟,不过通过vivado提供的时钟约束向导可以快速的完成基本的时序约束工作。

//确定主时钟

report_clock_networks -name mynetwork

//或者

check_timing -override_defaults no_clock

1)、主时钟之间有明确的相位关系

假设待约束的时钟如下:

可表示为:

create_clock -period 10 -name clka -waveform {5 10} [get_ports clka]

waveform可以省略,默认格式为:{0 周期/2}。有时候需要模拟复杂的波形,比如脉冲消隐,需要在触发器指定的时间范围内删除数据,主要是为了减少射频干扰。如一下波形:

create_clock -period 10 -name clkb -waveform {3 5 8 9}{get_ports clkb}

2)、异步时钟

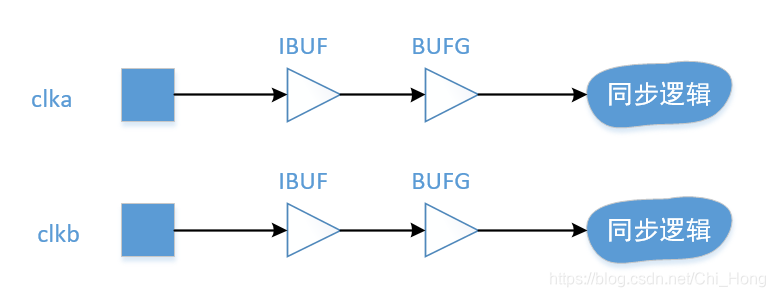

异步时钟通过set_clock_groups命令指定,如下图所示的两个时钟:

create_clock -period 10 -name clka [get_ports clka]

create_clock -period 5 -name clkb [get_ports clkb]

set_clock_groups -asynchronous -group clka -group clkb

//假如两个时钟有生成时钟的情况

set_clock_groups -asynchronous -group [get_clocks clka -include_generated_clocks] -group [get_clocks clkb -include_generated_clocks]

3)、差分时钟约束

差分时钟只约束p端口即可。在一些摄像头CMOS模块中会遇到的差分时钟,可以这样约束:

create_clock -name clkpn -period 5 [get_ports clk_p]

4)、同源多时钟

有时需要在时钟源指定多个时钟,从而满足多I/O速度协议的需求。有时需要验证在不同时钟频率下的运行情况,也会出现同源多时钟的情况。

create_clock -name clk_a -period 10 [get_ports clk]

create_clock -name clk_b -period 8 [get_ports clk] -add

每一个时钟信号需要一个唯一的名称来区别。若对同一个对象指定多个时钟时,没有指定-add选项,那么之前的定义会被覆盖掉。

5)、高速收发时钟

6)、虚拟时钟

虚拟时钟一般只有在创建输入或输出延迟的时候才会被使用。分为两种:

- 传输给FPGA的数据所用到的捕获时钟是由FPGA内部生成的,与主时钟频率不同。

- PCB上有Clock Buffer导致时钟延迟不同。

//捕获时钟是由FPGA内部生成

create_clock -name sysclk -period 10 [get_ports clkin]

create_clock -name vclk -period 5

set_input_delay 2 -clock vclk [get_ports din]

//PCB上有Clock Buffer导致时钟延迟不同,假设延迟1ns

create_clock -name sysclk -period 10 [get_ports clkin]

create_clock -name virclk -period 10

set_clock_latency -source 1 [get_clocks virclk]

set_input_delay -clcok virclk -max 4 -min 2 [get_ports din]

二、两种时序例外

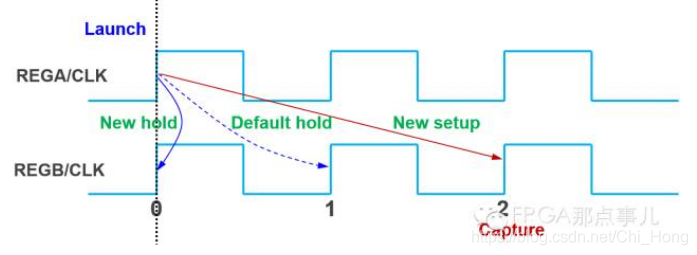

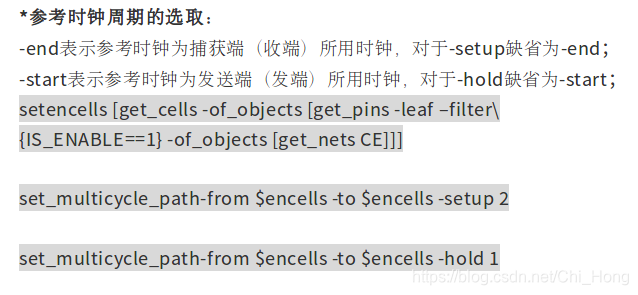

1、多周期路径

工程实践中会存在这种情形:数据路径裸机较为复杂,导致延时过大,使得数据无法在一个周期内稳定下来;或者数据在发送几个时钟周期以后逻辑才使用。设计者的意图是,从发起沿数个时钟之后捕获数据。fpga那点事儿的文章中有这么个例子:

2、虚假路径

虚假路径或称为伪路径是指基于该路径的电路功能不会发生或者该路径无须时序约束。

set_false_path -from [get_cells {opb_r_reg}] to [get_cells {dout_reg}]