引言

DFT是ASIC芯片设计流程中不可或缺的环节。其主要目的是在芯片前端设计验证完成后插入一些诸如寄存器链等可供测试的逻辑,算是IC后端设计的范畴。主要是在ASIC芯片流片完成后,通过这些已插入的逻辑,检测流片得到的芯片的制造质量。检测一些固定故障等。

学习参考

- 数字系统测试和可测试性设计。【美】赛纳拉伯丁 - 纳瓦比 著。原本和译本。

- 修真院讲解视频。

- E课网 DFT 课程。

- 华中科技大学IC设计中心 陈新武 讲稿《集成电路测试方法研究》。

- Design-for-Test: Scan and ATPG Training Student Workbook ,Copyright Mentor Graphics。

简单理解DFT

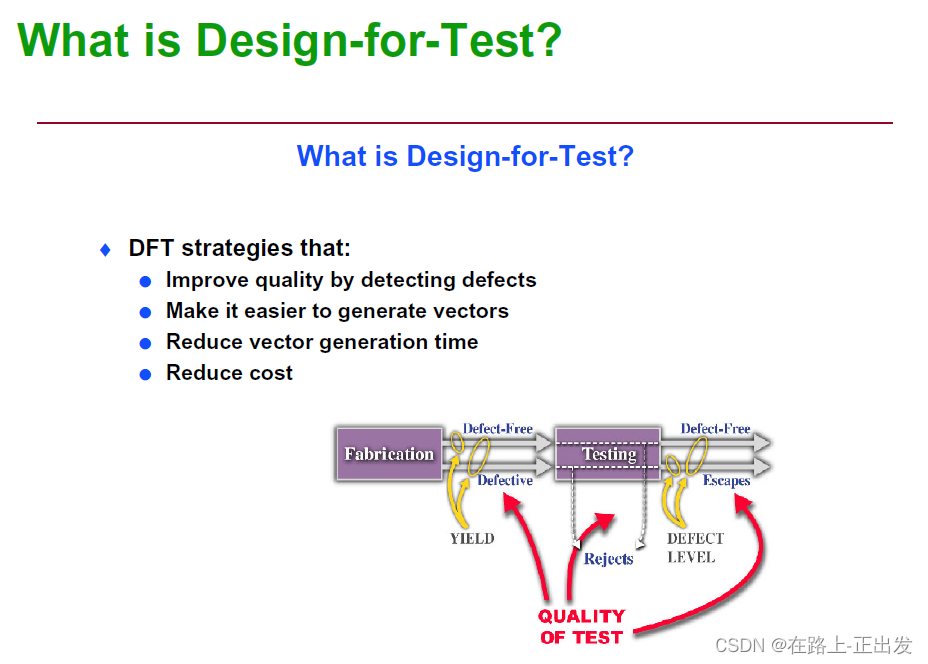

增加一些硬件开销来实现一些辅助性测试设计。需要产生一些高效的测试向量用于测试。DFT不只是插入一些设计的逻辑还包括具体的测试向量产生、测试结果分析等。

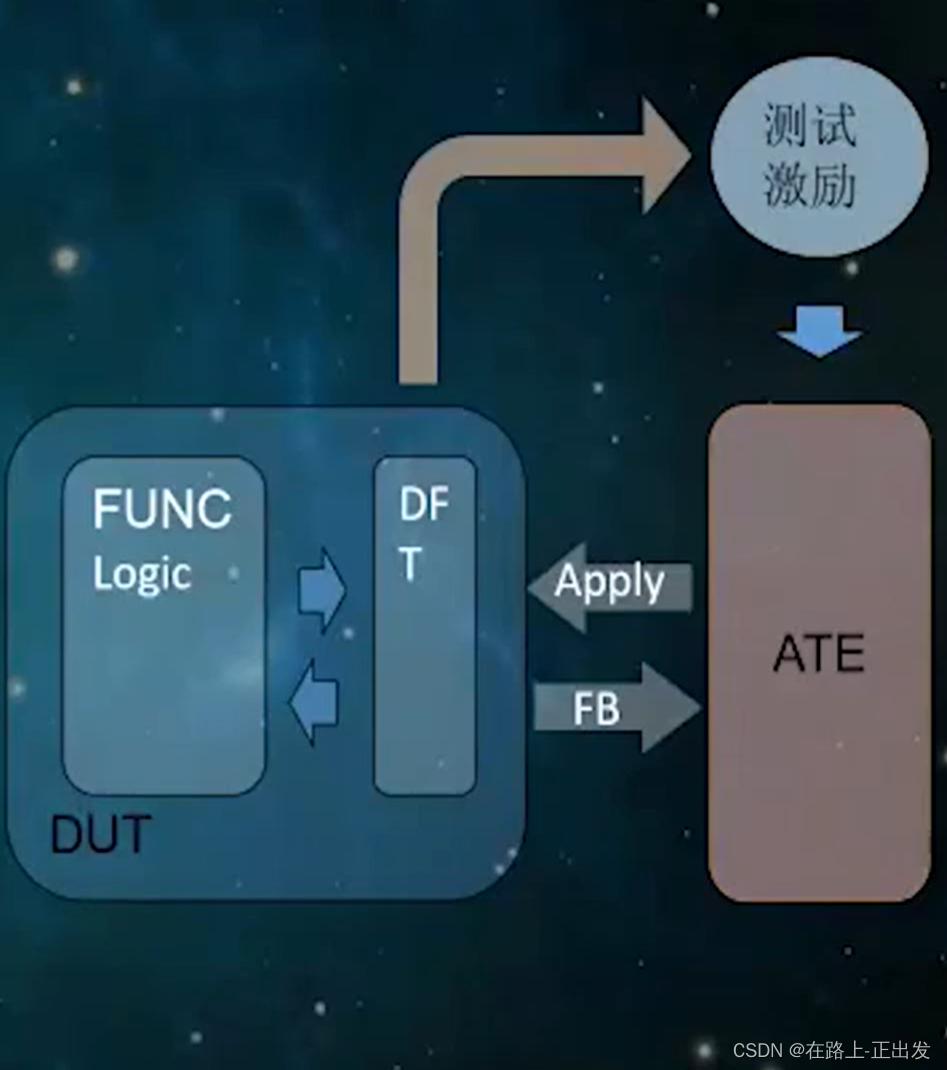

ATE是自动测试机,将测试向量通过ATE激励DUT,DUT的反馈给到ATE,ATE比对收到的响应和期望的响应是否一致,完成对DUT的测试。

DFT策略

可测试性电路示例

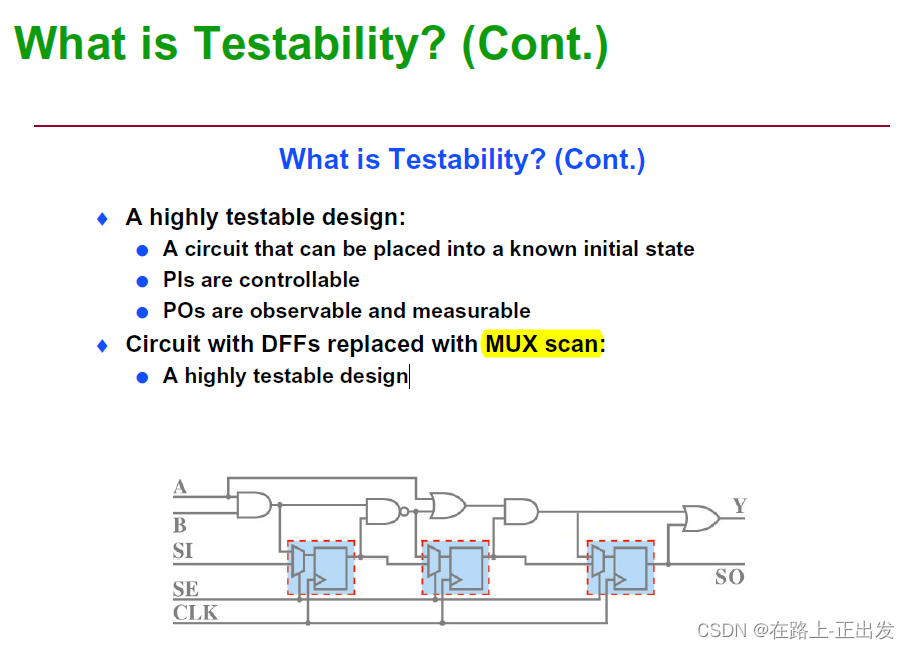

寄存器会被替换为带有MUX的寄存器链,当SE为1时,各个寄存器首尾相接连接成一条寄存器链将测试输出的数据串行输出。

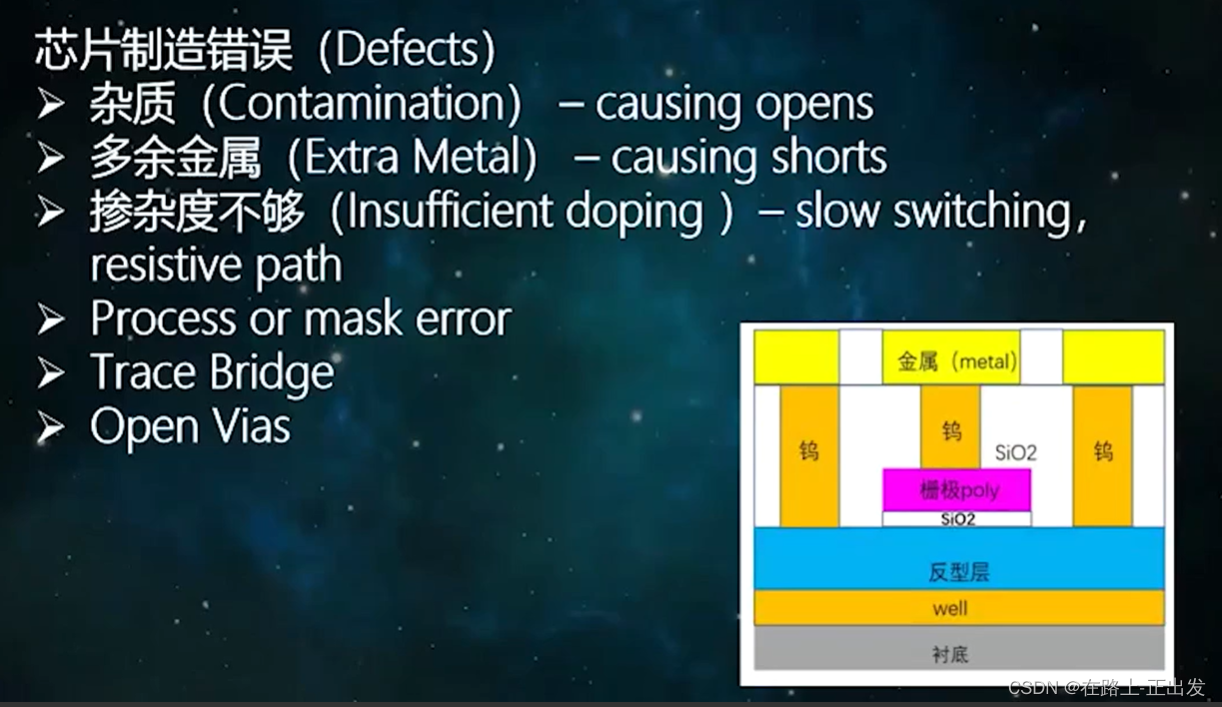

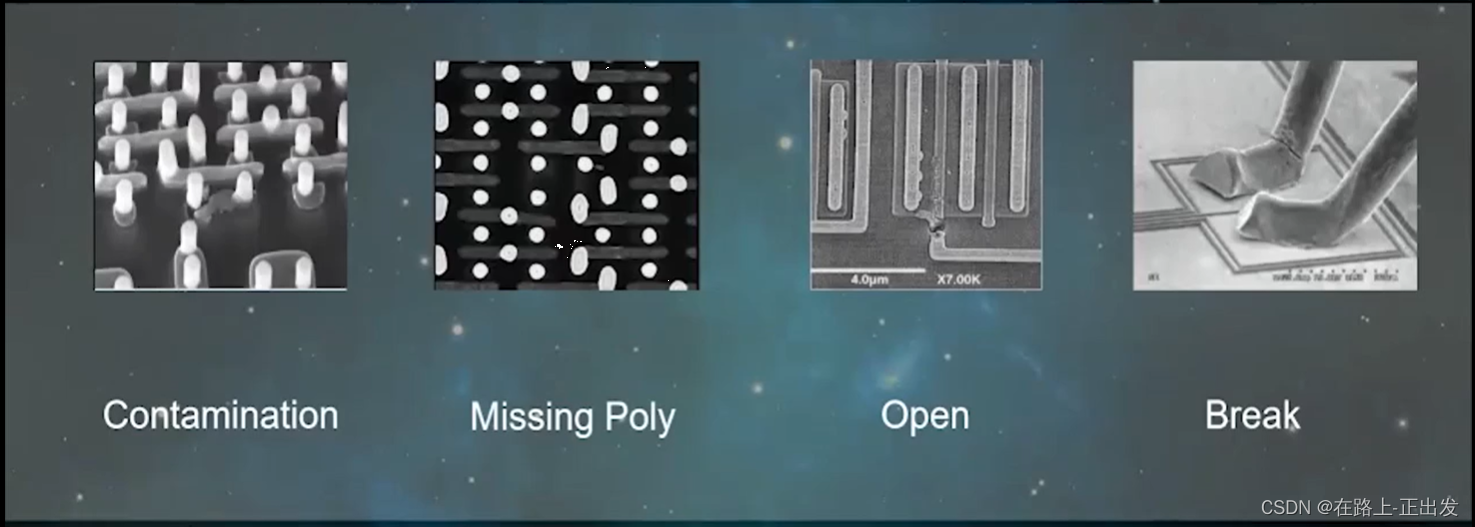

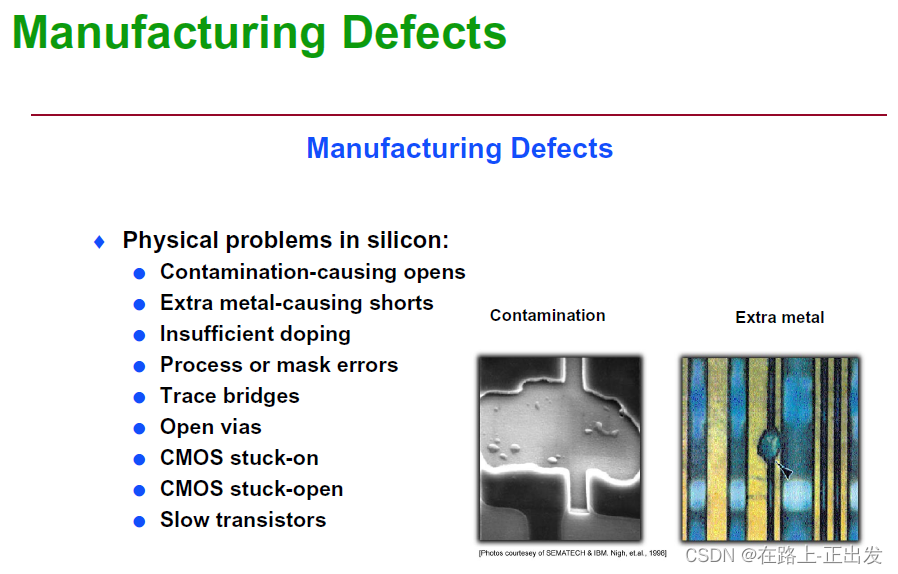

芯片制造故障

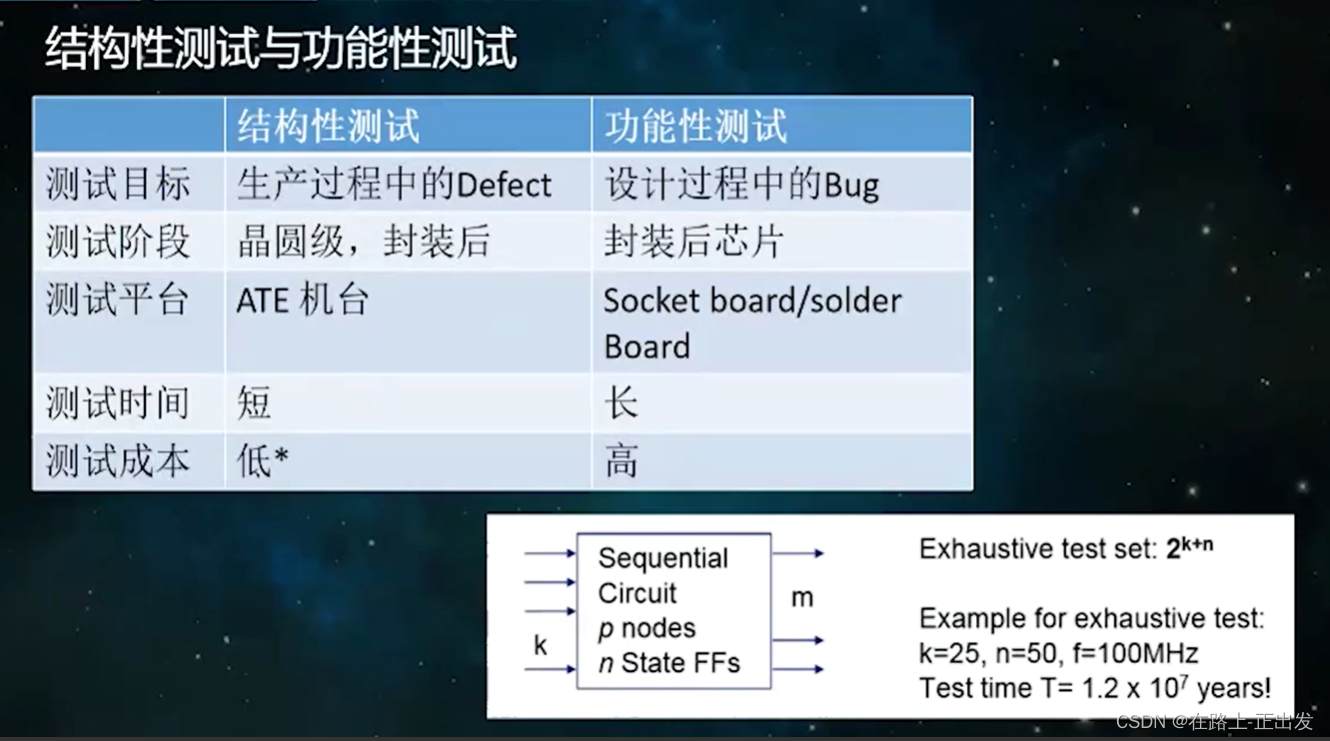

结构性测试与功能性测试

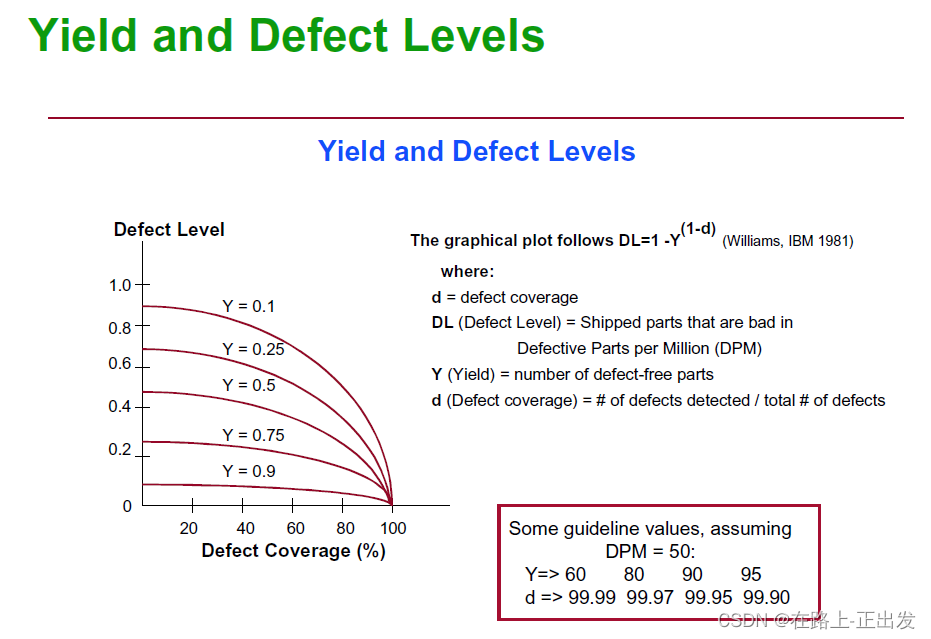

成品率和质量的关系

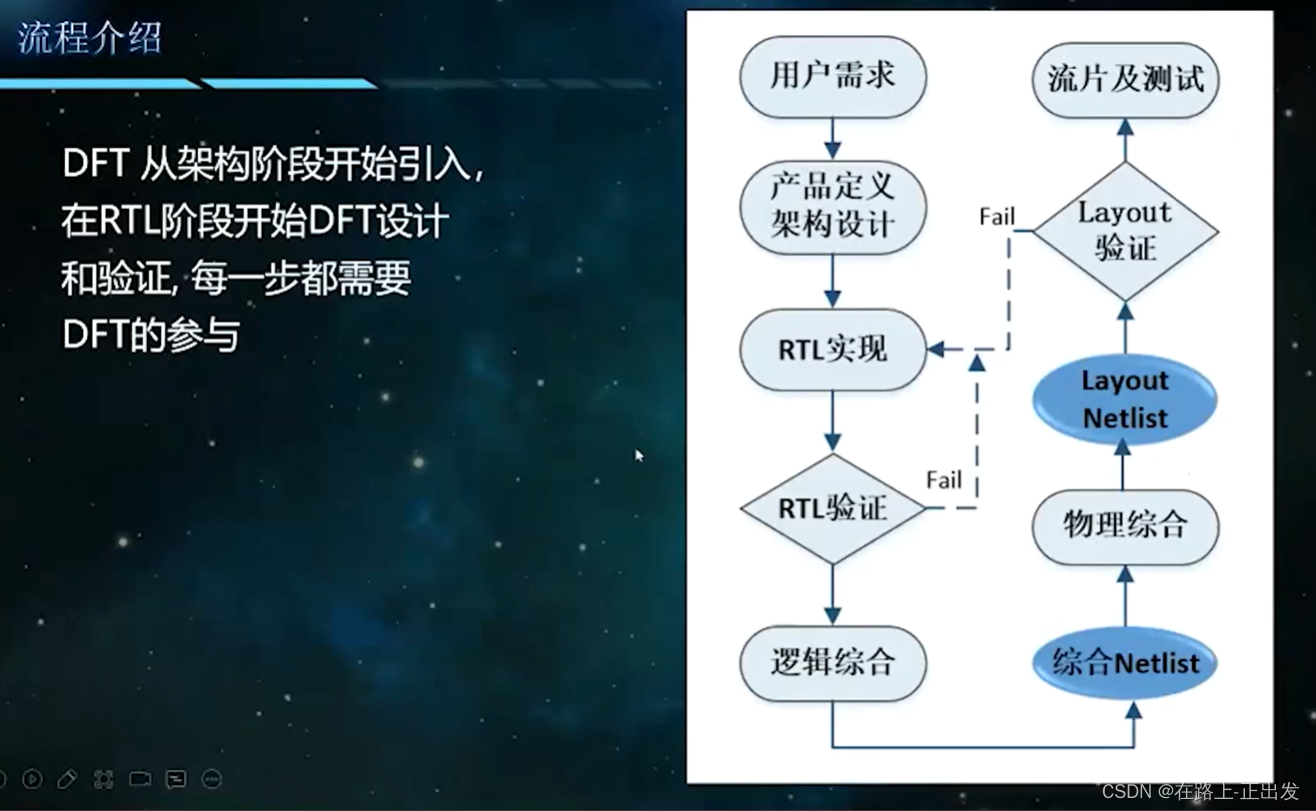

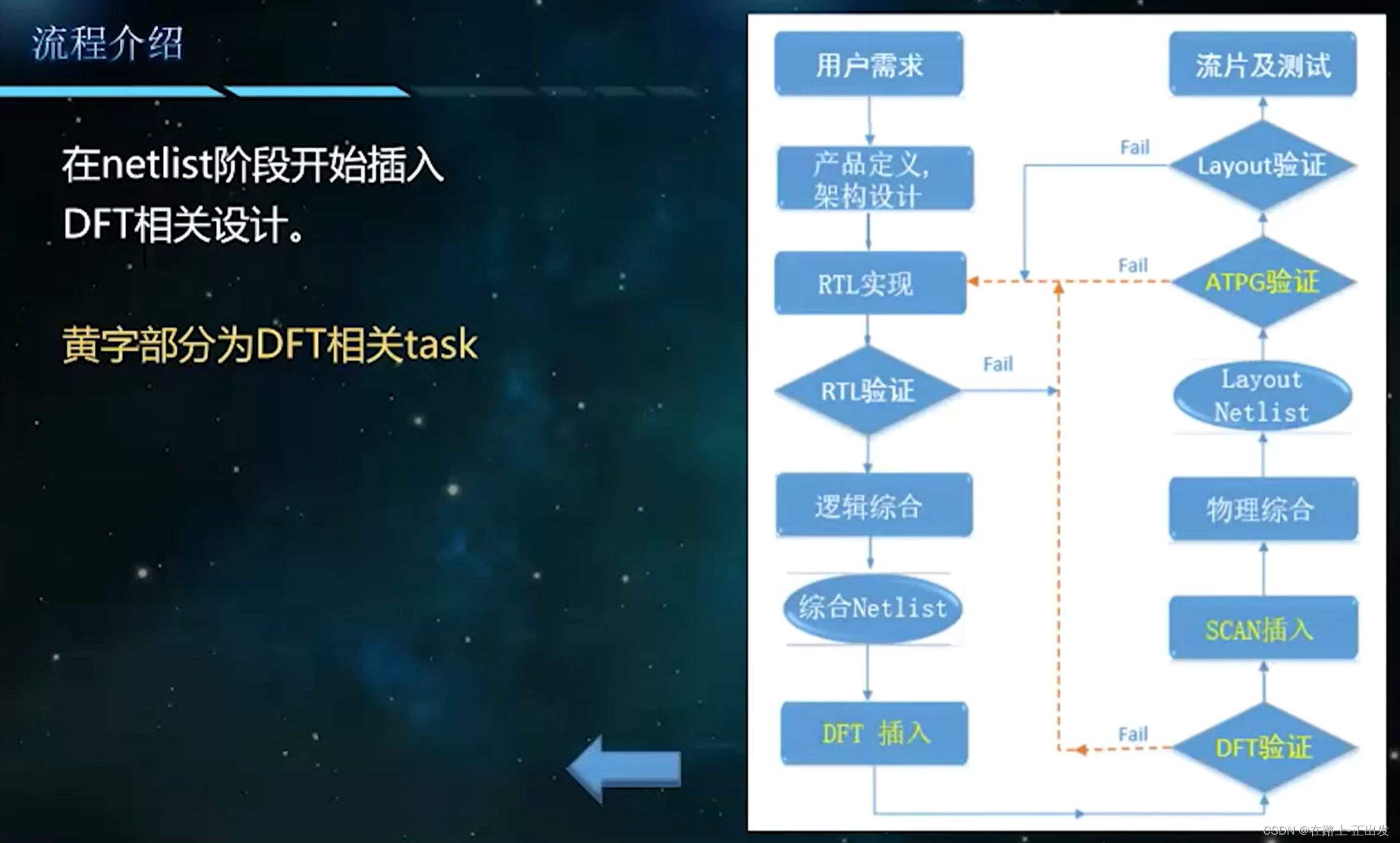

设计流程

DFT全程参与:

DFT后期参与:

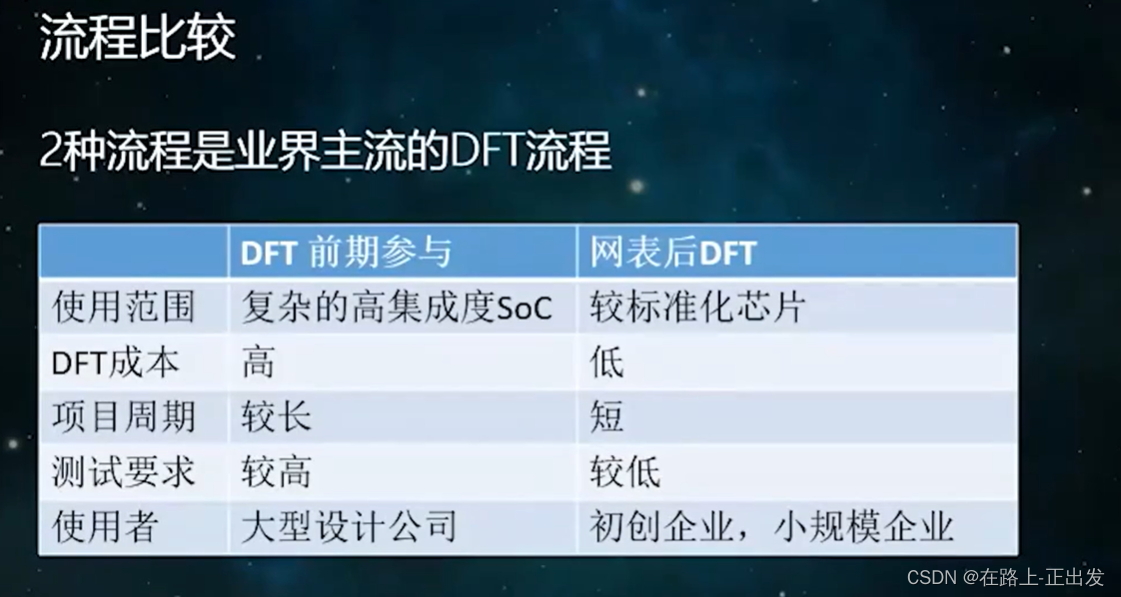

二者比较:

测试方式

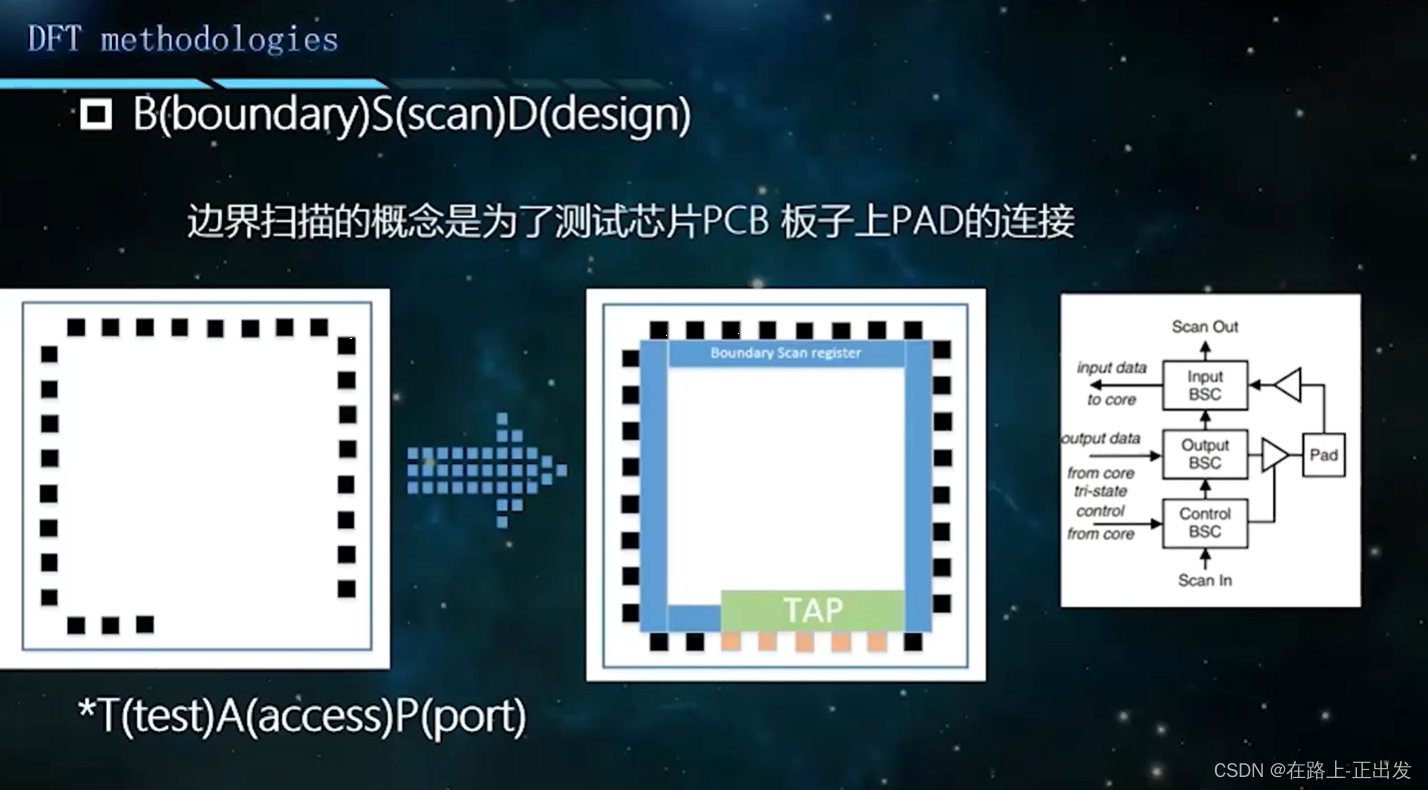

边界扫描:

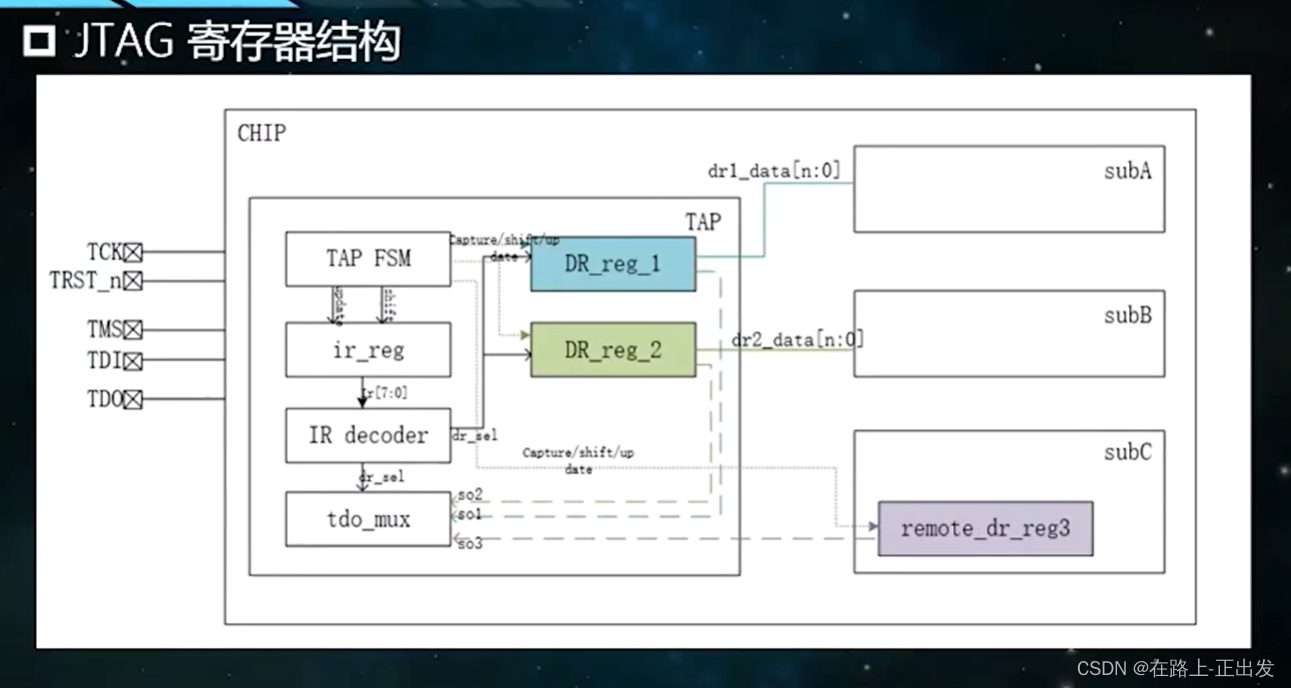

JTAG寄存器结构

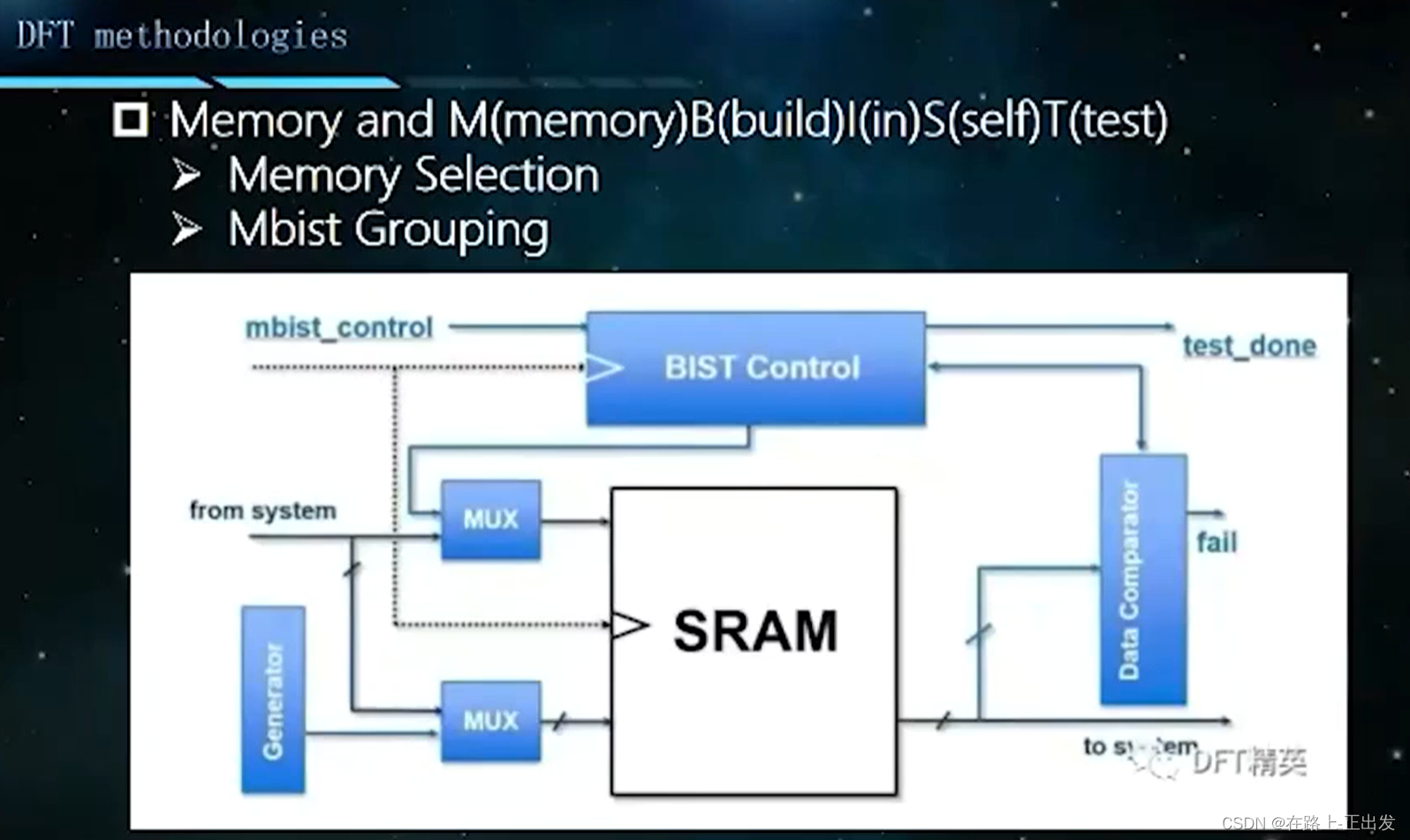

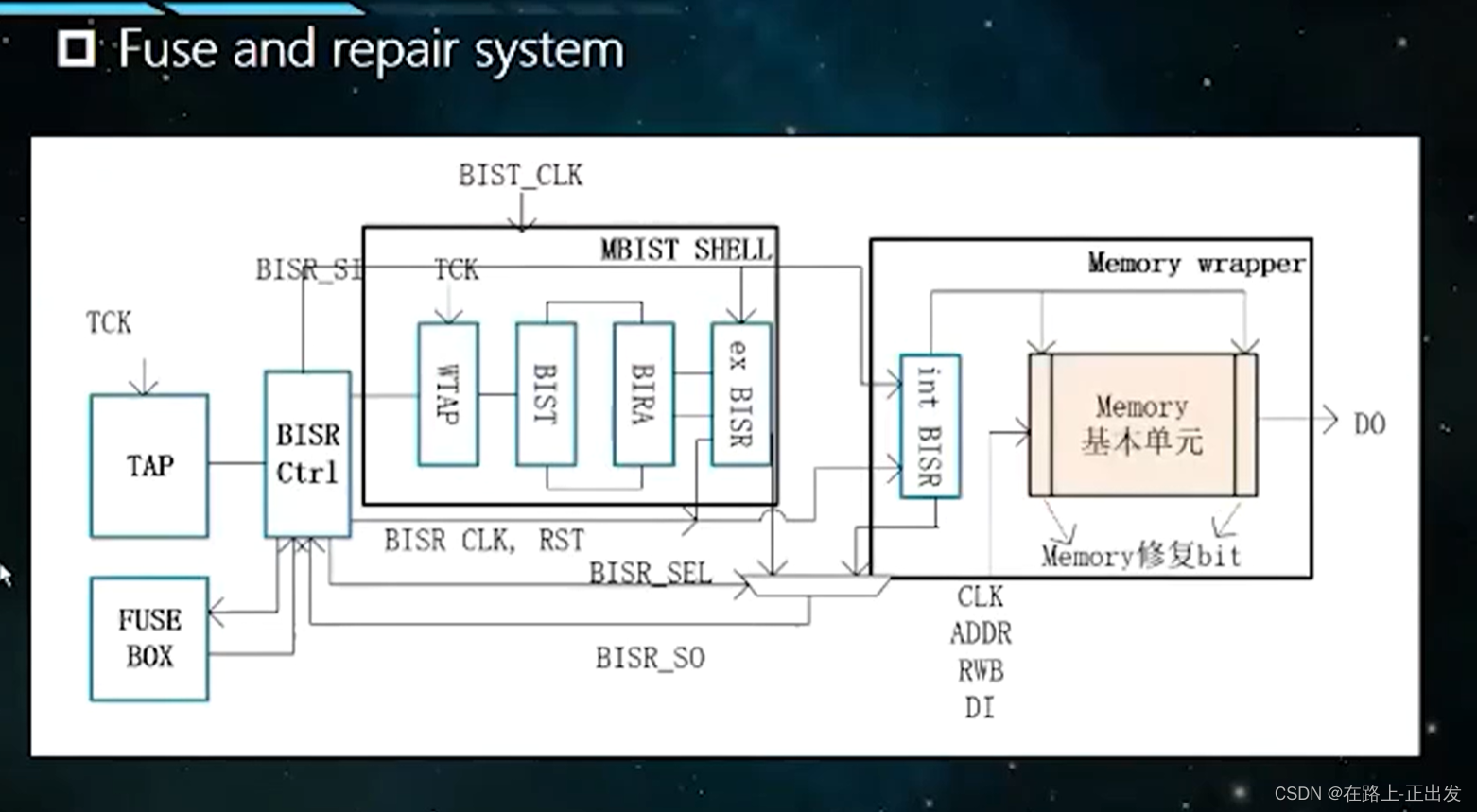

MBIST测试结构:

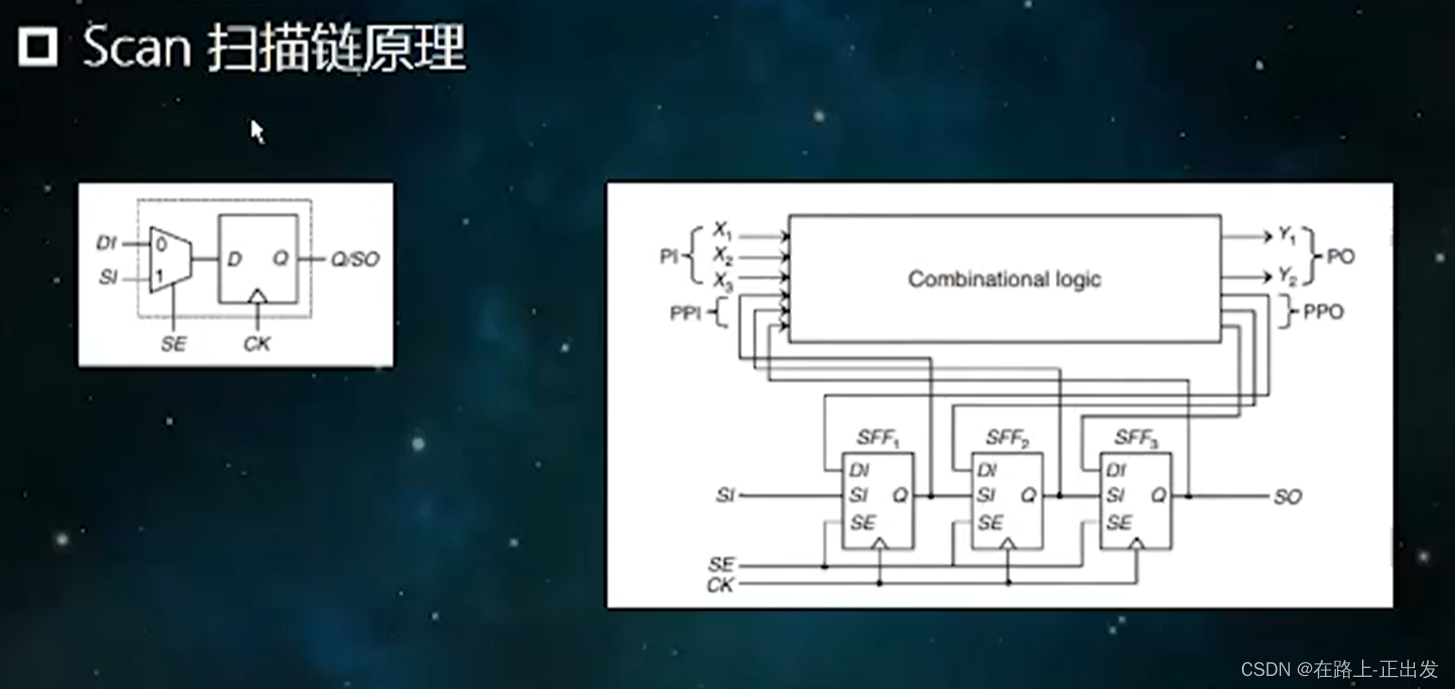

扫描链

将普通的D触发器替换为带有MUX的D触发器,实现扫描链的电路功能。

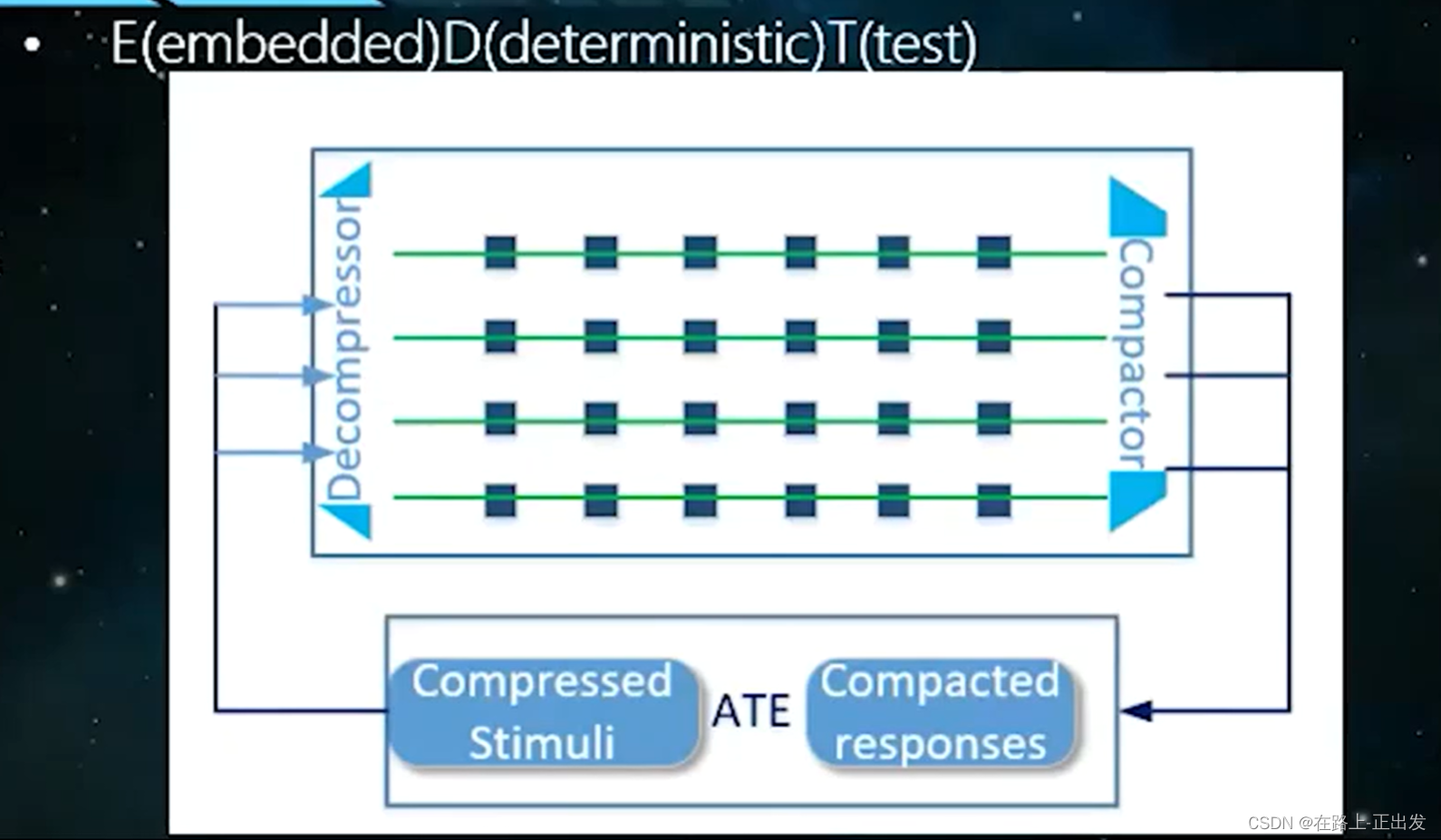

压缩激励/响应

在大型的集成电路中,需要测试的功能有很多,但是可以供使用的IO很少,或者内部的扫描连很长,导致测试时间成本很大。

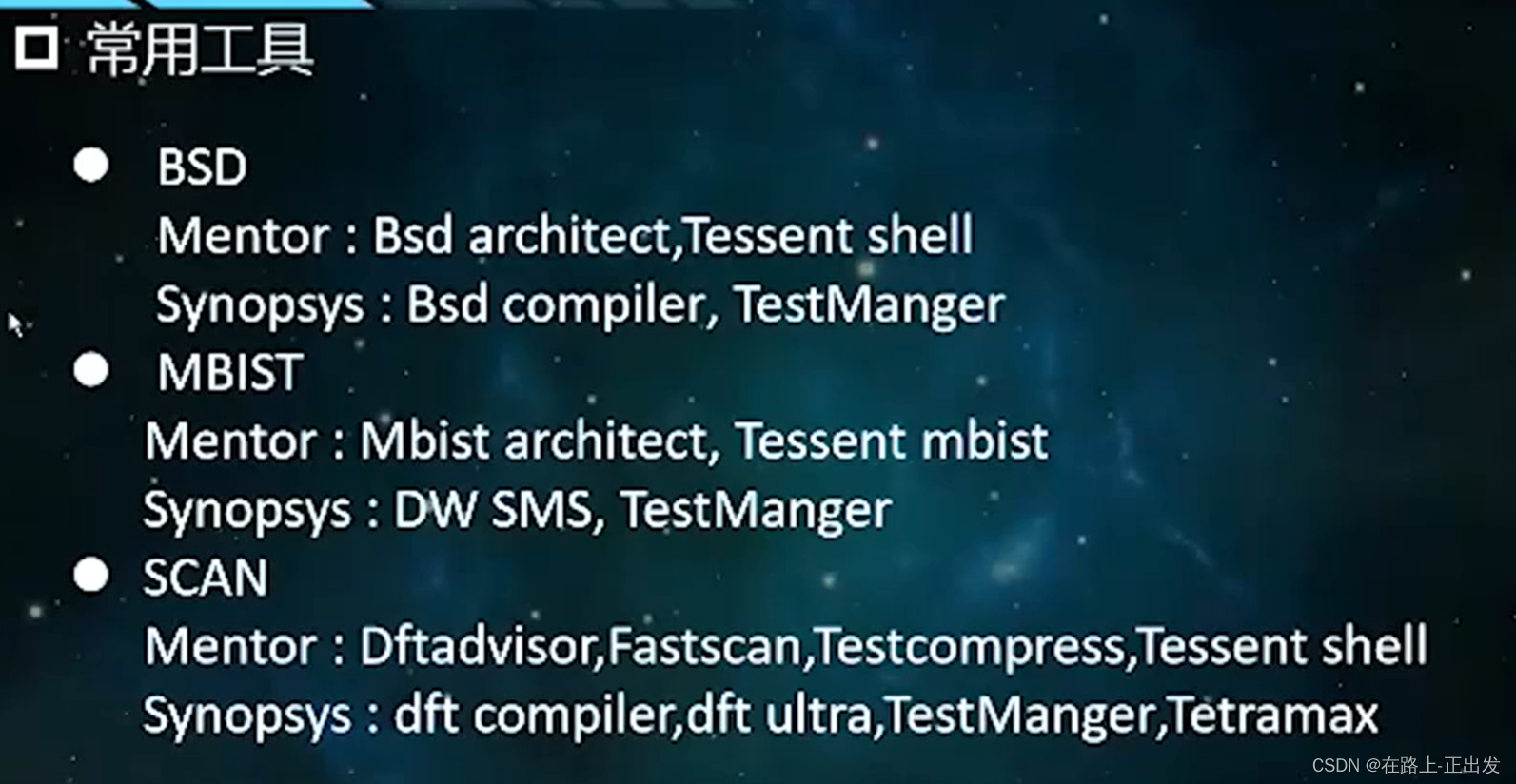

常用工具

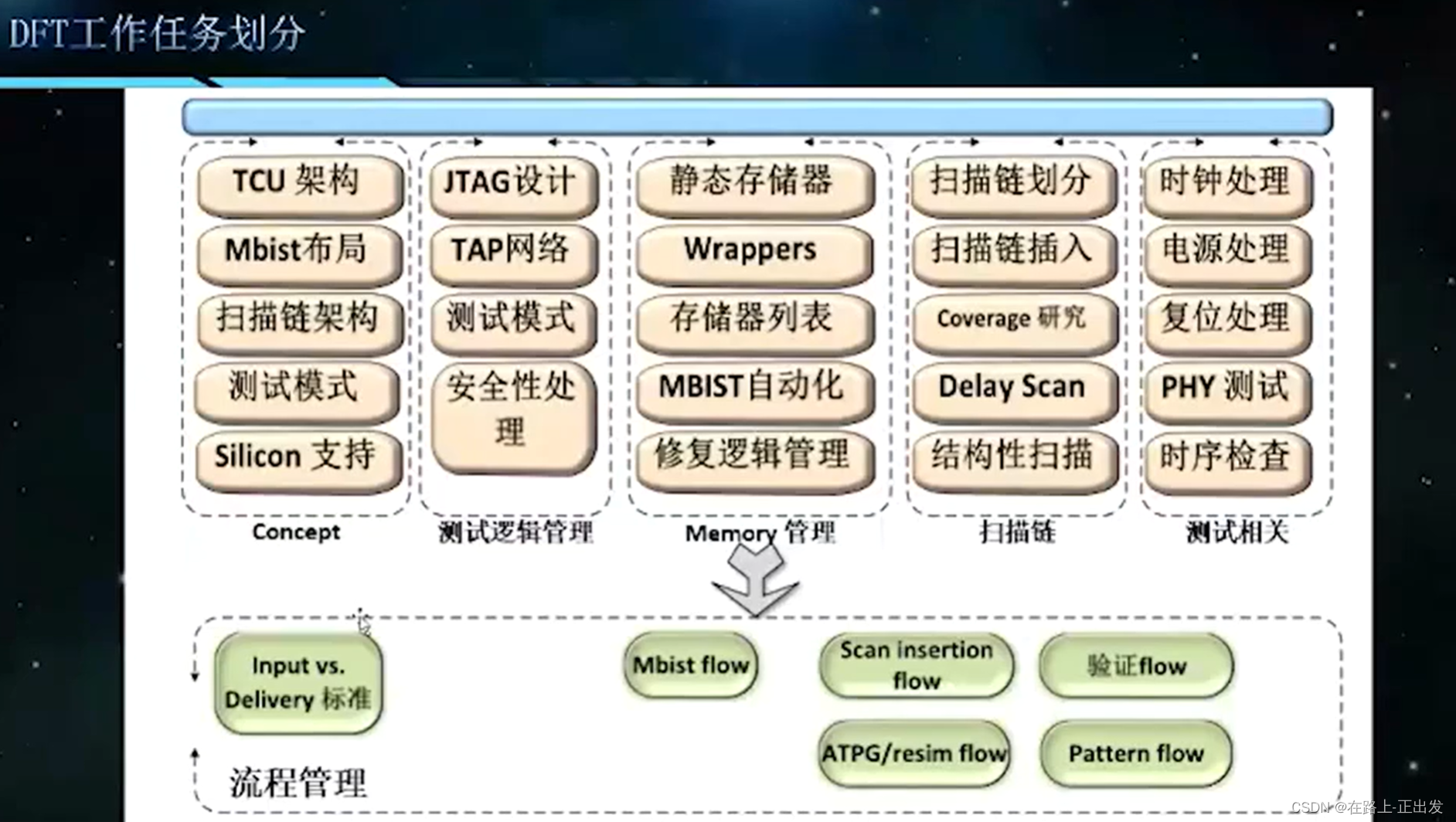

任务分配