在MMC规范发展的过程中出现了很多的名词,如SDHC、SDIO、SDXC等,每次看到这些不同的规范都有点懵,也很容易搞混,所以本篇文章就来介绍一下MMC规范发展过程中出现的一些新的规范,并详细地理解一下SD和SDIO。

1 MMC规范发展历史

1997年,MMC(Multimedia Card)即多媒体存储卡的规范发布,它是一种非易失性存储卡规范,定义了卡的形态、尺寸、容量、电气特性和通讯协议等内容。基于不同的需求的考量,如物理尺寸、容量、位宽、频率等,在MMC的规范的基础上又出现了很多不同的规范:

(1)多媒体存储方向:由MMC进化出了MMCPlus(更快)、Secure MMC(更安全)、MMCmobile和MMCmicro(更小)、MiCard(高容量)和eMMC(嵌入式)等标准。其中eMMC为BGA封装,可以直接焊接在板子上。

(2)安全和存储方向:由MMC先进化出了SD/SDSC(Secure Digital Standard Capacity),这类标准的特点就是安全。在继承了SDSC的一些优点的同时,基于存储容量、尺寸和使用范围等方面进行了优化和改进,又诞生了miniSD和microSD/TF(更小)、SDHC(高容量)、micro SDHC(更小)、SDXC(更快更大)等标准。

(3)接口方向:在SD/SDSC的基础上还诞生了另外一个分支,就是SDIO,目的是为移动电子设备提供低功耗的高速数据I/O。

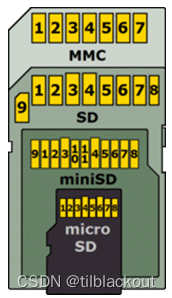

下面是不同接口规范的封装引脚和大小对比图,当SD接口要和MMC兼容时,8和9脚留空即可。

2 基本SD协议

SD卡遵循两个协议:SD协议和SPI协议。

SPI和MMC、SD的关系

SPI硬件接口非常简单,但信号是单向的,且只支持1个数据位。最初,SD和MMC总线都支持SPI模式,这样只要带有SPI外设的CPU就可以与SD卡通信。对于SD主机来说,SPI模式并不是必需的,因为任何设计用于SD总线的主机应该实现SD总线协议,而不是性能较低的SPI协议。从MMC版本4.3开始,不再强制要求支持兼容SPI接口。但是SD卡仍然需要支持兼容SPI接口。

比如对于microSD来说,就有以下两种引脚映射:

(1)SD模式

| Pin # | Pin Name | Signal Function |

|---|---|---|

| 1 | DAT2 | Data Bit 2 |

| 2 | CD/DAT3 | Card Detect/Data Bit 3 |

| 3 | CMD | Command Line |

| 4 | Vdd | Supply Voltage 2.7V/3.6V |

| 5 | CLK | Clock |

| 6 | Vss | Ground |

| 7 | DAT0 | Data Bit 0 |

| 8 | DAT1 | Data Bit 1 |

(2)SPI模式

| Pin # | Pin Name | Signal Function |

|---|---|---|

| 1 | NC | No Connect |

| 2 | /CS | Chip Select |

| 3 | DI | Master Out/Slave In(MOSI) |

| 4 | Vdd | Supply Voltage 2.7V/3.6V |

| 5 | CLK | Clock |

| 6 | Vss | Ground |

| 7 | DO | Master In/Slave Out(MISO) |

| 8 | RSV | Reserved |

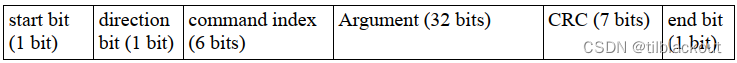

(1)SD总线通过双向CMD和DATA引脚串行地传输信息。在CMD引脚上,每个命令包含48位的命令信息,而一个命令信息包括命令索引、参数和CRC校验位。命令始终由主机发送,响应也通过CMD引脚由SD发送。大多数响应包也是48位长。主机始终是命令发起者,传输命令给SD。

(2)并非所有命令都有数据传输(DATA引脚),只有读写命令会伴随数据传输。数据包的单位称为块,主机可以定义不同的块大小,一般为512字节。数据可以使用1个或4个DATA引脚进行传输。每个数据包后面跟着16位的CRC数据。

(3)SD卡在状态机下运行,每个状态都有不同的命令集,只有在特定的状态下才能执行特定的指令。主机可以通过CMD引脚更改SD状态,比如上电后发送初始化序列改变SD状态,直到SD卡准备好传输数据。

(4)命令和数据信号通过时钟信号同步,复位后,主机使用最低的400KHz时钟速率与SD卡通信。SD卡内部寄存器可以向主机提供与SD卡容量等相关的信息。

3 SD和MMC的不同规范版本

1、SD

SD的第一个版本在2000年发布,它支持25MHz的总线频率和最大2GB的容量,数据可以在SD模式(可选择1bit或4bit)和向下兼容的SPI模式(1bit)下进行传输。

SD的第二个版本在2006年发布,它增加了SDHC(SD High Capacity)规范,即增加了存储容量最高可达32GB。这次修订版本的变化并不大,但是SDHC的诞生未未来的规范的修订奠定了基础。这次修订占据了图片和视频存储应用的市场,即使在后面的SD 3.0版本出来后,SDHC规范依旧有很大的市场。

SD3.0规范增加了一个新的容量标准SDXC,最多支持2T的存储空间,同时还根据UHS-I(Ultra High Speed)规范增加了数据的带宽。使用相同的4bit DATA接口,UHS-I支持最大单数据速率达到208MHz,可以实现104MB/s的数据传输速率;它支持的最大双数据传输速率为50MHz,即50MB/s的数据传输速率。

SD4.0规范增加了UHS-II速度版本,继续提高数据传输速率。

2、MMC

MMC规范最早由西门子和闪迪于1996年发布。该规范在2008年之前由MMC协会控制,之后由JEDEC控制规范和新版本的发布。1999年发布了2.0版本,随后于2001年发布了3.0版本。SD 1.0规范与MMC 2.11版本正式兼容。2003年的4.0版本引入了四位和八位数据宽度。八位数据宽度使MMC在相同速度下的数据带宽比SD翻倍。然而,许多主机不支持八位数据宽度,四位数据宽度仍然是与可移动存储卡通信最广泛使用的数据宽度。

JEDEC接管MMC规范后,引入了嵌入式MMC(eMMC)作为4.3版本。eMMC适用于嵌入式应用,除了机械形状之外,eMMC和MMC有相同的特性和功能。从4.4版本起,还支持引导模式,允许将设备用作BootROM(上电运行的程序)。接着还引入了DDR数据速率,以最高带宽为50MHz运行的8位DDR,传输速率达到100MB/s,与以4倍时钟速率运行的SD卡相同。

以下表格总结了不同版本的两种总线的数据速率。

| Revision | Max Clock Frequency | Data Rate |

|---|---|---|

| SD 1.0 to 1.01 | 25MHz | 12.5MB/s |

| SD 1.10 to 2.0 | 50MHz | 25MB/s |

| SD 3.0 | 208MHz | 104MB/s |

| MMC 1.0 to 3 | 20MHz | 2.5MB/s |

| MMC 4.0 to 4.3 | 50MHz | 50MB/s |

| MMC 4.4 | 50MHz | 100MB/s |

4 SD速度等级

为了向用户提供SD卡可用性能的真实度量,从SD规范2.0开始定义了几个速度等级:

| Speed Class | Decription | Revision |

|---|---|---|

| Class 0 | 这类卡没有说明其性能,包括所有SD规范2.0之前的卡 | 1.0 |

| Class 2 | 速度大于等于2MB/s | 2.0 |

| Class 4 | 速度大于等于4MB/s | 2.0 |

| Class 6 | 速度大于等于6MB/s | 2.0 |

| Class 10 | 速度大于等于10MB/s | 3.0 |

5 SD主机控制器

SD主机控制器是硬件逻辑,它构成了主机CPU和SD总线之间的桥梁。SD总线规范的主机规范部分对主机控制器设计提供了非常严格的定义。从CPU的角度来看,主机控制器包含一个256字节的寄存器集,它映射到系统的内存或IO空间。

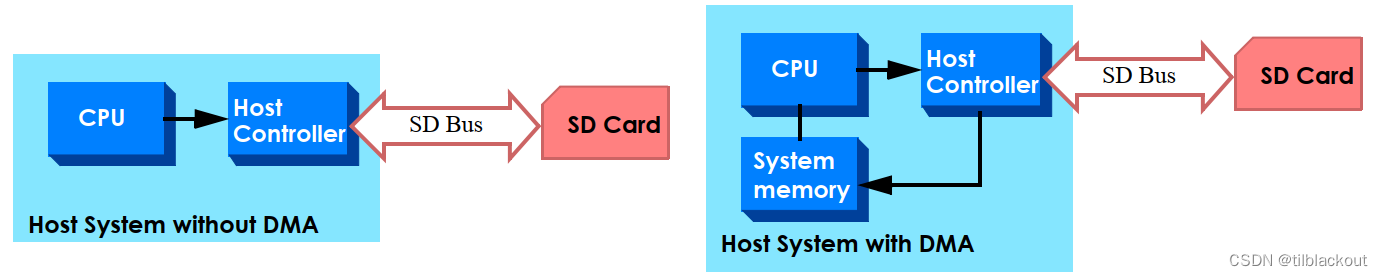

- 与SD通信时,建议打开DMA,能大大减轻CPU的运算

SD总线上的事务是由软件读取或写入该寄存器集发起的。通过此寄存器设置,用户程序可以:

- 检测SD卡的插入或拔出

- 打开/关闭SD卡电源

- 启用/禁用/控制SD时钟速度

- 定义命令参数和发送命令到SD卡

- 接收来自SD卡的命令响应

- 从SD卡读取和写入数据

- 暂停、恢复和终止数据事务

- 中断CPU的不同类型的事件,如命令完成,CRC错误等

主机系统负责为SD卡提供电源和时钟信号,SD规范中定义了卡检测机制,允许热插拔,即在插卡时产生中断,在产生该中断时,CPU再给SD卡上电。上电后,用户程序可能会使能默认的400KHz的时钟信号给SD卡,完成初始化序列,接着用户程序可以通过SD卡的寄存器获得SD卡的容量和带宽等信息,以重新配置时钟频率。

CPU可以在无操作时停止时钟信号或关闭SD卡的电源通路,以节省电源。SD卡时钟信号不能使用锁相环(PLL)。

6 SD卡内部设计

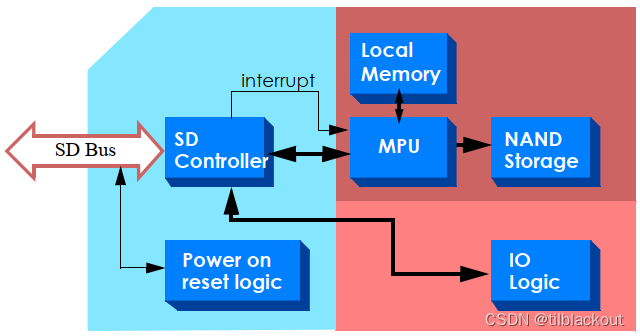

上图展示了一个典型的SD卡设计。它包括了SD存储和SDIO功能。在SD存储的实现中,实际上就是一个NAND Flash,内部一般有一个MPU来管理这些内存。典型的SDIO实现包括SD接口和IO功能逻辑模块(IO Logic),IO逻辑模块内部也可能会有MPU。

图中的SD控制器SD Controller)完成所有物理和数据链路层的功能,如命令解码、响应生成、CRC、状态管理和预定义的SD寄存器集,许多SD命令可以直接由SD控制器模块处理,而对内存空间的访问将被从SD控制器转发到卡内其他模块。

由于NAND Flash很容易有坏块,所以访问NAND的内存时一般还会经过一个用于处理坏块和其它事物的本地处理器。SD控制器不直接访问NAND闪存芯片,它可以访问“处理器”中的**影子内存(存储一些重要的数据,如设备状态)**进行数据传输,或者中断本地处理器,然后进行所需的数据传输。

当MPU接收到中断时,它会通过查询SD控制器模块来获取来自SD总线的数据请求。如果是读请求,它会从NAND中检索数据并将读取的数据传送到SD控制器模块。如果是写入请求,它会从SD控制器模块中检索数据并将其写到NAND中。

对于SDIO设备,根据正在实现的IO逻辑的特性,当从SD总线接收到用户数据传输请求时,SD控制器核心可以直接访问IO逻辑模块,或者使用中断方法来请求IO逻辑模块的服务。实际上SD规范并没有规定SD卡的内部架构,设计者可以根据应用选择最合适的架构。通常在SD存储卡中使用中断方式访问,而在SDIO中则采用直接访问方式。