关于DMA相关知识的总结,写给未来的自己,希望有帮助。立个Flag[坚持写博客总结自己工作或学习记录自己的生活]

-------------------------------------------------------------------------------------有事做,有人爱,有所期待----------------------------------------------------------------------------------------------------------------------------------------------------

DMA基础知识点

DMA 简介

直接存储器访问 (DMA) 用于在外设与存储器之间以及存储器与存储器之间提供高速数据传输。可以在无需任何 CPU 操作的情况下通过 DMA 快速移动数据。这样节省的 CPU 资源可供其它操作使用。

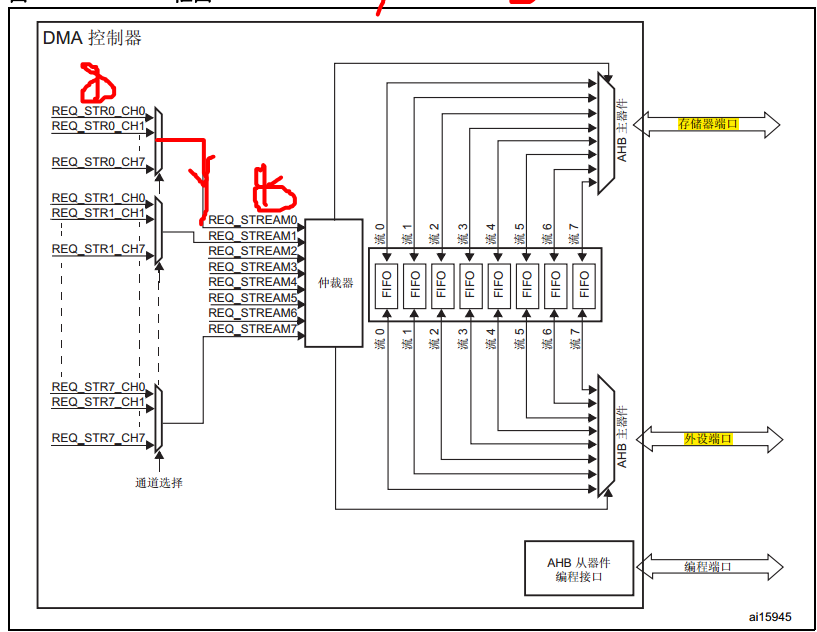

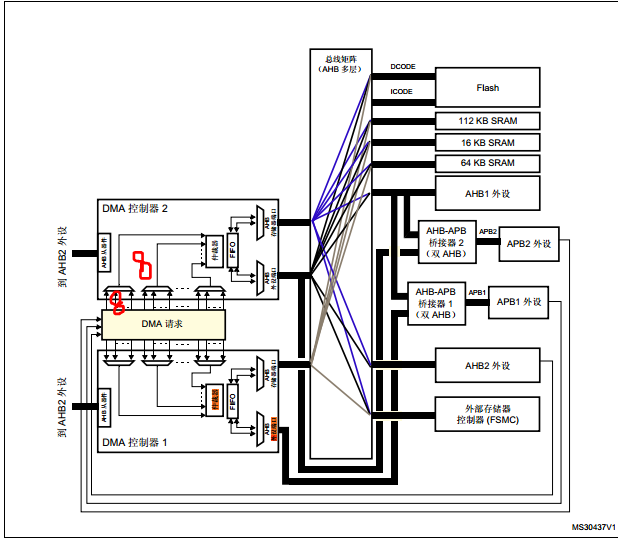

DMA 控制器基于复杂的总线矩阵架构,将功能强大的双 AHB 主总线架构与独立的 FIFO 结合在一起,优化了系统带宽。两个 DMA 控制器总共有 16 个数据流(每个控制器 8 个),每一个 DMA 控制

器都用于管理一个或多个外设的存储器访问请求。每个数据流总共可以有多达 8 个通道(或称请求)。每个通道都有一个仲裁器,用于处理 DMA 请求间的优先级。

(说白了,就是通过AHB总线将数据从源地址--->目标地址无需CPU参与高效数据传输模式,在数据传输的过程中通过寄存器配置好要传输的数据流和数据通道然后DMA控制器管理相关的寄存器进行数据传输)

DMA 框图

DMA 控制器执行直接存储器传输:因为采用 AHB 主总线,它可以控制 AHB 总线矩阵来启

动 AHB 事务。

它可以执行下列事务:

● 外设到存储器的传输

● 存储器到外设的传输

● 存储器到存储器的传输

DMA 控制器提供两个 AHB 主端口: AHB 存储器端口(用于连接存储器)和 AHB 外设端口(用于连接外设)。但是,要执行存储器到存储器的传输, AHB 外设端口必须也能访问存

储器。AHB 从端口用于对 DMA 控制器进行编程(它仅支持 32 位访问)

DMA 事务(DMA实现过程)

DMA 事务由给定数目的数据传输序列组成。要传输的数据项的数目及其宽度(8 位、 16 位或 32 位)可用软件编程。

每个 DMA 传输包含三项操作:

● 通过 DMA_SxPAR(外设) 或 DMA_SxM0AR (存储器)寄存器寻址,从外设数据寄存器或存储器单元中加载数据。

● 通过 DMA_SxPAR 或 DMA_SxM0AR 寄存器寻址,将加载的数据存储到外设数据寄存器或存储器单元。

● DMA_SxNDTR 计数器在数据存储结束后递减,该计数器中包含仍需执行的事务数。

在产生事件后,外设会向 DMA 控制器发送请求信号。 DMA 控制器根据通道优先级处理该请求。只要 DMA 控制器访问外设, DMA 控制器就会向外设发送确认信号。外设获得 DMA 控

制器的确认信号后,便会立即释放其请求。一旦外设使请求失效, DMA 控制器就会释放确认信号。如果有更多请求,外设可以启动下一个事务。 (DMA 就是将设定好目的地址和源地址

设定好的数据大小(8字节16位半字 32位字),传输的数据量,传输模式,传输的方向等基本配置后按照指定的源地址将通过AHB总线将数据传输到目的地址);

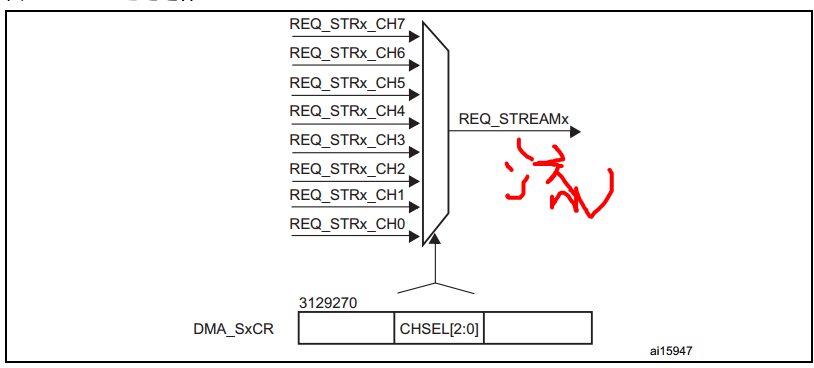

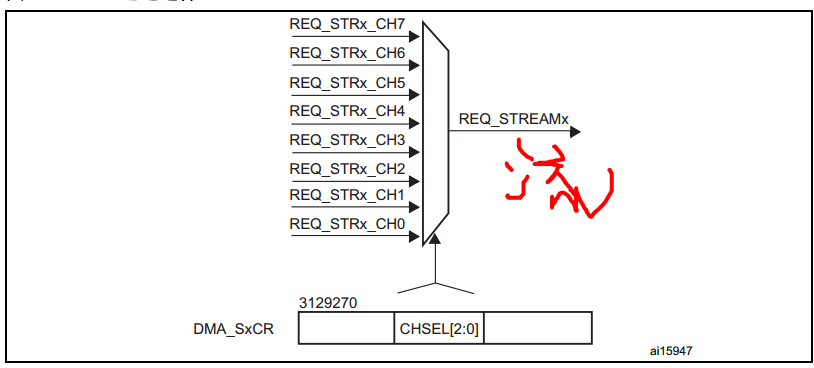

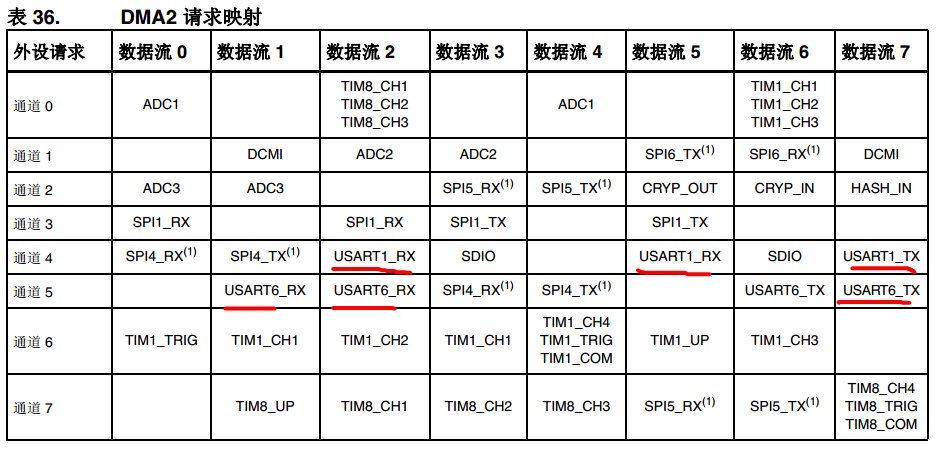

DMA数据流和数据通道 [DMA_SxCR寄存器控制 CHSEL[2:0]]

每个数据流都与一个 DMA 请求相关联,此 DMA 请求可以从 8 个可能的通道请求中选出。此选择由 DMA_SxCR 寄存器中的 CHSEL[2:0] 位控制。

来自外设的 8 个请求(TIM、 ADC、 SPI、 I2C 等)独立连接到每个通道,具体的连接取决于产品实现情况。

DMA1,控制器控制UART数据流和数据通道

DMA 仲裁器(控制每个数据流[0-7]优先级) 【相同的优先级,数据流编号低的数据流优先】

仲裁器为两个 AHB 主端口(存储器和外设端口)提供基于请求优先级的 8 个 DMA 数据流请

求管理,并启动外设/存储器访问序列。

优先级管理分为两个阶段:

● 软件:每个数据流优先级都可以在 DMA_SxCR 寄存器中配置。分为四个级别:

— 非常高优先级

— 高优先级

— 中优先级

— 低优先级

● 硬件:如果两个请求具有相同的软件优先级,则编号低的数据流优先于编号高的数据流。例如,数据流 2 的优先级高于数据流 4。

DMA 数据流

8 个 DMA 控制器数据流都能够提供源和目标之间的单向传输链路。每个数据流配置后都可以执行:

● 常规类型事务:存储器到外设、外设到存储器或存储器到存储器的传输。

● 双缓冲区类型事务:使用存储器的两个存储器指针的双缓冲区传输(当 DMA 正在进行自/

至缓冲区的读/写操作时,应用程序可以进行至/自其它缓冲区的写/读操作)。

要传输的数据量(多达 65535)可以编程,并与连接到外设 AHB 端口的外设(请求 DMA 传

输)的源宽度相关。每个事务完成后,包含要传输的数据项总量的寄存器都会递减。

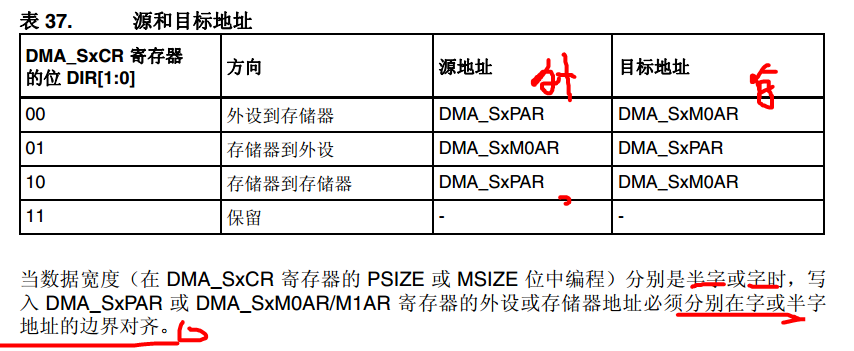

源、目标和传输模式

源传输和目标传输在整个 4 GB 区域(地址在 0x0000 0000 和 0xFFFF FFFF 之间)都可以寻址外设和存储器。

传输方向使用 DMA_SxCR 寄存器中的 DIR[1:0] 位进行配置,有三种可能的传输方向:存储器到外设、外设到存储器或存储器到存储器。 表 37 介绍了相应的源和目标地址。

DMA 模式

源地址------------->目标地址

外 设---DMA--> 存储器

存储器 ---------> 外设

存储器----------->存储器

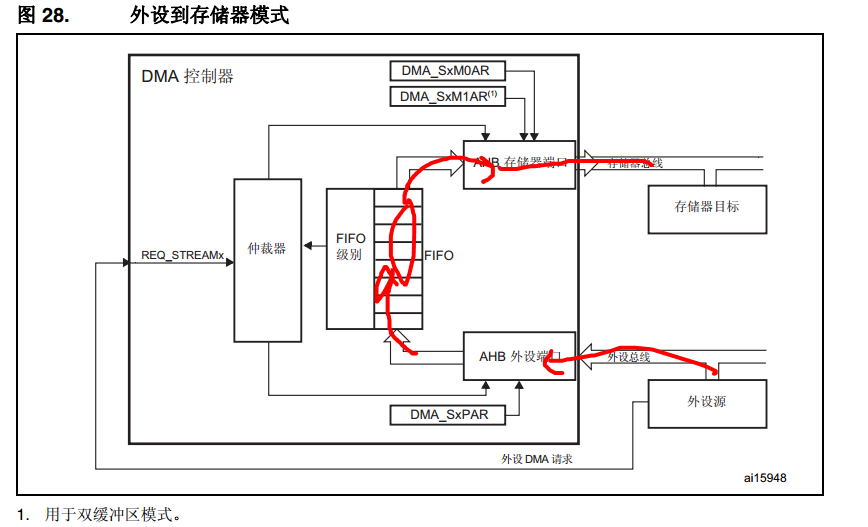

外设到存储器模式

图 28 介绍了这种模式。

使能这种模式(将 DMA_SxCR 寄存器中的位 EN 置 1) 时,每次产生外设请求,数据流都会启动数据源到 FIFO 的传输。

达到 FIFO 的阈值级别时, FIFO 的内容移出并存储到目标中。

如果 DMA_SxNDTR 寄存器达到零、外设请求传输终止(在使用外设流控制器的情况下)或DMA_SxCR 寄存器中的 EN 位由软件清零,传输即会停止。

在直接模式下(当 DMA_SxFCR 寄存器中的 DMDIS 值为“0”时),不使用 FIFO 的阈值级别控制:每完成一次从外设到 FIFO 的数据传输后,相应的数据立即就会移出并存储到目标中。

只有赢得了数据流的仲裁后,相应数据流才有权访问 AHB 源或目标端口。系统使用在

DMA_SxCR 寄存器 PL[1:0] 位中为每个数据流定义的优先级执行仲裁。

存储器到外设模式

图 29 介绍了这种模式。

使能这种模式(将 DMA_SxCR 寄存器中的 EN 位置 1)时,数据流会立即启动传输,从源完

全填充 FIFO。

每次发生外设请求, FIFO 的内容都会移出并存储到目标中。当 FIFO 的级别小于或等于预定

义的阈值级别时,将使用存储器中的数据完全重载 FIFO。

如果 DMA_SxNDTR 寄存器达到零、外设请求传输终止(在使用外设流控制器的情况下)或

DMA_SxCR 寄存器中的 EN 位由软件清零,传输即会停止。

在直接模式下(当 DMA_SxFCR 寄存器中的 DMDIS 值为“0”时),不使用 FIFO 的阈值级

别。一旦使能了数据流, DMA 便会预装载第一个数据,将其传输到内部 FIFO。一旦外设请

求数据传输, DMA 便会将预装载的值传输到配置的目标。然后,它会使用要传输的下一个数

据再次重载内部空 FIFO。预装载的数据大小为 DMA_SxCR 寄存器中 PSIZE 位字段的值。

只有赢得了数据流的仲裁后,相应数据流才有权访问 AHB 源或目标端口。系统使用在

DMA_SxCR 寄存器 PL[1:0] 位中为每个数据流定义的优先级执行仲裁。

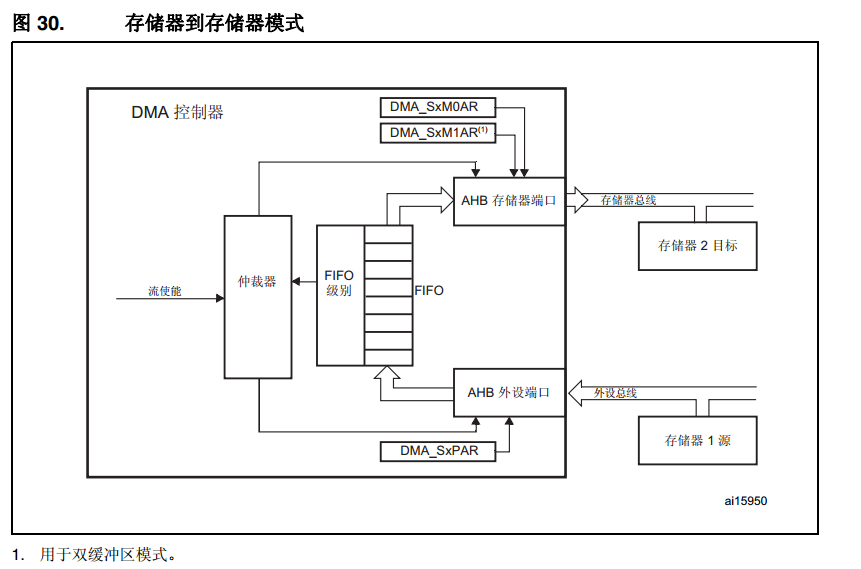

存储器到存储器模式

DMA 通道在没有外设请求触发的情况下同样可以工作。此为图 30 中介绍的存储器到存储器

模式。

通过将 DMA_SxCR 寄存器中的使能位 (EN) 置 1 来使能数据流时,数据流会立即开始填充

FIFO,直至达到阈值级别。达到阈值级别后, FIFO 的内容便会移出,并存储到目标中。

如果 DMA_SxNDTR 寄存器达到零或 DMA_SxCR 寄存器中的 EN 位由软件清零,传输即会

停止。

只有赢得了数据流的仲裁后,相应数据流才有权访问 AHB 源或目标端口。系统使用在

DMA_SxCR 寄存器 PL[1:0] 位中为每个数据流定义的优先级执行仲裁。

注意: 使用存储器到存储器模式时,不允许循环模式和直接模式。

只有 DMA2 控制器能够执行存储器到存储器的传输