1. 硬件接口

显示屏分辨率是1920×RGB×1080 pixels。

1.1 硬件连接示意图

1.2 硬件连接引脚

CPU |

SN65DSI84 DSI转LVDS |

LM3492HCMH 背光控制IC |

显示屏 |

GPIO126_LCD_1V8_EN |

VCC |

||

GPIO129_LCD_5V_EN |

5V_BL |

||

GPIO125_LCD_COMM |

COMM |

||

MPP2_LCD_BL_PWM |

DIM1/CLK |

||

GPIO123_LCD_DIM2 |

DIM2 |

||

GPIO7_LCD_I2C2_SCL |

SCL |

||

GPIO6_LCD_I2C2_SDA |

SDA |

||

GPIO124_LVDS_INT |

IRQ |

||

GPIO130_LVDS_EN |

EN |

||

2. SD65DSI84

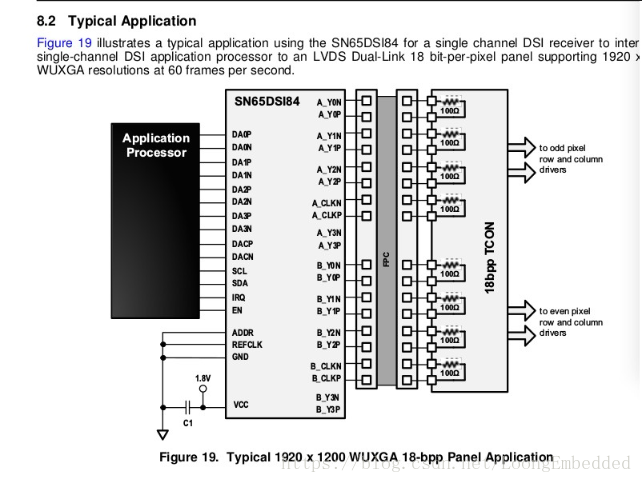

The SN65DSI8x can be used between a GPU with DSI output and a video panel with LVDS inputs,MIPI DSI-to-LVDS

SN65DSI84 非常适合于每秒 60 帧的 WUXGA 1920 x 1200 应用,每像素比特位高达 24。 执行了部分线路缓冲以适应 DSI 与 LVDS 接口间的数据流不匹配。

2.1 SN65DSI84的主要特征

(1) 单DSI接收通道,可配置为使用1~4个D-PHY数据信道,每个数据信道最高可工作在1Gbps。

(2) 支持18bpp(RGB666)和24bpp(RGB888)数据格式的DSI视频包。

(3) 支持低压差分信令(LVDS)单通道DSI 至双链路LVDS 桥 (Rev. E)

(4) LVDS输出时钟范围为25MHz~154MHz。

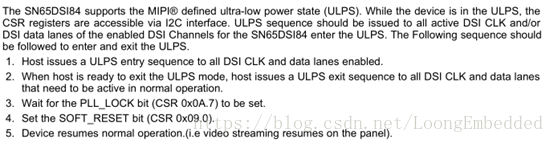

(5) 低功耗特性包括关断 (SHUTDOWM) 模式、精简 LVDS 输出电压摆幅、共模和 MIPI® 超低功耗状态 (ULPS,ultra-low power state,超低功耗) 支持

2.2 复位芯片

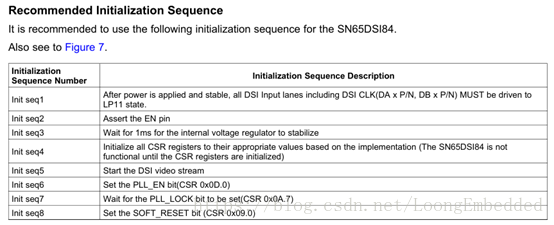

2.3 SN65DSI84推荐的初始化时序

2.4 时钟配置和倍频器

(2) 采用外部参考时钟源

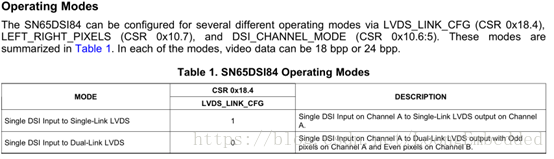

2.5 SN65DSI84的工作模式

工作模式由DSI和LVDS通道的使用数量与CSR寄存器配置的DSI数据输入选项来决定。

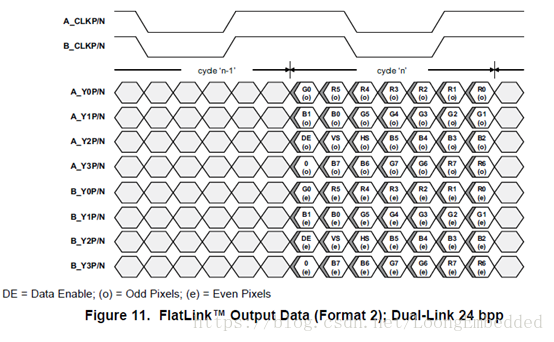

2.6 LVDS输出格式

当使用双通道配置,通道A传输奇数像素数据,通道B传输偶数像素数据when

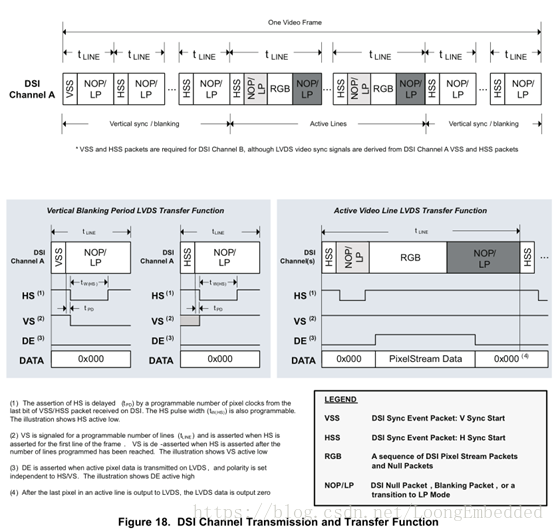

SN65DSI84处理DSI包和以工业标准格式来产生视频数据驱动LVDS接口,上图这是我们产品使用的视频数据格式。

2.7 DSI lane数据合并

我们采用4路DSI数据通道。

2.8 DSI 像素流包

2.9 DSI视频传输规范

2.10 ULPS

LVDS的输出时序由CSR寄存器对应的视频参数来产生。HSync pulse width, HSync Back Porch duration,and VSync pulse width.这些值需要变成用来创建LVDS显示屏的时序。

2.11 LVDS模式生成

此特征可用来测试LVDS输出路径和LVDS面板。

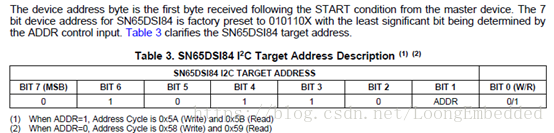

2.12 SN65DSI84的I2C地址

我们硬件设置是ADDR引脚通过下拉电阻接地,也就是ADDR=0,所以I2C写地址为0x58,读地址为0x59,但在代码里I2C从设备地址为0x2C,采用前7位作为I2C从设备的地址。