基于高通Msm8937平台,SN65DSI84后面简称DSI84。

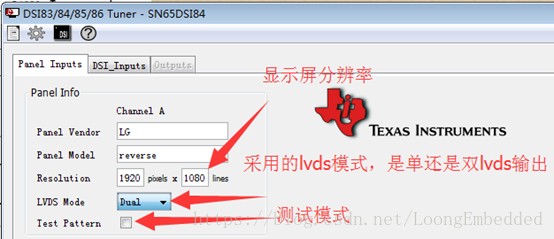

打开DSI Tuner,选择目标设备,这里我们是SN65DSI84

- Panel Inputs

1.1 Panel Info

这些数据的填写主要来至于显示屏规格书:

这里的LVDS Mode一定要根据我们硬件设计来写,我们这里是dual,也就是双路LVDS输出模式。

1.2 Pixels和Line

显示屏相关参数

(1) LVDS_HActive和LVDS_VActive的值根据上面的Resolution和LVDS Mode的值自行确定

(2) 我们分别取Hsync和Vsync典型值,LVDS_HPW+LVDS_HBP+LVDS_HFP=tHP-tHV=1088-960=128,LVDS_VPW+LVDS_VBP+LVDS+VFP=tVP-tVV=1100-1080=20

1.3 Additional Panel Info

这里说明下DE、HS和VS的极性选择,这需要匹配显示屏panel规格书,比如我们的屏

2.DSI_Inputs

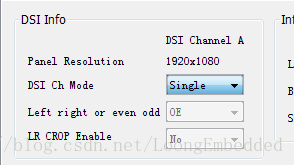

2.1 DSI Info

SN65DSI84只有单通道,所以只有Single选择。

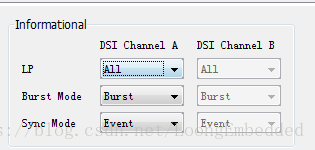

2.2 Informational

选择默认的

2.3 Pixels和Lines

根据前面得到的值填写,保持一致

2.4 Additional Channel info

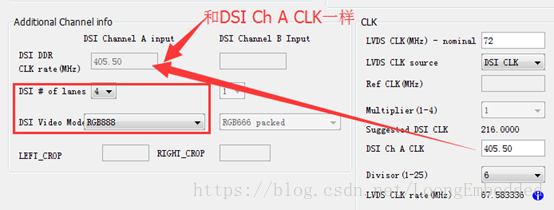

根据我们的涉及填写DSI采用了几个lane,DSI视频模式采用的18bpp还是24bpp。

2.5 CLK

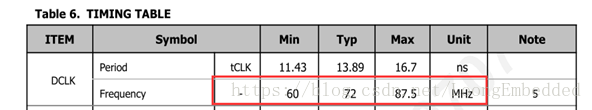

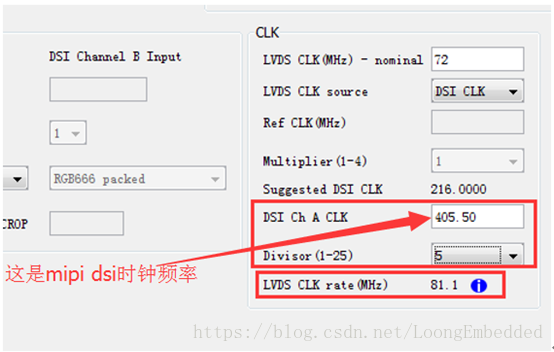

(1) LVDS CLK(MHz)-nominal,显示屏的像素时钟的标称值

比如这里我们选择72

(2) Suggested DSI CLK

建议最小的DSI CLK值,由(LVDS CLK(MHz)-nominal)*( (bytes/pixel))=72*3=216

(3) DSI CH A CLK

这也就是DSI CLK,对应dsiclk,这也是我们用用示波器测量MIPI CLK的频率,这里为405.50MHz

Dsiclk是根据高通80-NH713-1_G_DSI_Timing_Parameters.xlsm输入panel的参数后计算得到的。

这里bitclk、byteclk、dsiclk和pclk的意义见https://blog.csdn.net/LoongEmbedded/article/details/82979864

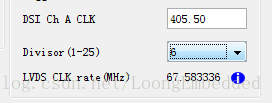

(4) LVDS CLK rate(MHz):SN65DSI84输出的lvds时钟

LVDS CLK rate(MHz) = (DSI Ch A CLK)/divisor,此图得到的初始化参数可以正常点亮显示屏,

这里特别说明下,生成的0x28寄存器的值是0Xc1,如果过小,比如0x20就黑屏,如果是0x48就显示一半左右,试过0xa8开始就能正常全部显示。

如果改为下面的就不行