使用MATLAB生成滤波器有很多学问,这里只是作为初步的探索,和FPGA的更多结合,也正在探索中,相关博文例如:【 FPGA 】FIR滤波器目录,该专题目录正在记录我学习FIR滤波器的过程。

MATLAB生成30阶低通1MHz海明窗函数设计步骤:

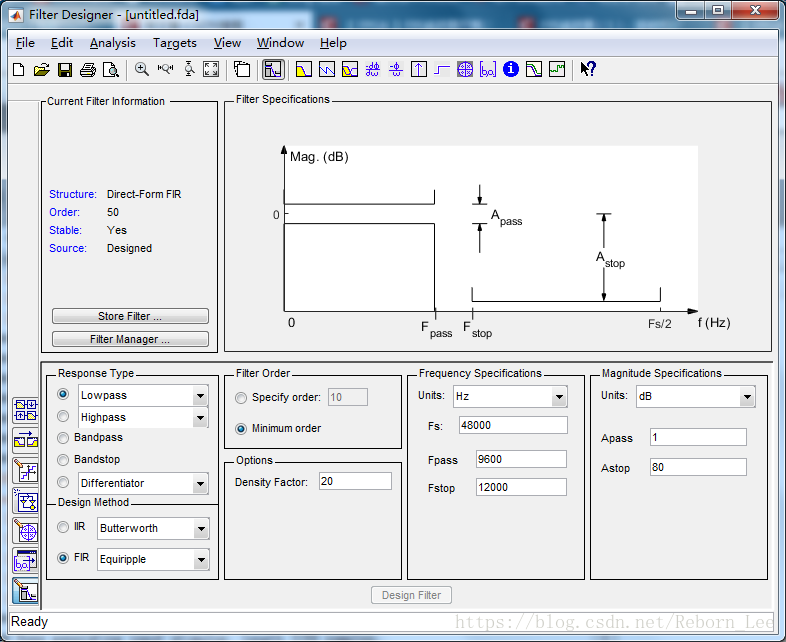

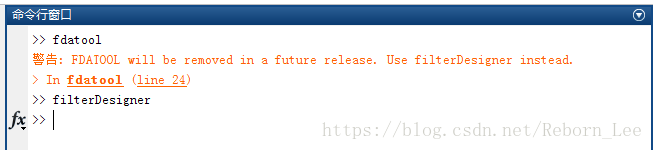

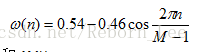

(1)在MATLAB命令窗口中输入“fdatool”出现如下对话框:

注意,在MATLAB2018以后的版本中输入:filterDesigner,即可打开上述界面。

(2)设定为低通滤波器。

(3)选择FIR滤波器的设计类型为窗函数。

设置FIR滤波器为30阶滤波器,选择窗函数的类型为海明窗函数,海明窗函数可以得到旁瓣更小的效果,能量更加集中在主瓣中,主瓣的能量约占99.963%,第一旁瓣的峰值比主瓣小40dB,但主瓣宽度与海明窗相同。它定义为:

(4)输入抽样频率和截止频率,分别是16MHz和1MHz。

(5)点击Design Filter 得到结果,如下图:

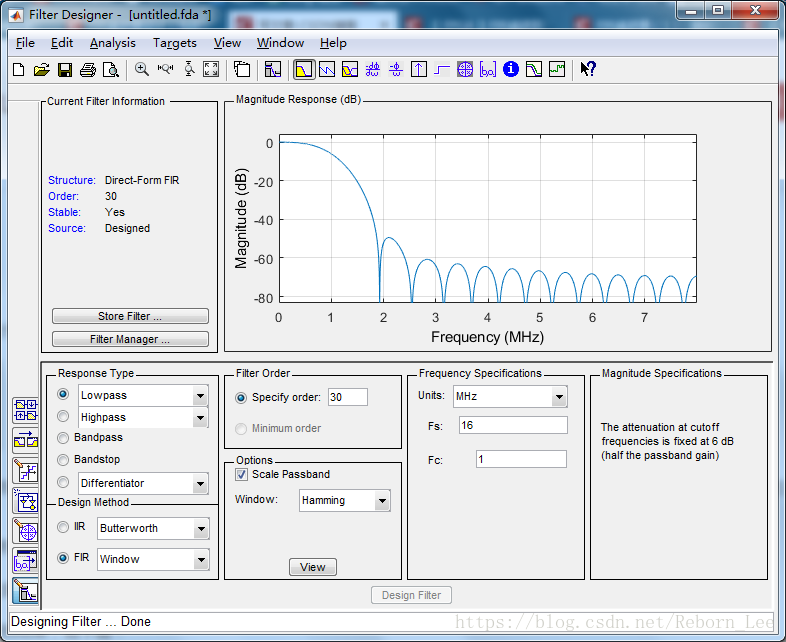

(6)量化输入输出,点击工作栏左边的量化选项,即“set quantization parameters”选项,选择定点,设置输入字长为8,其他选择默认,如下图示:

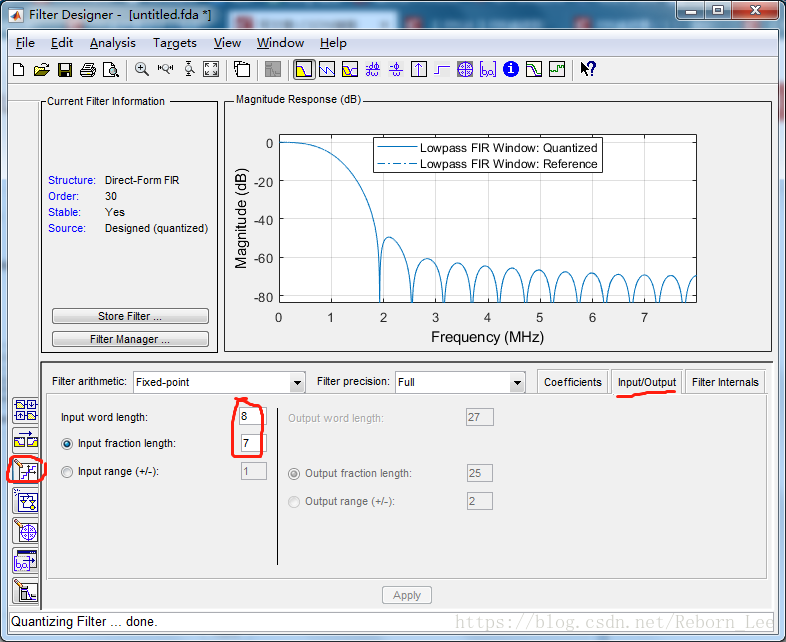

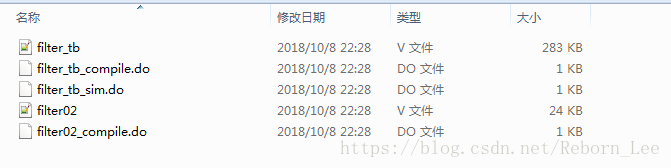

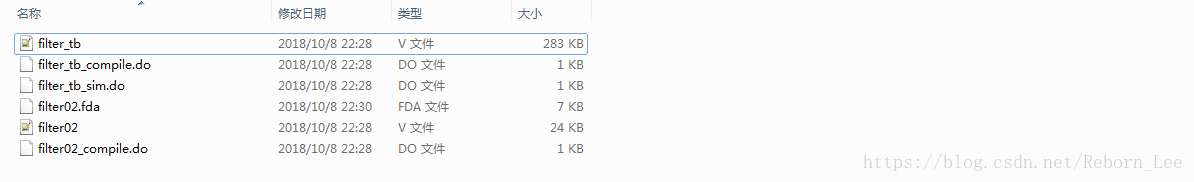

设置完成后,点击Targets中Generate HDL,选择生成Verilog 代码,设置路径,MATLAB即可生成设计好的滤波器Verilog HDL 代码以及测试文件:

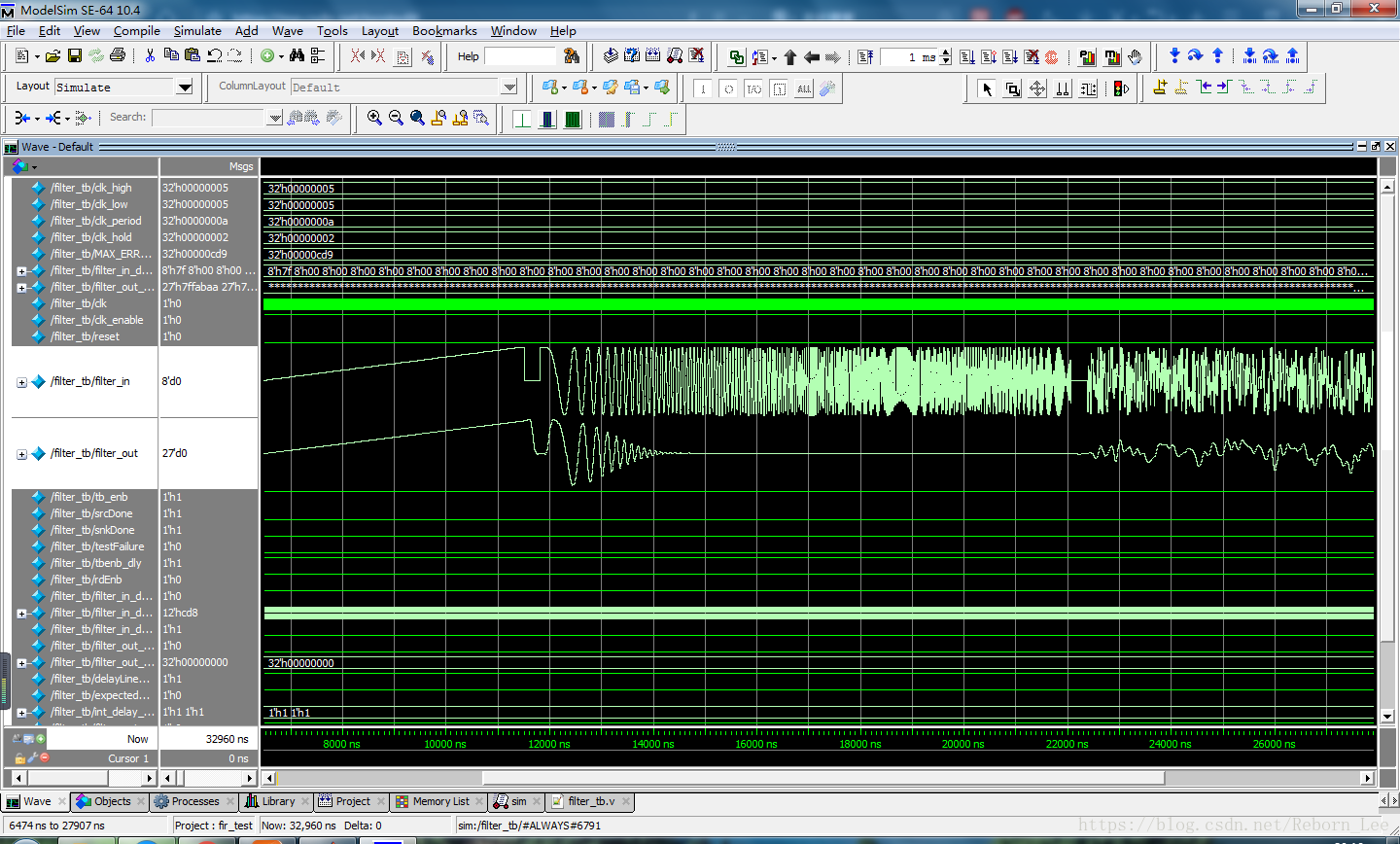

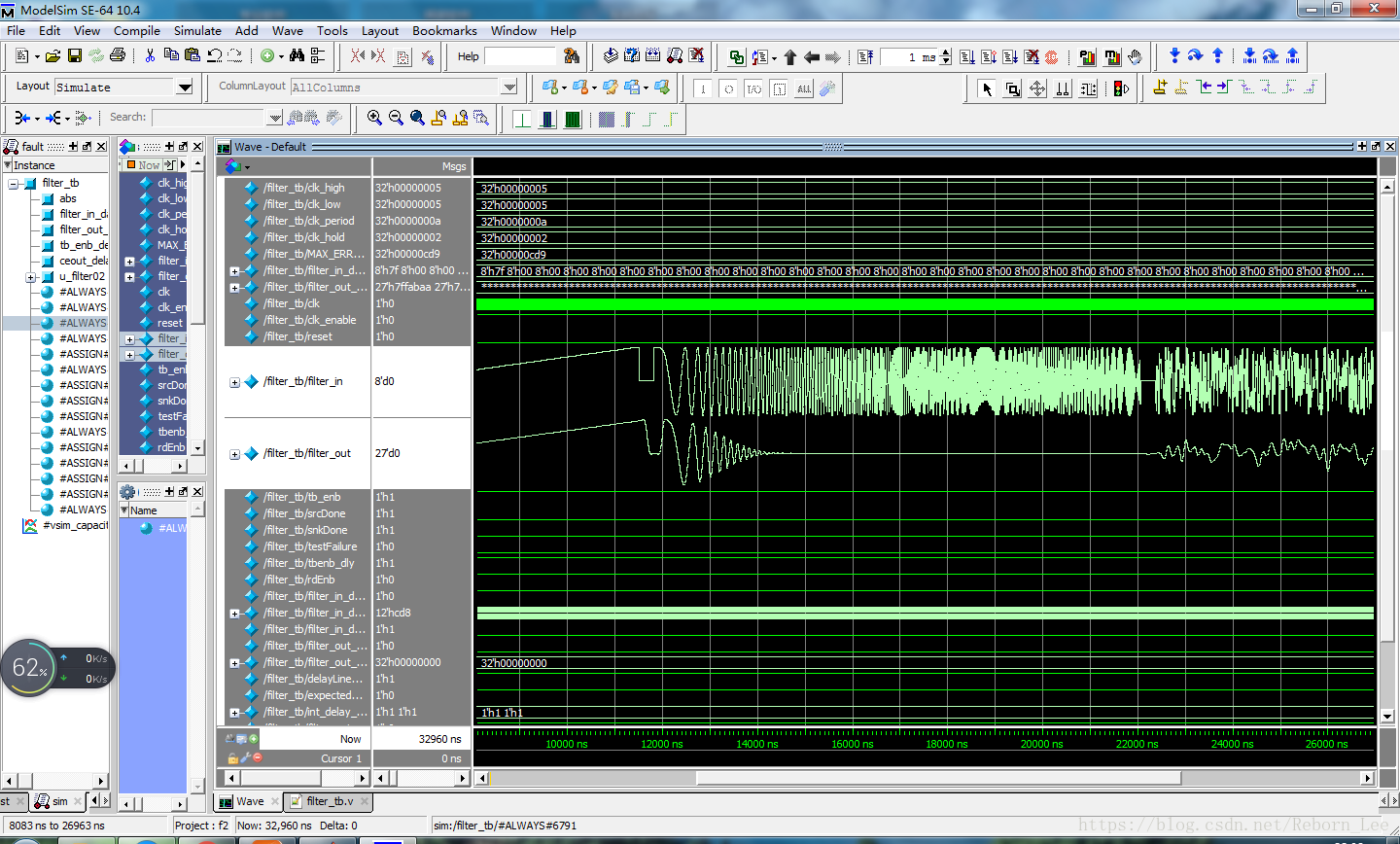

仿真结果如下图:

如上图所示,当输入为线性,或者输入频率较低时,输出幅度不会被抑制,当输入频率较高,输出幅度会受到大幅度抑制,而当输入为白噪声或者混频信号时,滤波器会过滤掉高频信号。

当然,如果仅仅直接给出上述仿真结果,略显没有诚意,因为一般教科书上的风格就是这样的,不告诉你怎么仿真成这个样子,(例如这里的模拟波形是如何产生的等),那这里不是教科书,这里是更随意、更接地气的分享知识以及经验的地方,我就给出仿真的过程。

预备1:

首先,你的电脑上必须要有Modelsim这个仿真软件:

我曾经写过modelsim安装以及破解的博文,可以参考!

modelsim-win64-10.4-se 破解(win7实验成功)(其他操作系统也可参考,大同小异)

预备2:通过上述的方法生成Verilog HDL代码以及testbench文件:

正式开始:

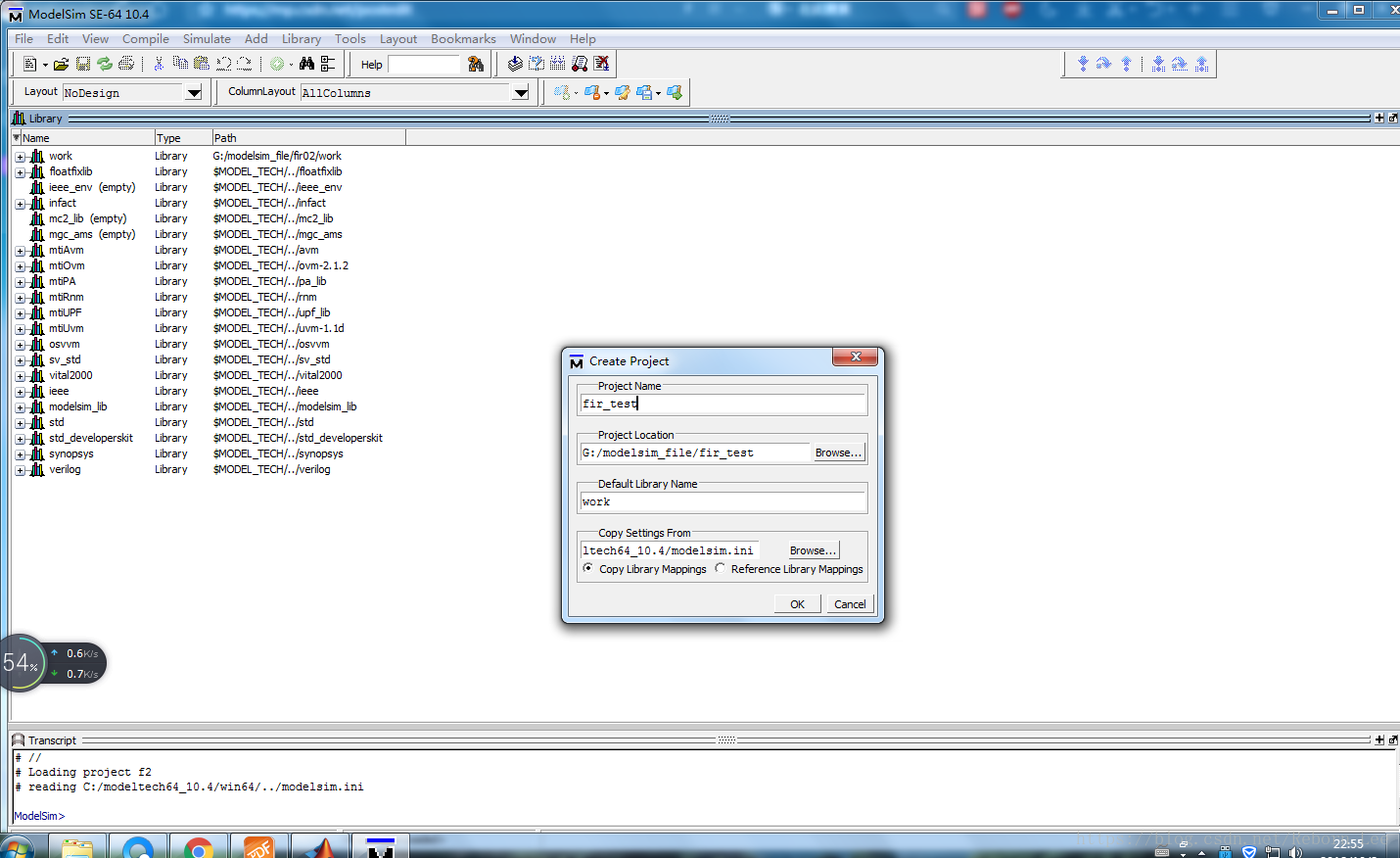

打开Modelsim,新建一个工程文件:

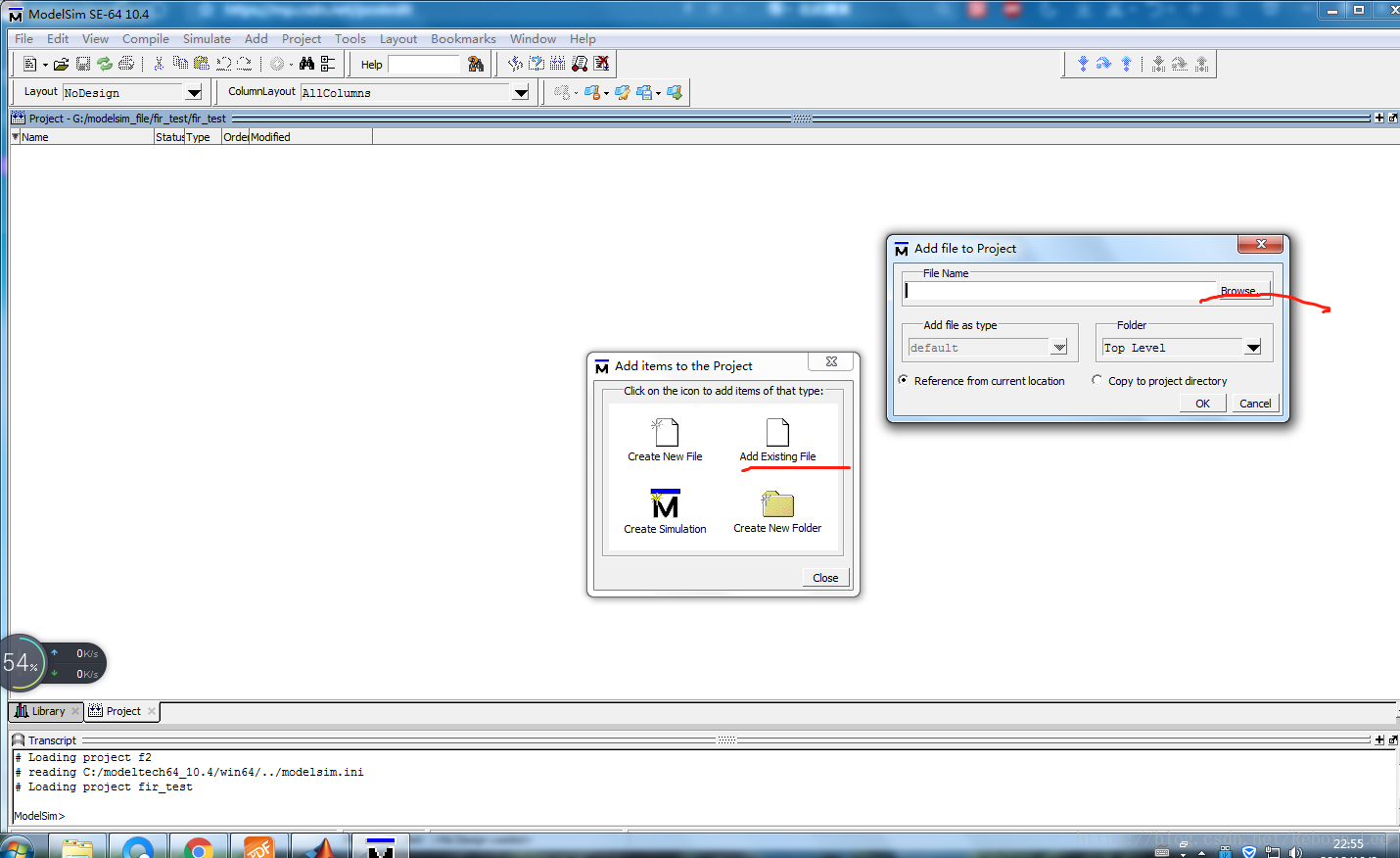

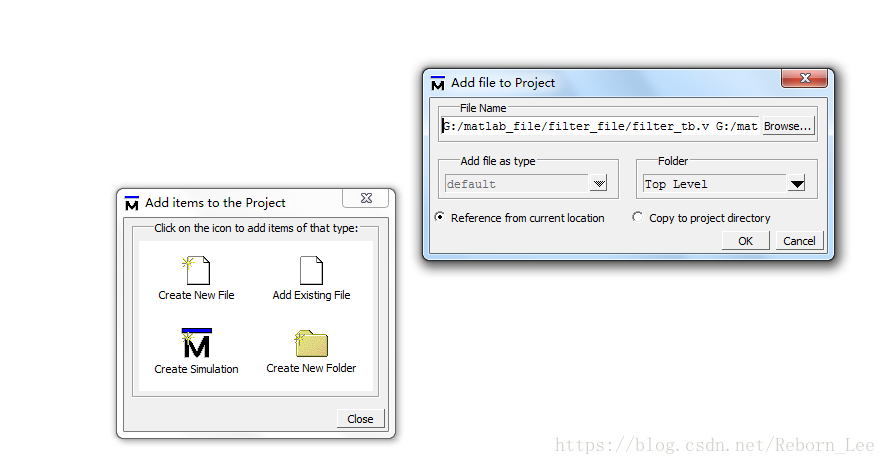

添加Verilog HDL文件以及测试文件:

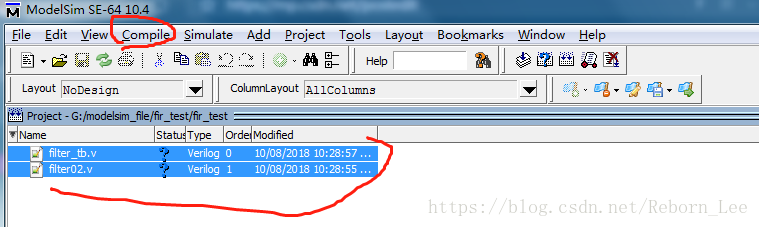

如下图,选中并编译:

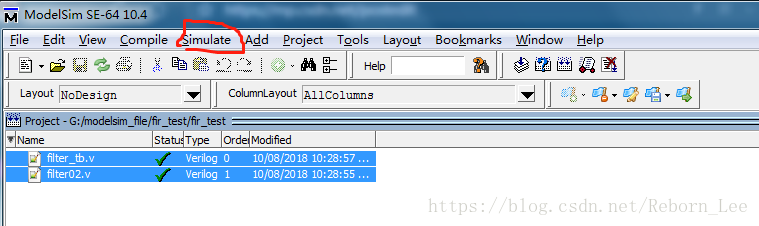

之后开始仿真:

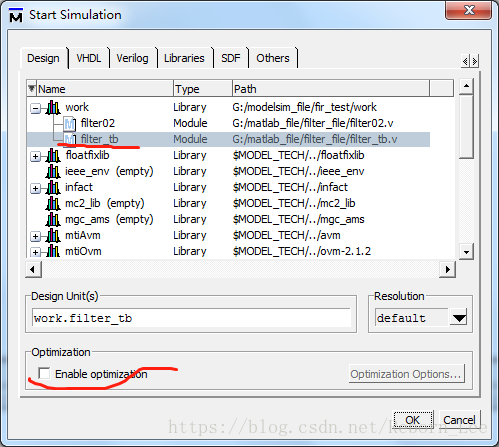

选中tb文件,并取消优化选项:

之后,如下图:选中目标并右击添加到wave;

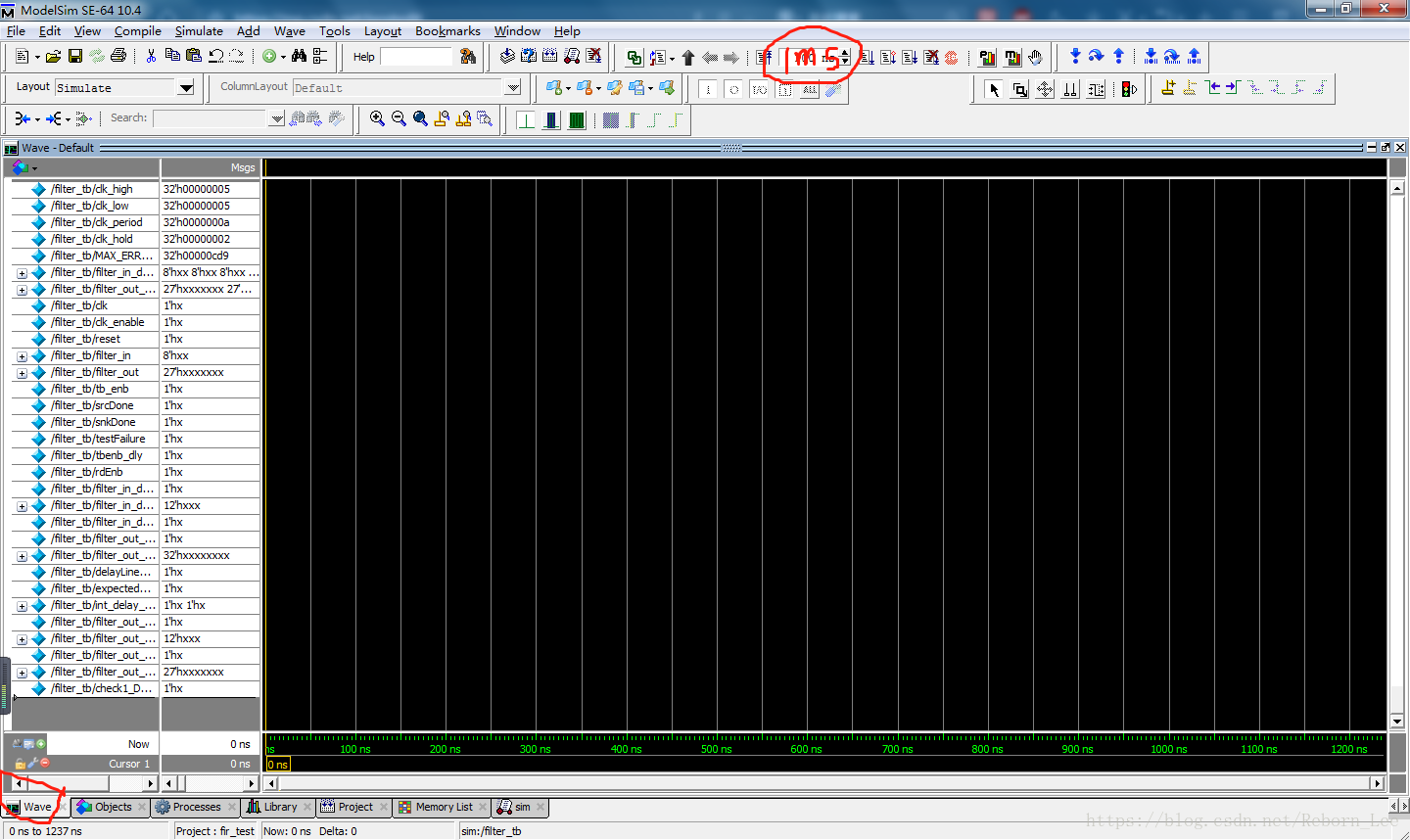

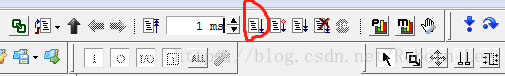

如下图:仿真时间改为1ms

运行:

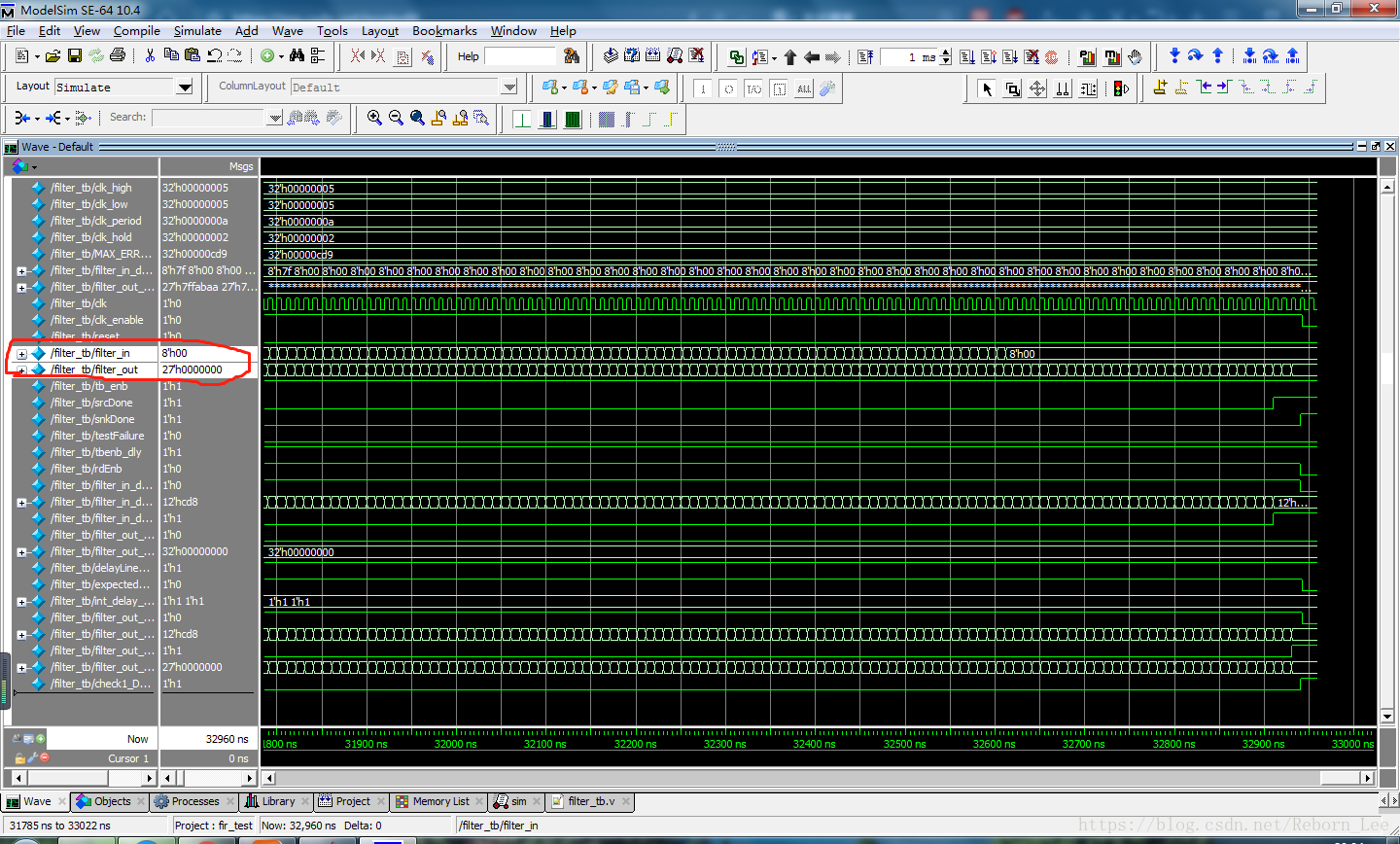

选中下面的两项:

右击,format,analog(automatic);

右击,radix,decimal;

这两个步骤完成之后,就出现如下图的效果:

从中,最直观的感受就是我们设计的这个滤波器对低频分量给予通过,对高频分量则出现抑制现象,和我们的预期一样,因为我们设计的就是低通滤波器。

更多内容的你可以仔细去阅读tb文件,看看人家输入的信号是什么样的。

好了,这篇博文就到这里了。

路漫漫其修远兮,吾将上下而求索!

参考博文:https://www.cnblogs.com/xiaomeige/p/8846786.html

参考文献:Verilog HDL数字集成电路高级电路设计