目录

1.算法描述

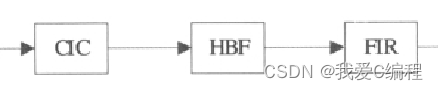

数字下变频中的低通滤波器是由多级抽取滤波器组实现的。信号的同相分量和正交分量再分别经由积分梳状滤波器(CIC)、半带滤波器(HB)和有限长单位脉冲响应(FIR)滤波器构成的多级抽取滤波器组进行滤波和降采样处理,再将产生的正交基带信号I (n)、Q (n)送到通用DSP处理器,进行信号识别、解调等基带信号处理。这三个滤波器在结构上组成如下的基本结构:

下面分别对滤波器的三组不同的滤波器进行设计与分析,并得出其优化结果。

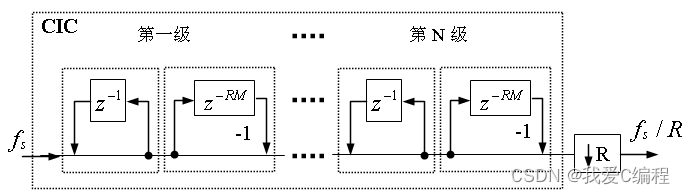

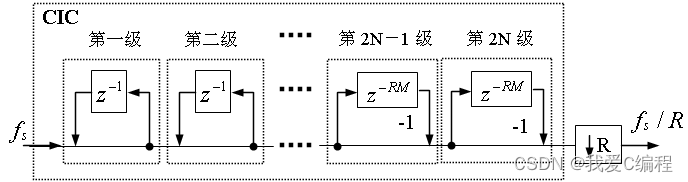

2.1CIC抽取滤波器结构图

图CIC梳状滤波器的结构一

图CIC梳状滤波器的结构二

2.2HBF模块由半带滤波器

HBF模块由半带滤波器(HBF)和抽取模块组成。该模块的任务是实现2倍抽取进一步降低信号采样速率。由于HBF的冲激响应h(k)除零点外其余偶数点均为零,所以用HBF实现2倍抽取可以节省一半的运算量,对增强软件无线电的实时性非常重要,HBF还具有参数约束少,设计容易、方便的特点。半带滤波器的主要作用是滤除信号高频部分,防止抽取过程后信号发生频谱混叠。

在实际中,需要将输入信号进行多次滤波和抽取,并逐次降低采样率,同时也降低对每一级抗混叠滤波器的要求,所以需要使用半带滤波器进行设计与实现。

阻带衰减: ≥50dB

通带不平坦度:≤2dB

通常情况下,半带滤波器的有三种基本的结构,一般结构,转置结构以及复用结构,下面我们将针对这三种结构的滤波效果以及硬件占用情况进行分析,从而选用最佳的设计方案。

2.3 DA分布式FIR

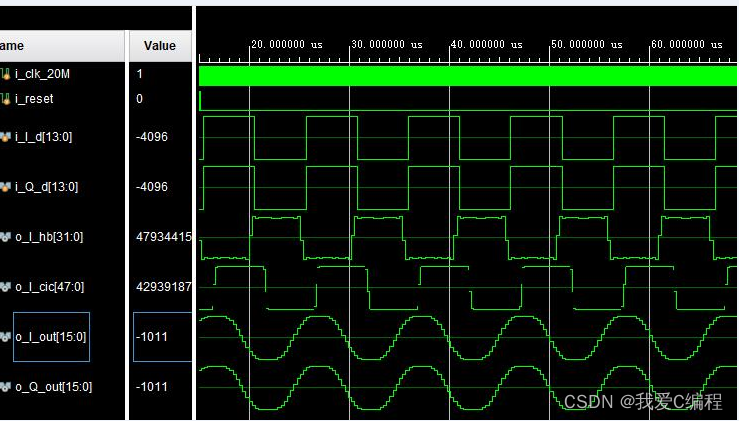

2.仿真效果预览

版本vivado2019.2

3.verilog核心程序

module tops2(

clk_20M,

reset,

I_d,

Q_d,

I_cic,

I_hb,

I_out,

Q_out

);

input wire clk_20M;

input wire reset;

input wire [13:0] I_d;

input wire [13:0] Q_d;

output wire [47:0] I_cic;

output wire [31:0] I_hb;

output wire [15:0] I_out;

output wire [15:0] Q_out;

wire [47:0] I_cic_ALTERA_SYNTHESIZED;

wire [31:0] I_hb_ALTERA_SYNTHESIZED;

wire [47:0] Q_cic;

wire [31:0] Q_hb;

wire SYNTHESIZED_WIRE_0;

wire SYNTHESIZED_WIRE_1;

wire SYNTHESIZED_WIRE_2;

wire SYNTHESIZED_WIRE_3;

cic_top b2v_inst(

.i_clk(clk_20M),

.i_rst(reset),

.i_din(I_d),

.o_clk16(SYNTHESIZED_WIRE_0),

.o_dout(I_cic_ALTERA_SYNTHESIZED));

defparam b2v_inst.WIDTH = 48;

cic_top b2v_inst1(

.i_clk(clk_20M),

.i_rst(reset),

.i_din(Q_d),

.o_clk16(SYNTHESIZED_WIRE_1),

.o_dout(Q_cic));

defparam b2v_inst1.WIDTH = 48;

hb_filter_02 b2v_inst2(

.i_clk(SYNTHESIZED_WIRE_0),

.i_rst(reset),

.i_din(I_cic_ALTERA_SYNTHESIZED[34:19]),

.o_clk2(SYNTHESIZED_WIRE_2),

.o_dout(I_hb_ALTERA_SYNTHESIZED));

defparam b2v_inst2.h0 = 27316;

defparam b2v_inst2.h1 = 20073;

defparam b2v_inst2.h11 = 1238;

defparam b2v_inst2.h13 = -1175;

defparam b2v_inst2.h15 = -624;

defparam b2v_inst2.h3 = -4745;

defparam b2v_inst2.h5 = 965;

defparam b2v_inst2.h7 = 667;

defparam b2v_inst2.h9 = -1238;

hb_filter_02 b2v_inst3(

.i_clk(SYNTHESIZED_WIRE_1),

.i_rst(reset),

.i_din(Q_cic[34:19]),

.o_clk2(SYNTHESIZED_WIRE_3),

.o_dout(Q_hb));

defparam b2v_inst3.h0 = 27316;

defparam b2v_inst3.h1 = 20073;

defparam b2v_inst3.h11 = 1238;

defparam b2v_inst3.h13 = -1175;

defparam b2v_inst3.h15 = -624;

defparam b2v_inst3.h3 = -4745;

defparam b2v_inst3.h5 = 965;

defparam b2v_inst3.h7 = 667;

defparam b2v_inst3.h9 = -1238;

firfilter_da b2v_inst4(

.CLK(SYNTHESIZED_WIRE_2),

.Reset(reset),

.DIN(I_hb_ALTERA_SYNTHESIZED[30:23]),

.Dout(I_out));

firfilter_da b2v_inst5(

.CLK(SYNTHESIZED_WIRE_3),

.Reset(reset),

.DIN(Q_hb[30:23]),

.Dout(Q_out));

assign I_cic = I_cic_ALTERA_SYNTHESIZED;

assign I_hb = I_hb_ALTERA_SYNTHESIZED;

endmodule

01_115m4.完整FPGA

V