概述

PS2鼠标和键盘实现了一个双向同步串行协议。当SCL和SDA两根信号线都为高(OC),表示总线为空闲状态。只有总线在空闲状态时,键盘和鼠标才允许进行数据传输。主机对总线有最终的控制权,可以在任何时候通过拉低时钟线强迫总线禁止通信。

设备会一直产生时钟信号。如果主机想要发送数据,它必须首先通过拉低时钟信号禁止通信。然后,主机拉低数据线,然后释放时钟信号。这就是所谓的“请求-发送”状态,然后发送信号给设备,开始产生时钟脉冲。

| Data | 时钟 | 状态 |

|---|---|---|

| 高 | 高 | 空闲状态 |

| 高 | 低 | 禁止通讯 |

| 低 | 高 | 主机请求-发送 |

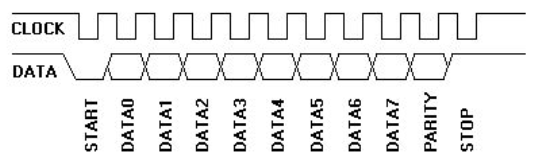

数据传输时,每次传输一个字节,每次发送的数据为一帧,每帧数据由11-12位组成。帧结构如下:

| 位序 | 名称 | 描述 |

|---|---|---|

| 0 | 起始位 | 起始位始终为0 |

| 1-8 | 数据位 | 高位在前,低位在后 |

| 9 | 奇偶校验位 | |

| 10 | 终止位 | |

| 11 | 应答位 | 仅仅适用于主机到设备通讯 |

如果数据中有偶数个1,那么奇偶校验位置1;如果数据中有奇数个1,那么奇偶校验位置0。数据中1的个数加上奇偶校验位的总和总是一个奇数(奇校验)。奇偶校验可以用于错误检测。键盘/鼠标必须检查奇偶校验位,如果不正确,应该反馈接收到了一个无效的命令。

当从设备向主机发送数据时,在时钟的下降沿采样数据;当数据从主机向设备发送时,在时钟的上升沿采样数据。总线的时钟频率必须为10~16.7kHz。这意味着时钟高维持时间为30-50微秒,低维持时间为30-50微秒。如果设计键盘,鼠标或者主机模拟器,那么应该每个周期的中间采样数据线,比如,在时钟跳变发生后15-25微秒的时刻。同时,键盘/鼠标应当一直发出时钟信号,但是主机总是掌握着通讯的控制权。

时许是绝对重要的。

从设备到主机的通讯

数据线和时钟线都是OC接口,都需要接上拉电阻到+5V,因此在空闲状态时总线都为高电平。当键盘/鼠标需要发送数据时,首先需要确保时钟线为高电平,如果为低电平,表明主机正在禁止通讯,设备必须缓存需要发送的信息,直到主机释放时钟。在设备开始传输数据前,时钟线必须保持高电平至少50微秒。

上图为设备到主机通信示意图,当时钟为高时,数据线发生变化;当时钟为低时,数据有效。

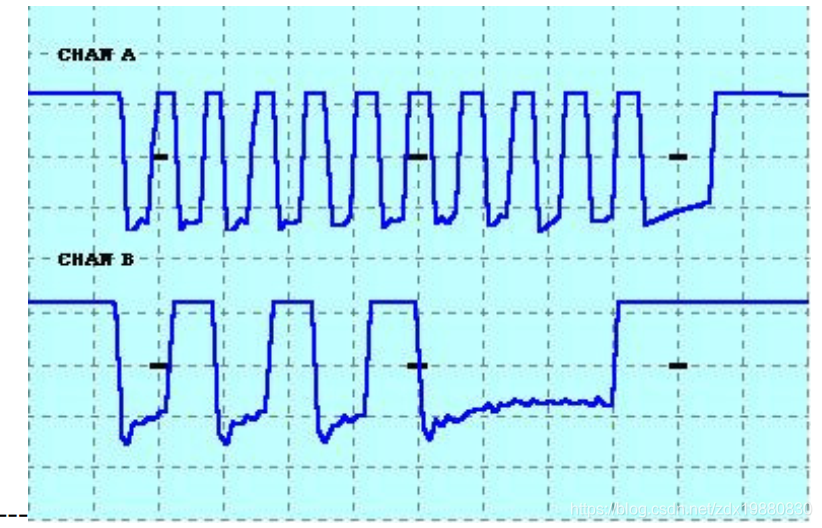

上图为“Q”键(15h)从键盘发送到电脑的测量信号图。通道A为时钟信号,通道B为数据信号。从图中可以看出每个时钟为低采样得到的位流序列:01010100001.

时钟频率范围为10-16.7kHz。从时钟上升沿到数据传输的时间间隔必须至少为5微秒;从数据传输到时钟下降沿的时间间隔大于5微秒而小于25微秒。

主机在任何情况下都可以通过拉低时钟信号持续时间大于100微秒来禁止总线通信。如果在第11个时钟脉冲前数据传输被禁止,那么设备必须放弃当前的数据传输。在主机释放时钟线后,重新传输当前的数据块。数据块可以“Make”码,“break”码,设备ID,鼠标移动包等。比如,如果键盘在发送一个2字节break码的第二个字节时被中断,那么它需要在主机释放时钟线后,重新整个break码(而不是仅仅发送被中断的字节)。

如果主机在第一个时钟下降沿前或在最后一个时钟脉冲下降沿后拉低了时钟线,键盘/鼠标并不会重新传输任何数据。然而,如果有新的数据被创建需要传输,那么新数据传输需要等待主机释放时钟线后进行。键盘拥有一个16字节的buffer来缓存数据。如果数据超过16字节,那么丢弃新产生的数据,直到buffer中有新的空间产生。鼠标仅仅存储最当前的移动数据包以便传输。

主机到设备的通讯

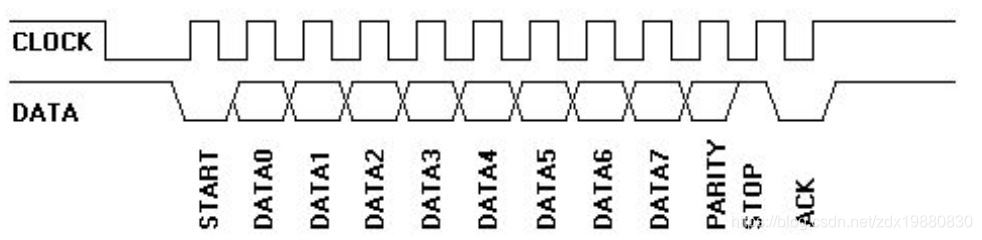

从主机到设备的数据包与从设备到主机略有差异。

首先,PS2设备需要一直产生时钟信号。如果主机想要发送数据,必须配置总线到请求-发送状态:

- 拉低时钟线持续100微秒以上,禁止通讯

- 设置请求-发送状态:拉低数据线,释放时钟线

设备应该以大于10毫秒的间隔检查请求-发送状态。当设备侦测到该状态,设备开始产生时钟信号,8个数据时钟和1个停止位时钟。主机仅仅在时钟线为低时改变数据线,仅仅在时钟线为高时读取数据。这与从设备到主机通讯模式相反。

在接收到停止位后,设备将会通过拉低数据线进行应答,并产生最后一个时钟脉冲。如果主机在第11个时钟脉冲后不释放数据线,那么设备将会继续产生时钟脉冲直到数据线被释放(然后设备将产生一个错误)。

主机可以在第11个时钟脉冲前(应答位)中止数据传输通过拉低时钟线100微秒。

简单的说,主机发送数据到PS2设备的流程如下:

- 主机拉低时钟线至少100微秒

- 主机拉低数据线

- 主机释放时钟线

- 主机等待设备拉低时钟线

- 改变数据线以便发送第一个数据位

- 等待设备拉高时钟

- 等待设备拉低时钟

- 重复5-7步骤,发送其他7个数据位和奇偶校验位

- 释放数据线

- 等待设备拉低数据线

- 等待设备拉低时钟

- 等待设备释放时钟和数据线

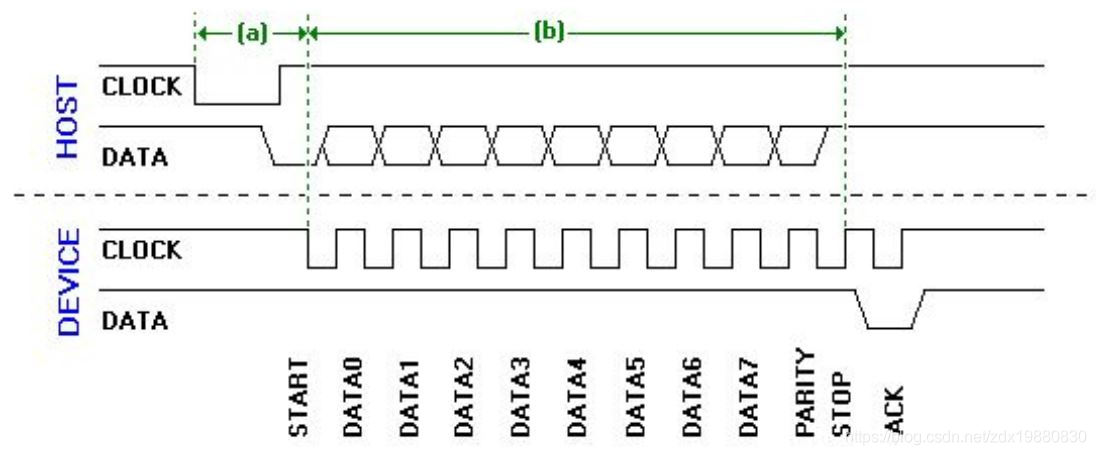

上图显示了主机到设备的通讯时序图。

上图将主机产生的信号与设备产生的信号进行区分。注意应答位的时序:数据跳变发生在时钟线为高时。

从上图中看出,有两个时间参数需要注意。

- 主机从拉低时钟线到设备开始产生时钟的时间间隔应不大于15毫秒

- 主机用来发送数据包的时间应不大于2毫秒

如果这两个时间限制有一个不满足,那么主机应该产生一个错误。

在处理数据时,在主机接收到应答位后立即拉低时钟线禁止通讯。

如果主机发送的命令需要应答,那么应答必须在主机释放时钟线20毫秒内接收到。

如果上述条件不满足,那么主机产生一个错误。