Chisel作为领域专用语言(DSL),用于构建硬件模型。待硬件模型建立后,再基于模型进行仿真、验证,以及转换。硬件模型可以转换为firrtl,也可以转换为verilog。

接下来介绍Chisel如何构建硬件模型。

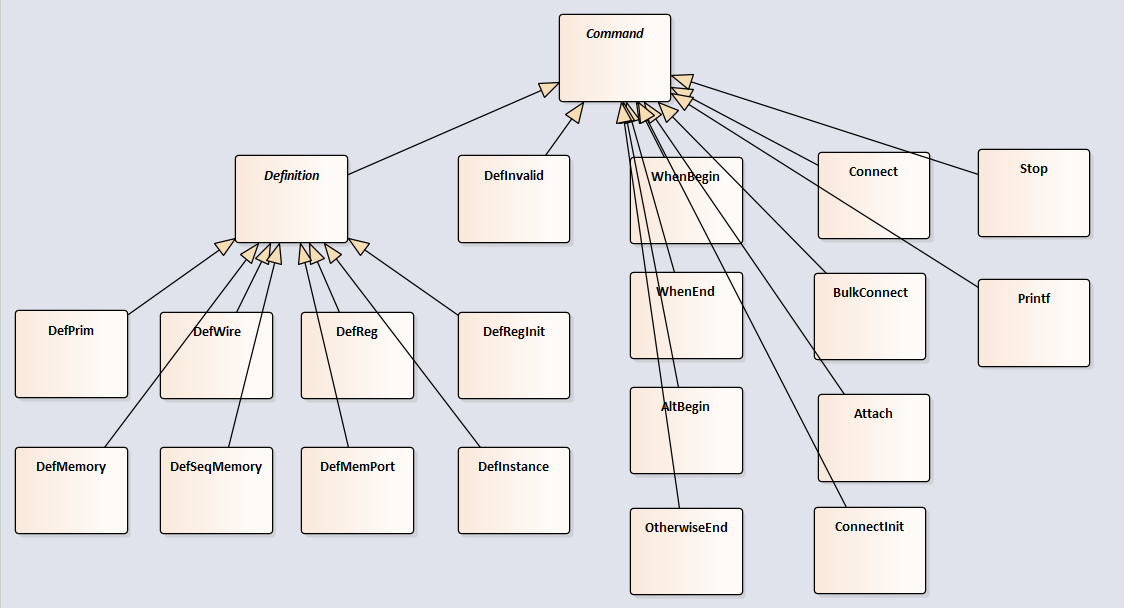

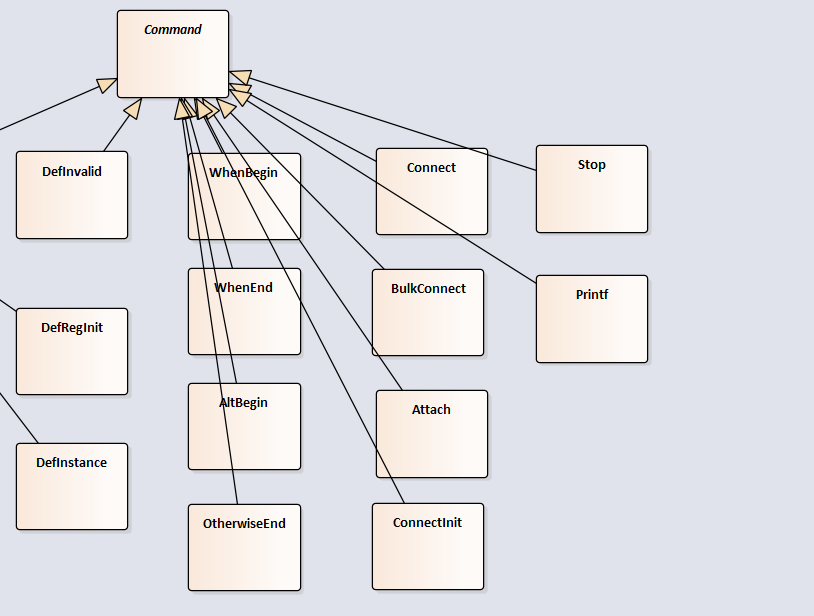

1. Command

Command定义用于构建硬件模型的命令。

命令可以分为两类:用于定义数据类型的命令,用于定义逻辑的命令。

用于定义数据的命令,称为Definition。

用于定义逻辑的命令,如下:

可以看到定义选择逻辑的命令:When/Alt/Otherwise;

还有数据之间连接的命令:Connect/BulkConnect;

软件程序中的逻辑结构有:顺序、选择、循环,三种;

而硬件中的逻辑结构只有:顺序、选择,两种;

硬件中的循环结构通过时钟实现,每个时钟可执行一次循环。但这不是物理上的硬件逻辑,而是建立在最基础的顺序、选择硬件逻辑之上,再基于时间而实现的逻辑。

所以硬件模型中,只需要顺序(基于连接)、选择(when/alt/otherwise)逻辑即可。

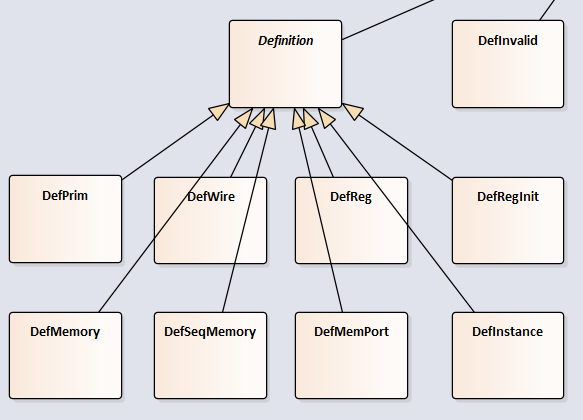

2. Definition

Definition用于定义数据,包括Wire/Reg/Mem等。

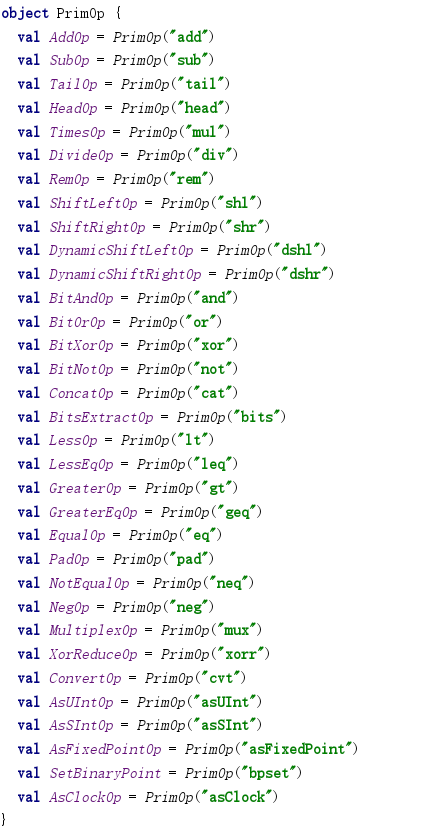

3. DefPrim

Prim是Primitive的缩写,意为原语。

PrimOp定义了各种原语操作:

DefPrim主要用于定义原语操作,但同时也定义原语操作产生的数据变量,所以DefPrim继承自Definition,而不是直接继承自Command。

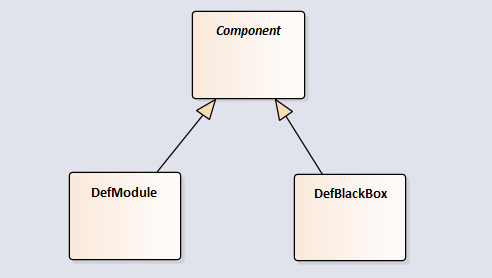

4. Component

Component定义硬件模型中的组成部分,以模块为基本单位。BlockBox是一种特殊的模块。

5. Circuit

case class Circuit(name: String, components: Seq[Component], annotations: Seq[ChiselAnnotation] = Seq.empty)

Circuit包含一系列的Component,可以视为Top Module。