文章目录

本文参考

1、【Vivado使用误区与进阶】XDC约束技巧

2、《综合与时序分析的设计约束—Synopsys设计约束(SDC)实用指南》

3、 Vivado 中的Language Template

一、XDC约束格式

set_output_delay -clock <clock_name>

-max <maxdelay>

-min <mindelay>

[get_ports <input_ports>]

-add_delay //用于DDR

-clock_fall; //用于DDR

二、系统同步接口(System Synchronous)

1、Single Data Rate(SDR),Rising Edge

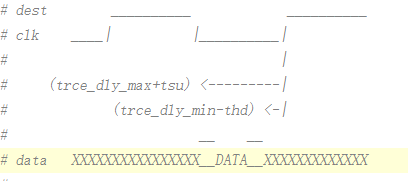

芯片间只传递数据,时钟信号的同步完全依靠板级设计对齐。仅需要考虑下游芯片的建立时间和保持时间以及板级延迟。XDC约束技巧中的例子特别好,不过这里还是以Language Template中的例子说明,注意下边时序图中的箭头,这里的参考方向变成了采样沿之前的时间。

set_output_delay -clock $destination_clock -max [expr $trce_dly_max + $tsu] [get_ports $output_ports];

set_output_delay -clock $destination_clock -min [expr $trce_dly_min - $thd] [get_ports $output_ports];

2、Double Data Rate(DDR)

DDR需要上升沿和下降沿都要约束,分析角度同上。

三、源同步接口(Source Synchronous)

在源同步接口中,定义接口约束之前,需要用set_generated_clock先定义送出的随路时钟

1、Setup/Hold Based

采用建立保持时间的角度,那么约束与系统同步约束相同。

2、Skew Based

1>、Single Data Rate(SDR),Rising Edge

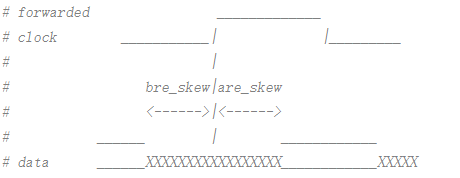

把同步数据相对与时钟的skew限定在一定范围内,可以基于Skew的大小来设置同步输出的约束。此时可以不考虑下游采样器件的建立时间和保持时间。先来看看Language Template中的例子:

# Output Delay Constraints

set_output_delay -clock $fwclk -max [expr $fwclk_period - $are_skew] [get_ports $output_ports];

set_output_delay -clock $fwclk -min $bre_skew [get_ports $output_ports];

每次看到这的时候都一脸××,但是还是要试着去理解,再画一张图。

这里可能不对,请自行取舍。在分析的时候一定要记得之前说的-max是setup分析;-min是hold分析。所以在set_output_delay的时候,数据有效窗口的大小是指的采样沿之前。

2>、Double Data Rate(DDR)

手疼,不写了。language template如下:

# Output Delay Constraints

set_output_delay -clock $fwclk -max [expr $fwclk_period/2 - $afe_skew] [get_ports $output_ports];

set_output_delay -clock $fwclk -min $bre_skew [get_ports $output_ports];

set_output_delay -clock $fwclk -max [expr $fwclk_period/2 - $are_skew] [get_ports $output_ports] -clock_fall -add_delay;

set_output_delay -clock $fwclk -min $bfe_skew [get_ports $output_ports] -clock_fall -add_delay;

再画出时序图:

注意:

1、set_input_delay把启动时钟(源时钟)作为参考时钟。

2、set_output_delay把采样时钟(目的时钟)作为参考时钟。