文章目录

本文参考

1、【Vivado使用误区与进阶】XDC约束技巧

2、《综合与时序分析的设计约束—Synopsys设计约束(SDC)实用指南》

3、 Vivado 中的Language Template

一、XDC约束格式

set_input_delay -clock <clock_name>

-max <maxdelay>

-min <mindelay>

[get_ports <input_ports>]

-add_delay //用于DDR

-clock_fall; //用于DDR

-max <maxdelay>描述了用于setup分析的包含有板级走线和外部器件的延迟。

-min <mindelay> 描述了用于hold分析的包含板级走线和外部器件的延迟。

二、系统同步接口(System Synchronous)

上游芯片只传递数据,时钟信号由系统板级同步,在系统层面上时钟信号同源,故板级走线也很重要(要学习下orcad)。

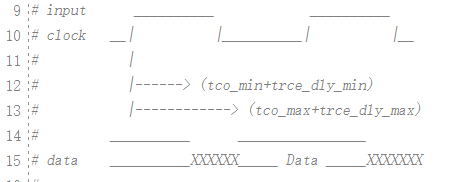

1、Single Data Rate(SDR),Rising Edge

这里的-max为tco_max + trce_dly_max,是时钟、数据延迟加上板级延迟的最大值,用于setup分析。这个值会影响建立时间裕量。同样-min为tco_min +trce_dly_min是时钟、数据延迟加上板子走线的最小延迟。这个值影响保持时间裕量。如果以此种约束下发生了时序违例,只能修改逻辑代码和修改PCB板级布线。

set input_clock <clock_name>; # Name of input clock

set tco_max 0.000; # Maximum clock to out delay (external device)

set tco_min 0.000; # Minimum clock to out delay (external device)

set trce_dly_max 0.000; # Maximum board trace delay

set trce_dly_min 0.000; # Minimum board trace delay

set input_ports <input_ports>; # List of input ports

# Input Delay Constraint

set_input_delay -clock $input_clock -max [expr $tco_max + $trce_dly_max] [get_ports $input_ports];

set_input_delay -clock $input_clock -min [expr $tco_min + $trce_dly_min] [get_ports $input_ports];

2、Double Data Rate(DDR)

系统不同结构的数据传递性能受到时钟在系统级的走线延迟和skew,以及数据路径延迟的多重限制,一般仅仅用于SDR的方式。不过language template中也有这个例子,可以学习分析下。

set_input_delay -clock $input_clock -max [expr $trco_max + $trce_dly_max] [get_ports $input_ports];

set_input_delay -clock $input_clock -min [expr $trco_min + $trce_dly_min] [get_ports $input_ports];

set_input_delay -clock $input_clock -max [expr $tfco_max + $trce_dly_max] [get_ports $input_ports] -clock_fall -add_delay;

set_input_delay -clock $input_clock -min [expr $tfco_min + $trce_dly_min] [get_ports $input_ports] -clock_fall -add_delay;

分析的角度是一样的,不同之处就是下降沿也做了约束。

三、源同步接口(Source Synchronous)

源同步是为了消除系统同步中频率受限的不足而发展而来的,在发送端将数据和时钟同步传输,在接收端用时钟沿锁存数据;理论上源同步不受传输延迟的影响。源同步除了SDR、DDR的分别外,由于clk和data同时传输,还分clk和data中心对齐和边缘对齐。

1、Center Aligned

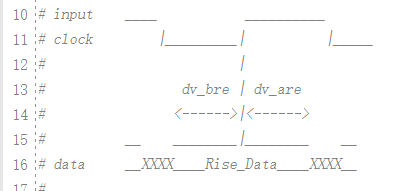

1>、Single Data Rate(SDR),Rising Edge

若果知道上游芯片的时钟延迟和板级延迟,也可以从系统的角度分析,这种分析是由系统参数决定了的。源同步时一般知道数据的有效窗口的大小。也可以采用有效窗口来确定最大最小延迟。

dv_bre:Data Valid Before Rising Edge

dv_are:Data Valid After Rsing Edge

# Input Delay Constraint

set_input_delay -clock $input_clock -max [expr $input_clock_period - $dv_bre] [get_ports $input_ports];

set_input_delay -clock $input_clock -min $dv_are [get_ports $input_ports];

最大延迟为周期T-dv_bre,最小延迟为:dv_are。不论是系统角度(由Tcko)还是源同步的方法,时序分析的结果应该是一样的(建立时间裕量和保持时间裕量应该有不同才是)。Ally给的例子两者的-max和-min都是一样的;但是实际中可能并非如此。因为式 ,建立时间裕量是一个范围。同理保持分析也一样。总体来说,还是更推荐采用数据有效窗口的源同步分析。

2>、Double Data Rate(DDR)

中心对齐DDR形式的数据约束与中心对齐SDR类似,不同之处是上升下降沿都要约束,并且每个沿也就只有T/2的总时间,也就是周期的一半。具体可以参照Language Template中的例子。

2、EdgeAligned

在Vivado的Language Template中,边缘对齐的情况又分为:1、Clock with MMCM 。 2、Clock directly to FF。第二种要比第一种多一个周期的时间,当然DDR是周期的一半时间。这只理出来Clock with MMCM的情况。

1>、Single Data Rate(SDR),Rising Edge

图中的红线是最大的延迟,蓝箭头指的是最小的延迟;也就是说最大最小延迟决定了数据有效窗口的大小。这也和源同步中心对齐是一样的。

# Input Delay Constraint

set_input_delay -clock $input_clock -max $skew_are [get_ports $input_ports];

set_input_delay -clock $input_clock -min -$skew_bre [get_ports $input_ports];

2>、Double Data Rate(DDR)

边缘对齐的DDR其实也是和SDR一样的,不同之处是下降沿也要约束。但是在实际应用当中,还是通过MMCM/PLL把采样时钟进过一定的相依,使之成为中心对齐的形式。