VIVADO创建工程置流水灯

1、 概述

首先创建FPGA工程,编写Verilog代码,然后添加管脚约束,最后进行编译,将产生的bit文件下载到开发板中。本次实验,FPGA开发板断电后,bit文件就会消失。如果想要保证开发板上电后就能运行程序,则需要把bit文件打包成bin或者MCS文件,然后固化到FLASH中才可以。这个方法以后再详细说明。

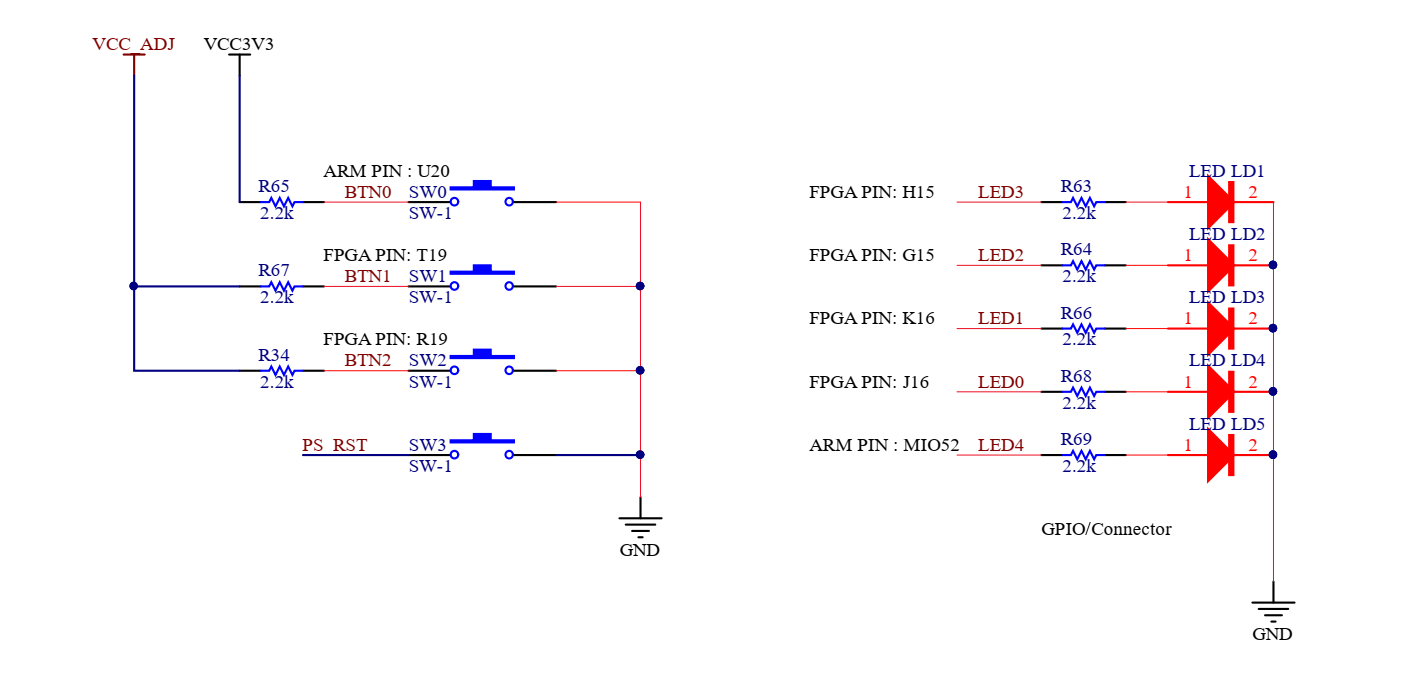

2、 硬件原理图

3、 Verilog工程代码run_led.v

module run_led( //定义输入输出变量

input CLK_i,

input RSTn_i,

output reg [3:0] LED_o

);

reg [31:0] C0; //设置时间变量

always @(posedge CLK_i) //上升沿触发

if(!RSTn_i) //没有复位

begin

LED_o <= 4'b1; //类似于初始化,led第一位置1

C0 <= 32'h0; //变量初始化C0置零

end

else

begin

if(C0 == 32'd50_000_000) //当C0累加到这个数时,

begin

C0<=32'h0; //C0清零

if(LED_o ==4'b1000) //当LED只有第四位为1时

LED_o<=4'b1; //LED移位,只有第一位为1

else

LED_o<=LED_o<<1; //LED的1左移一位

end

else

begin

C0<=C0 + 1'b1; //C0累加1

LED_o <= LED_o;

end

end

endmodule

4、 约束文件代码fpga_pin.xdc

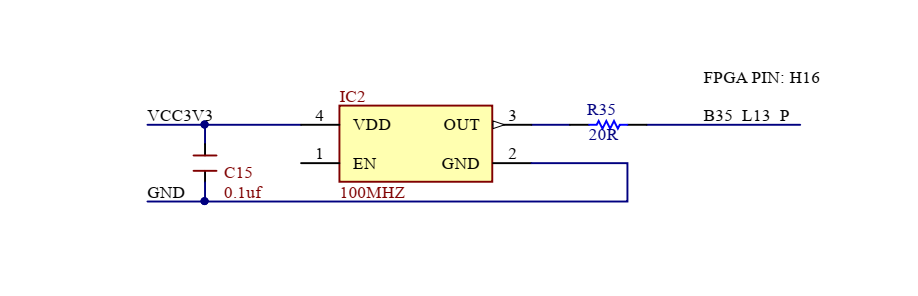

create_clock -period 10.000 -name CLK_i [get_ports CLK_i] //创建一个始终,周期为10

set_property PACKAGE_PIN H16 [get_ports CLK_i] //管脚约束 时钟引脚

set_property IOSTANDARD LVCMOS33 [get_ports CLK_i] //电平约束 LVCMOS电平标准:

//所有引脚号都与原理图一一对应

set_property PACKAGE_PIN T19 [get_ports RSTn_i] //复位引脚

set_property IOSTANDARD LVCMOS33 [get_ports RSTn_i]

set_property PACKAGE_PIN J16 [get_ports {LED_o[0]}] //led灯的配置

set_property PACKAGE_PIN K16 [get_ports {LED_o[1]}]

set_property PACKAGE_PIN G15 [get_ports {LED_o[2]}]

set_property PACKAGE_PIN H15 [get_ports {LED_o[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[*]}] //led灯电平标准

#bit compress //压缩

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design] //板卡配置电压约束

set_property CFGBVS VCCO [current_design] //CFGBVS管脚连接至上拉电压VCCIO(3.3V)

set_property CONFIG_VOLTAGE 3.3 [current_design] // //配置电压也连接至3.3V

5、 感悟

FPGA学习感觉根单片机学习很像,都需要读懂原理图,有一定的编程思维。C语言编程都是先寻找一个个子零件,慢慢拼凑,最后拼成一个大零件,从而实现某个功能,编程思想是从底层出发慢慢走向顶层。Verilog编程恰恰相反,它是从顶层出发,发现此时需要什么,再去寻找什么,最后把底层都找到。