写控制完成后开始设计读控制,写控制和读控制是非常相似的。

一、总线详解

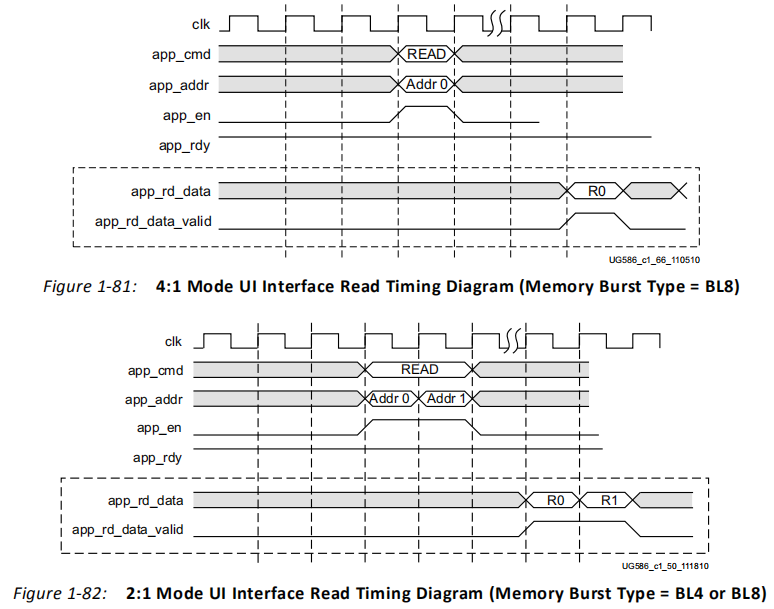

由 User Guide 可知各信号之间的逻辑关系,读数据是在给出命令之后一段时间后开始出现的。图中没有给出app_rd_data_end信号,此信号和app_wdf_end是相同的,即在DDR3的物理层端与用户端存在两种速率情况,此次设计速率为4:1,app_rd_data_end 和 app_rd_data_valid 相同。

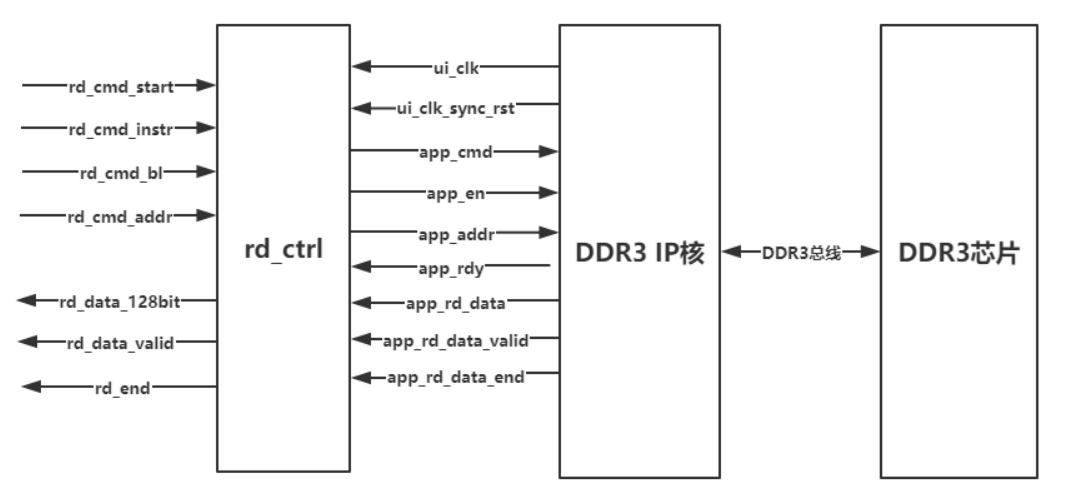

二、读控制模块设计

本次设计读控制模块,试着将之前写控制模块的64个128bit数据读回来,并最终进行仿真验证。写控制模块框图如下所示:

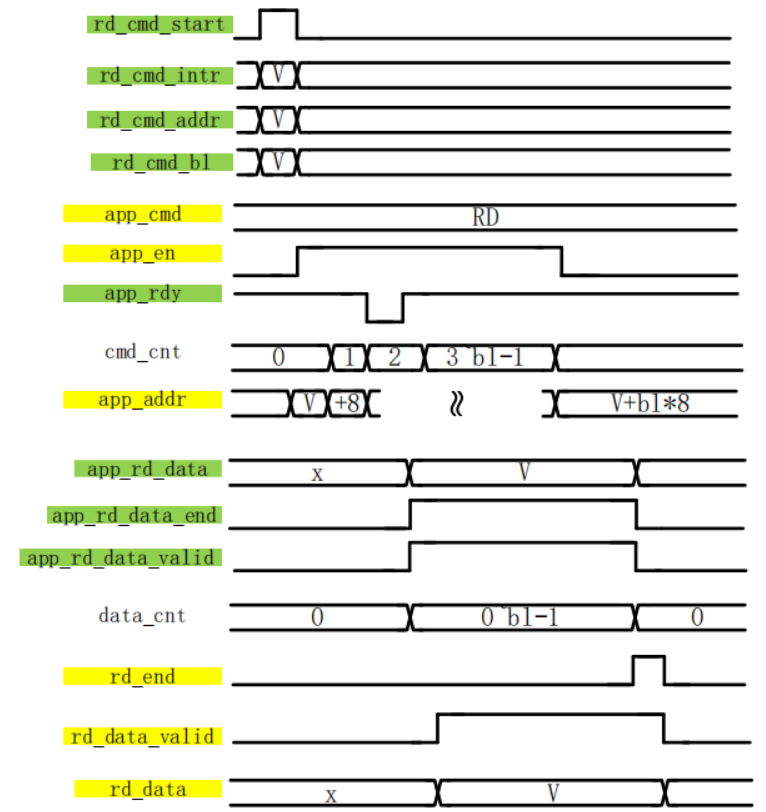

当 rd_cmd_start 有效时,启动本次的读突发,根据由外部输入的 rd_cmd_bl 可以确定本次突发需要读多少个数据。wr_cmd_addr 代表本次突发读的起始地址,数据是128bit的,一个地址能存16bit,因此每个128bit数据需要占用8个地址,即每次的地址计数+8。wr_end 用于告知其他模块,本次突发写结束。

本次设计均学自《威三学院FPGA教程》,具体代码就不贴了。

三、读控制模块仿真