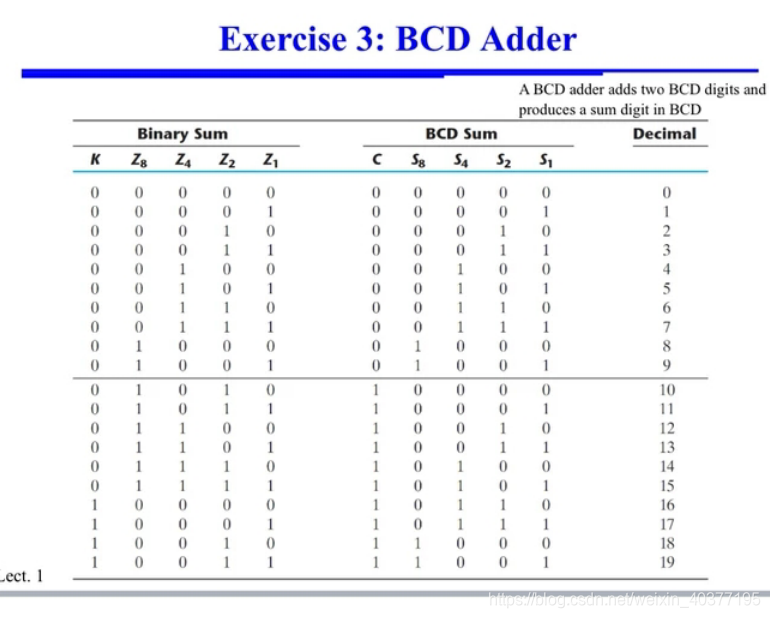

1.题目

2.源码

// *********************************************************************************

// Project Name : BCD_adder

// Email : [email protected]

// Website : https://home.cnblogs.com/u/hqz68/

// Create Time : 2019/12/11

// File Name : BCD_adder.v

// Module Name : BCD_adder

// Abstract :

// editor : sublime text 3

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// 2019/12/11 宏强子 1.0 Original

//

// *********************************************************************************

`timescale 1ns/1ns

module BCD_adder (

input [3:0] a ,

input [3:0] b ,

output reg [3:0] sum ,

output reg c

);

//========================================================================\

// =========== Define Parameter and Internal signals ===========

//========================================================================/

reg [4:0] sum_r ;

//=============================================================================

//**************************** Main Code *******************************

//=============================================================================

always @ (a or b) begin

sum_r = a + b;

end

always @ (sum_r) begin

if (sum_r >4'd9) begin

sum = sum_r - 4'd10;

c = 1'b1;

end

else begin

sum = sum_r;

c = 1'b0;

end

end

endmodule3.测试平台

`timescale 1ns/1ns

module tb_bcd_adder();

reg [3:0] a ;

reg [3:0] b ;

wire [3:0] sum ;

wire c ;

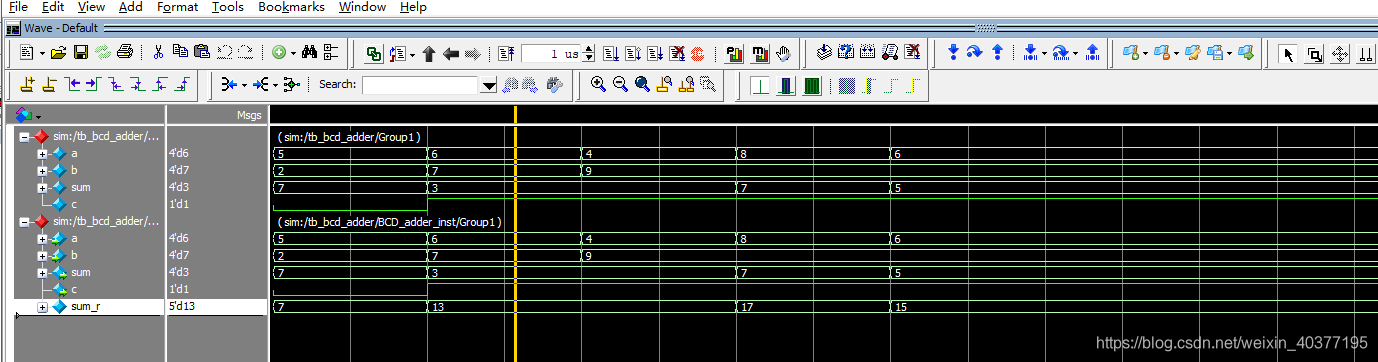

initial begin

a = 4'd5;

b = 4'd2;

#100

a = 4'd6;

b = 4'd7;

#100

a = 4'd4;

b = 4'd9;

#100

a = 4'd8;

b = 4'd9;

#100

a = 4'd6;

b = 4'd9;

end

BCD_adder BCD_adder_inst(

.a (a ),

.b (b ),

.sum (sum ),

.c (c )

);

endmodule4.仿真波形