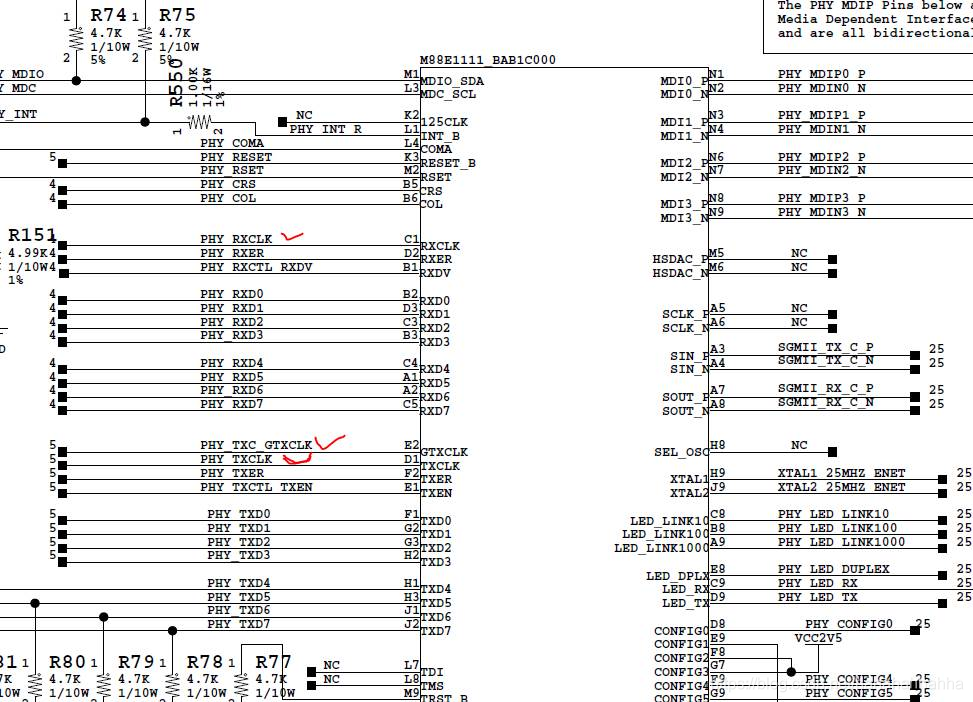

硬件以太网PHY芯片有三个时钟,对此进行了梳理:

PHY芯片时钟的选择:

PHY芯片中有3个时钟, Gtx_clk,Rx_clk ,Tx_clk。

GTX_CLK仅使用在GMII模式下,时钟频率为125M,发送数据时的时钟。

RX_CLK 在GMII和MII模式下均可使用,网络接收数据的时钟。

TX_CLK仅使用在MII模式下,发送数据时的时钟。

与MII接口相比,GMII的数据宽度由4位变为8位,GMII接口中的控制信号如TX_ER、TX_EN、RX_ER、RX_DV、CRS和COL的作用同MII接口中的一样,发送参考时钟GTX_CLK和接收参考时钟RX_CLK的频率均为125MHz(1000Mbps/8=125MHz)。

在这里有一点需要特别说明下,那就是发送参考时钟GTX_CLK,它和MII接口中的TX_CLK是不同的,MII接口中的TX_CLK是由PHY芯片提供给MAC芯片的,而GMII接口中的GTX_CLK是由MAC芯片提供给PHY芯片的。两者方向不一样。

在实际应用中,绝大多数GMII接口都是兼容MII接口的,所以,一般的GMII接口都有两个发送参考时钟:TX_CLK和GTX_CLK(两者的方向是不一样的),在用作MII模式时,使用TX_CLK和8根数据线中的4根。

附件为KC705原理图,第25页是M88E1111的连接图