Xilinx FPGA 架构简介

作者:AirCity 2020.2.4

[email protected] 本文所有权归作者Aircity所有

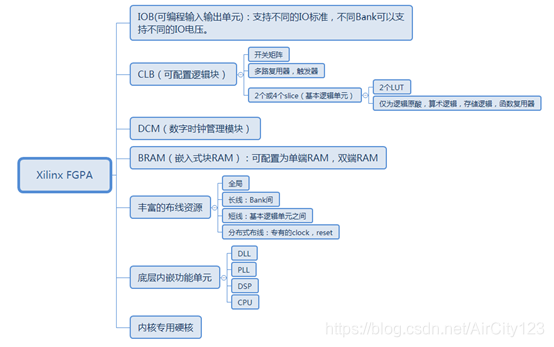

直接用一张图来说明Xilinx FPGA都包含哪些核心内容:

LUT,Look up table的简称,本质上是一个RAM,目前FGPA中多使用4输入的LUT,每一个LUT可以看成一个有4位地址线的16x1 RAM(16个1bit存储空间)。HDL语言描述了一个逻辑电路后,软件会自动计算所有可能的运算结果,并把结果写入到RAM中,这样每输入一个信号就相当于输入一个地址进行查表,找出地址响应内容。

由于制造工艺所限,FPGA都有漏电流存在,漏电流受内核VCCINT影响很大,大约与其立方成正比。如果VCCINT提升5%,静态功耗会增加15%之多。因此要控制好VCCINT的纹波水平。

FPGA与CPLD的区别

| FPGA | CPLD |

|---|---|

| SRAM工艺,基于LUT结构 | EEPROM工艺,乘积项结构 |

| 基本单元为CLB,颗粒度小,延迟与系统布局有关 | 基本单元是LCM(可编程逻辑宏单元),颗粒度大,特点是延迟相等 |

| 适用于数据密集型场合,完成复杂时序逻辑,需要大量触发器 | 适用于控制密集型场合,输入较多,复杂,完成组合逻辑。 |

Xilinx Virtex 5上电要求:

VCCINT:1V

VCCAUX:2.5V,Drop≤10mV

VCCO_X:3.3V

以上三个电压,没有时序要求!但是有Ramp time要求,都是0.2~50ms。切记,这个时间是很重要的,如果不满足可能引起芯片工作异常。