Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

软件主要特点:

RTL和门级优化,本地编译结构,编译仿真速度快,跨平台跨版本仿真;

· 单内核VHDL和Verilog混合仿真;

· 源代码模版和助手,项目管理;

· 集成了性能分析、波形比较、代码覆盖、数据流ChaseX、Signal Spy、虚拟对象Virtual Object、Memory窗口、Assertion窗口、源码窗口显示信号值、信号条件断点等众多调试功能;

· C和Tcl/Tk接口,C调试;

· 对SystemC的直接支持,和HDL任意混合;

· 支持SystemVerilog的设计功能;

· 对系统级描述语言的最全面支持,SystemVerilog,SystemC,PSL;

· ASIC Sign off。

· 可以单独或同时进行行为(behavioral)、RTL级、和门级(gate-level)的代码。

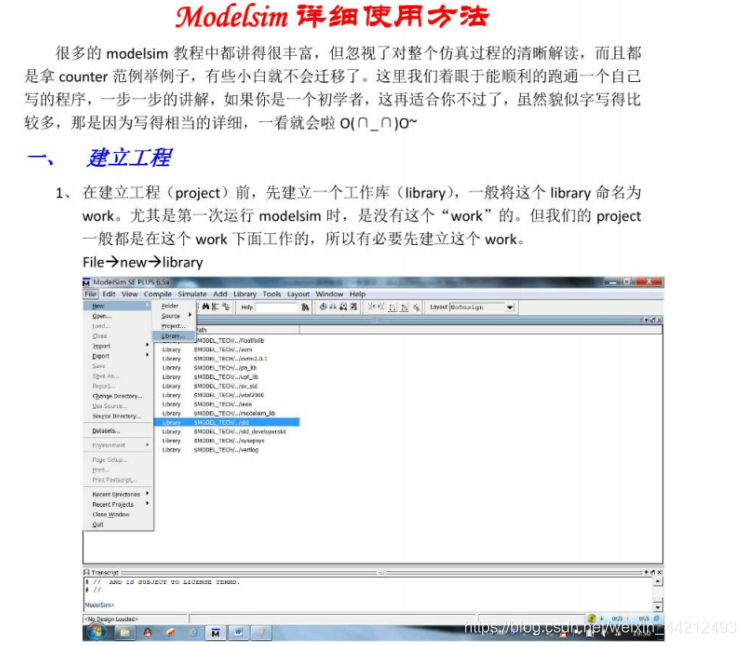

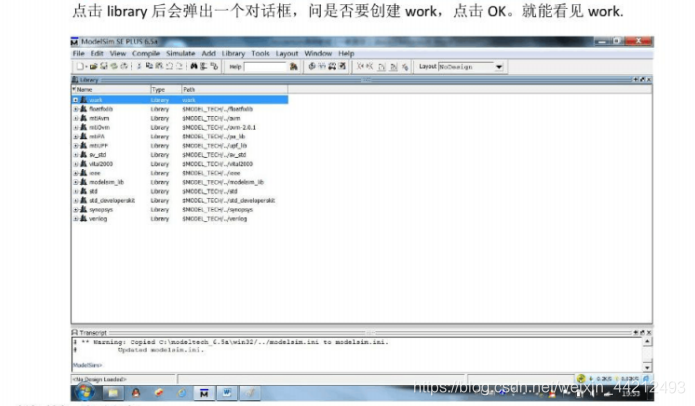

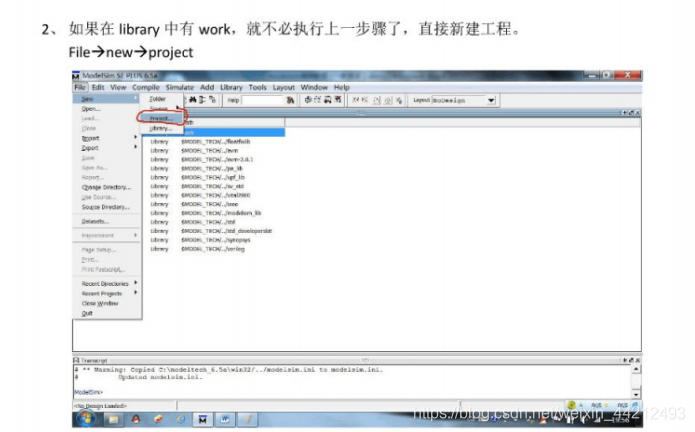

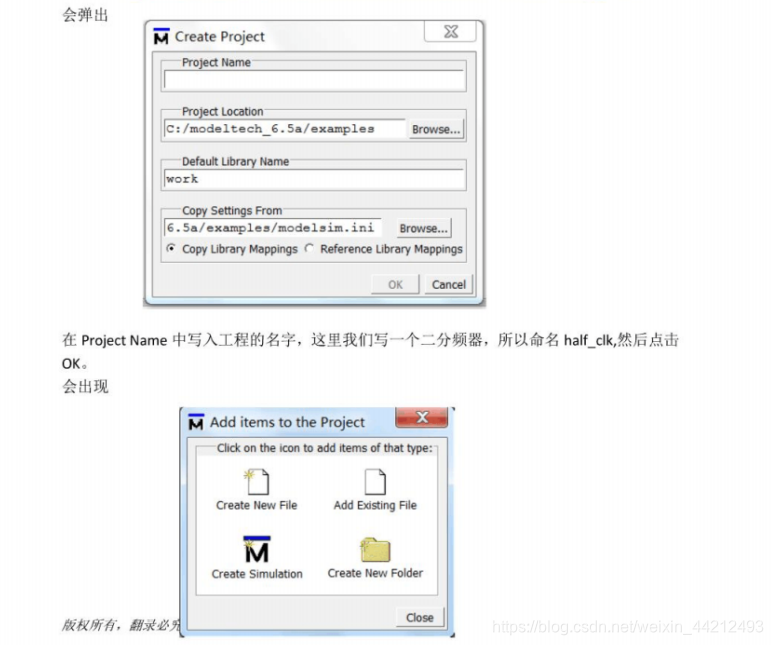

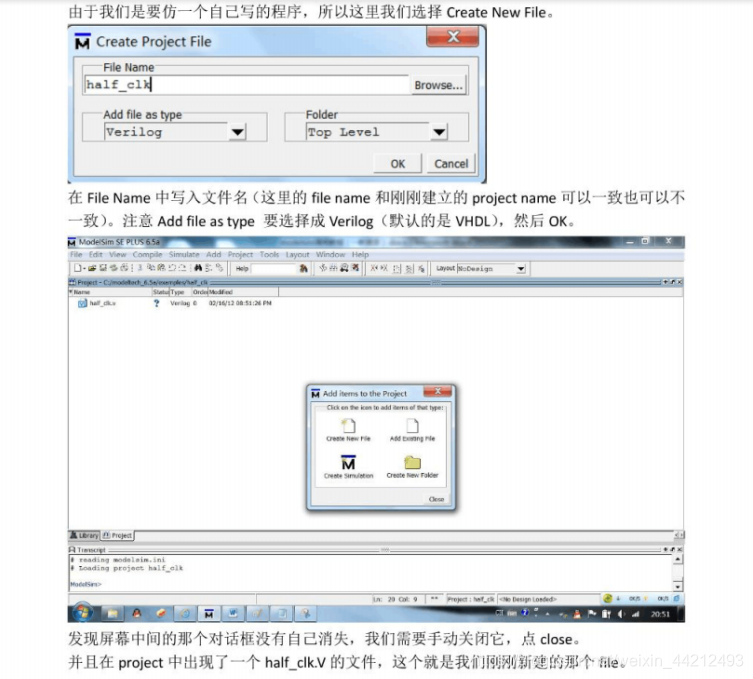

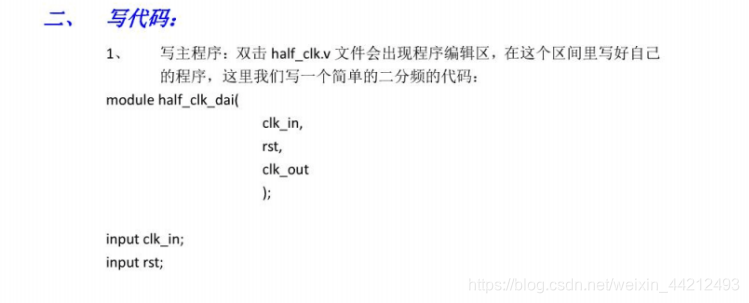

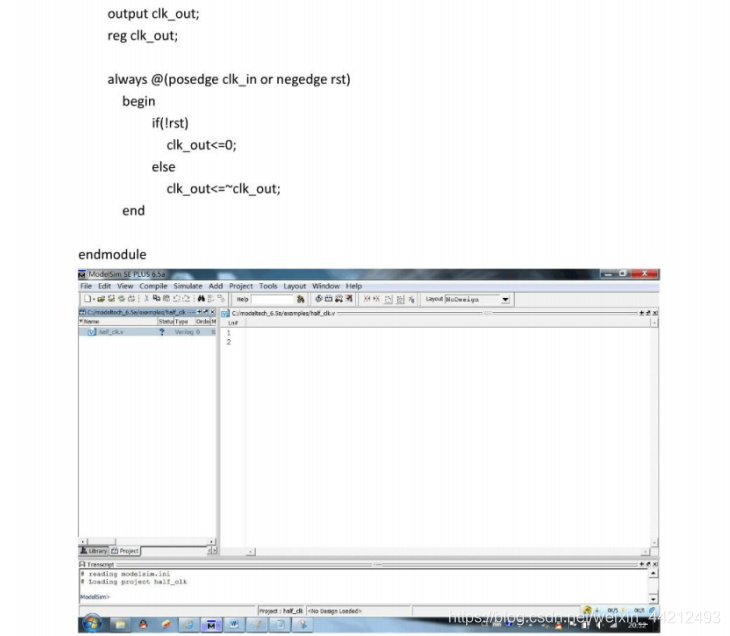

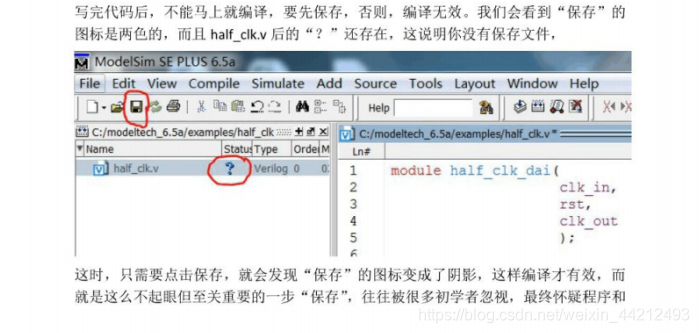

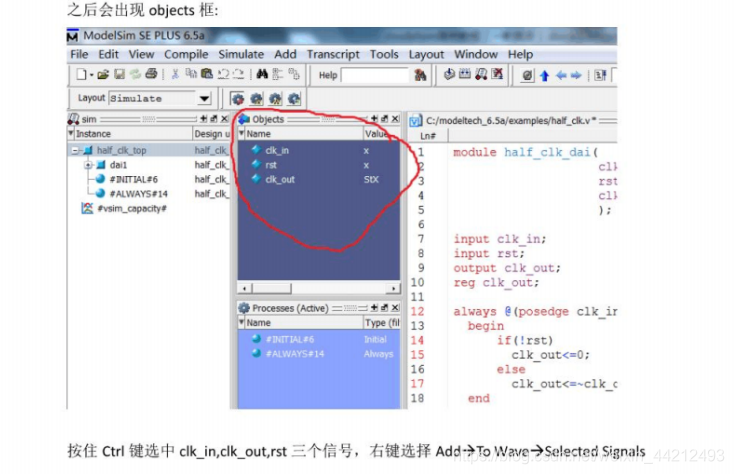

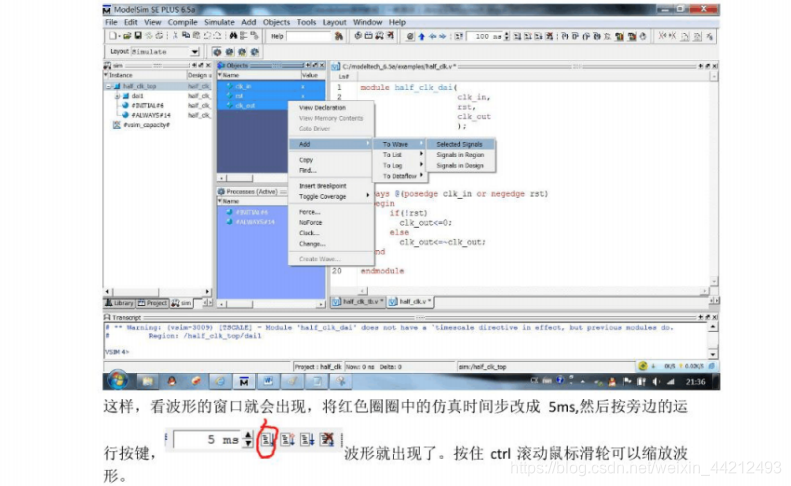

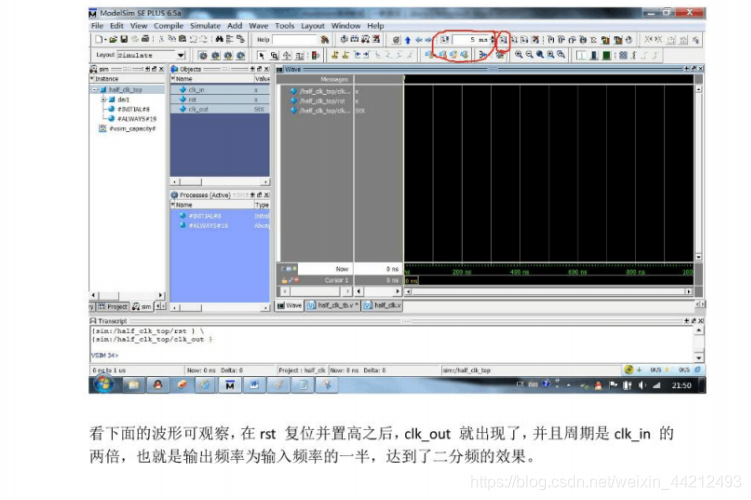

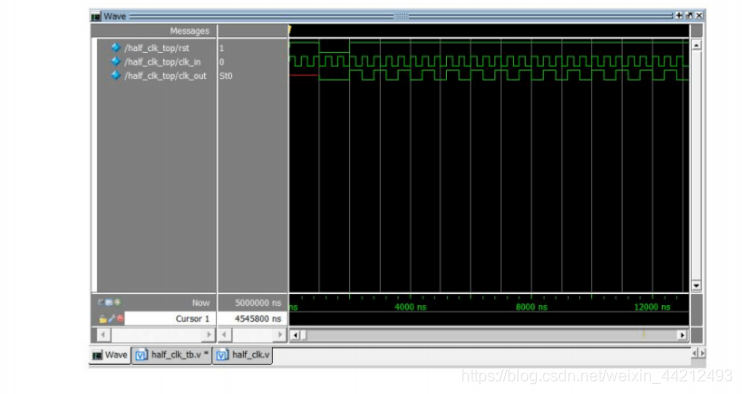

好了,开始我们的教程,下面我们利用Modelsim 做一个简单的二分频的仿真

好了,教程到这里就结束了,是不是很简单啊,大家有什么问题或者不明白的地方,随时给我留言啊,我们一起学习共同进步啊!

最后,如果有什么意见或者建议欢迎您留言给我,让我们共同学习一起进步,

如果需要 完整代码或设计文件,请在下方留言或者私信我,看到后会第一时间回复。

谢谢!