本人之前只用过FPGA做过项目,最近对znyq-7000 产生了兴趣,几乎是从零开始学。

主要基于zynq-7000 Soc 的设计指南进行学习。(何宾)

书上内容太多,在此需要掌握的知识点进行总结,一些最基础的知识点不做详述(在这段不太忙的是时间里,持续更新)

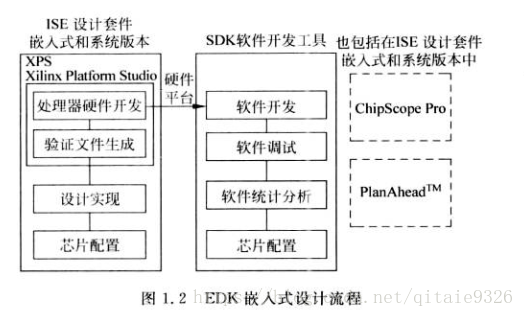

设计流程

就是软硬件结合的过程。软件流程完成C语言的编写,编译,链接的过程,硬件流程完成HDL 设计输入,综合,仿真,实现。

主要利用XPS,可以将C语言生成的ELF 文件代码插入生成的FPGA比特流文件中,将其生成下载到FPGA 中。

对于简单了解可编程Soc的设计流程和开发环境,强烈建议完成Helloword的整个流程,具体在如下的链接当中(ISE)

https://blog.csdn.net/luoqindong/article/details/42968693

开发工具

XPS 硬件设计环境,创建完整的嵌入式系统硬件结构;提供编辑器和项目管理接口用来创建和编辑源代码;提供工具流程配置选项的定制和提供图形化的系统编辑器用来连接处理器。外设和总线

SDK 软件设计环境,用于开发软件应用功能;导入基于XPS生成的硬件平台定义

平台

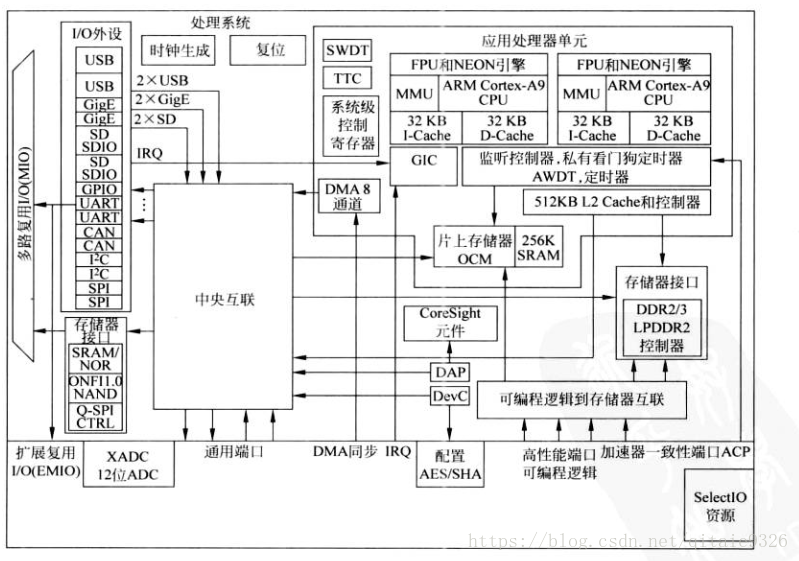

基于PS(ARM Cortex-A9)和PL (FPGA)

双核ARM 的多核CPU 是“心脏”

具体的PS.PL特性用到后在详细叙述

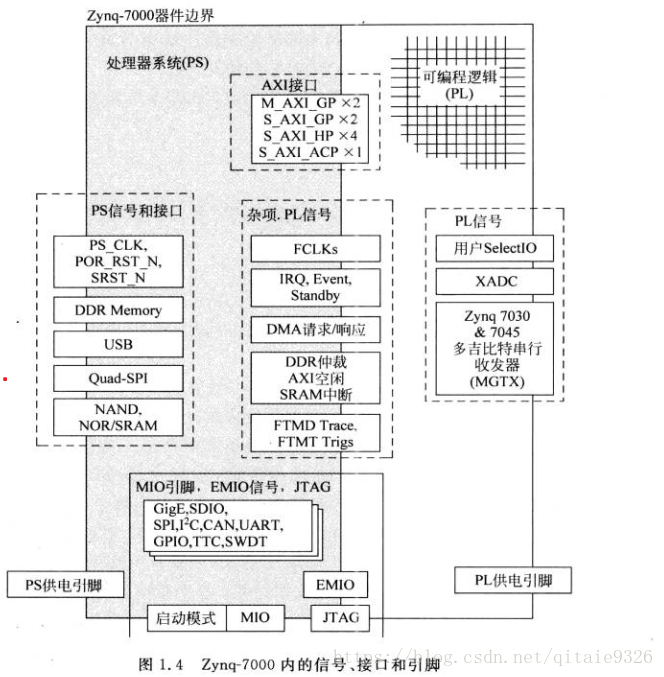

ZYNQ信号,接口和引脚

PS和PL 供电是独立的,强调!!必须在PL 供电以前,给PS 供电。PS 包括独立的供电,用于DDR I/O和用于MIO的两个独立电源组

PS 和外部接口之间的通信主要是通过复用的输入 / 输出(Multiplexed Input/Output,MIO)实现的,它提供了可以做灵活配置的 54 个引脚,这表明外部设备和引脚之间的映射是可以按需定义的。这样的连接也可以通过扩展 MIO (Extended MIO,EMIO)来实现,EMIO 并不是 PS 和外部连接之间的直接通路,而是通过共用了 PL 的 I/O 资源来实现的

USB、四-SPI 和SMC接口不能使用EMIO 接口连接到PL。在EMIO通信发生前,必须通过LVL_SHFTR_EN使能PL电平装换器