什么是LDPC?

LDPC码即低密度奇偶校验码(Low Density Parity Check Code,LDPC),它由Robert G.Gallager博士于1963年提出的一类具有稀疏校验矩阵的线性分组码,不仅有逼近Shannon限的良好性能,而且译码复杂度较低, 结构灵活,是近年信道编码领域的研究热点,已广泛应用于深空通信、光纤通信、卫星数字视频和音频广播等领域。

LDPC码由一个包含少量非零元素的mxn校验矩阵H的零空间定义。如果矩阵H中的非零元素仅为“1”,则将矩阵H的零空间所定义的LDPC码称为二元LDPC码,同理可得出多元LDPC码的定义。如果校验矩阵H具有固定的行重和列重,那么由该校验矩阵定义的LDPC码是规则的,否则称为非规则的LDPC码。非规则的LDPC码的性能与H的行重和列重密切相关。为了获得较好的性能,LDPC码在构造的噶城中需要对校验矩阵H做出限制,即任意两行(两列)同时为非零元素的位置不能超过一个,这个性质被称为行列约束。

LDPC码校验矩阵H的典型特征是密度(H中的非零元素比例)较低。众所周知,对一般线性分组码来说,最优解码算法(例如最大似然解码)由于过高的复杂度很难应用倒实际的系统中,所以无法获得最优解码性能。而LDPC码的低密度特性使它正好适合于迭代解码,在许多应用场景下,LDPC码在采用迭代解码时能够在许多感兴趣的误码率区域去爹接近最大似然解码的性能。

为什么5G采用LDPC编码

目前为止,影响力最大的三类先进的现带纠错编码方式分别时Turbo码、LDPC码和极化(polar)码,所以LDPC码、Turbo码和Polar码被3GPP定为数据信道候选纠错编码方案。

Turbo码在高吞吐率和误码平层性能方面存在短板;Polar码的BLER性能虽然非常的优异,但是在大码块传输时SCL解码算法的复杂过高,目前的技术难以支持20Gbit/s的峰值吞吐率,而支持高吞吐率的低复杂度算法却存在着较大的性能损失;LDPC码具有较低的解码复杂度,非常适合并行解码、支持高吞吐量传输,设计恰当的LDPC码具有很低的误码平台,完全可以满足5G支年高吞吐率传与可靠性方面的需求。

经过恰当设计的LDPC码性能优异,在AWGN信道性性能明显优于Turbo码,仿真结果还表明与其他候选方案相比,高码率的LDPC码复杂度最低、性能最好。这些技术原因在促使LDPC码被NR采纳为eMMB数据信道编码方案方面发挥了重要的作用。同时,LDPC码在uRLLC场景的研究也证明了其性能的优越性,在NR表混中也被接受为数据信道编码方案。

控制信道编码同样非常重要, 性能优异的纠错编码能够显著提高系统的整体性能,扩大小区覆盖。由于控制信令比特数较少,LDPC码、Tubo码在码长较短时性能较差、所以LTE采用了咬尾卷积编码( Tail Biting Convoltioal Colding. TBCC)作为信道编码方案,鉴于Polar码在控制信道小分组传输时的复杂度可以接受,性能优于TBCC及其它方案,所以采用Polar码为控制信道纠错编码方案。

5G NR LDPC码的设计

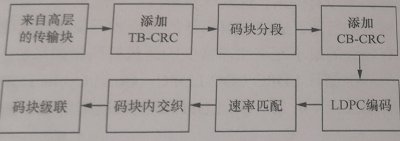

LDPC码的编码流程

QC-LDPC码

QC-LDPC(Quasi-Cyslic Low-Density Parity-Check Codes)即准循环LDPC码。LDPC码基本属于随机构造法,构造出的码性能很好,但校验矩阵具有不规律性,存在校验矩阵存储于读取困难、编码复杂度高等问题,相对难以实现。准循环LDPC码是结构化LDPC码的重要子集,其奇偶校验矩阵可以分成多个大小相等的方阵,每个方阵都是单位矩阵的循环移位矩阵或全0矩阵,非常便于存储器的存储和寻址,从而大大降低了LDPC码的编译码复杂度,并且具有重复累计结构的准循环LDPC码能够实现线性复杂度的快速编码。因此,目前实际中所使用的LDPC码大都使用这种校验矩阵构造方式。

鉴于QC-LDPC的优良特性,NR LDPC码也采用了这种准循环结构。

基图

5G NR采用QC-LDPC码,BG是整个LDPC码设计的核心。BG是LDPC码PCM(Parity-Check Matrix, 校验矩阵)设计的前提,也决定了LDPC码的宏观特性和整体性能。在5G NR中,为适应不同通信场景的需求,LDPC码必须能够灵活地支持不同的码长和码率。同时,为提高通信可靠度,IR-HARQ 也是LDPC码必须支持的一项特性。

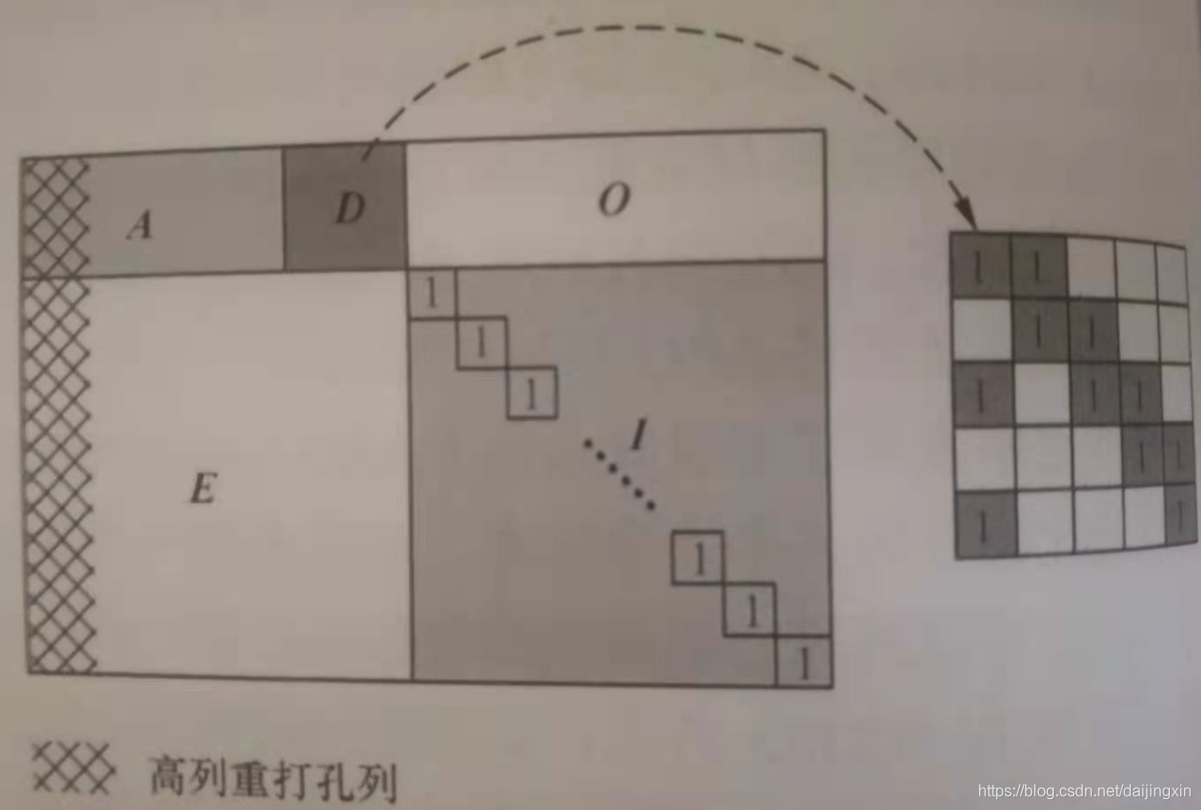

在采纳LDPC码作为数据编码方案的同时,3GPP 会议也同期确定通过对一个高码率PCM进行下行角的码字扩展,以支持IR-HARQ和速率匹配。后续会议上,各公司同意把5G NR LDPC码PCM做如图的划分。

NR LDPC码的基础矩阵有五个部分,其中A矩阵和E矩阵都是循环置换矩阵和全零矩阵组成的矩阵阵列,O矩阵为全零矩阵,I矩阵为单位矩阵。并且A矩阵对应系统信息位,D矩阵对应校验信息位,矩阵[A D]对应一个高码率的LDPC码,矩阵[E I]对应支持IR-HARQ的扩展冗余比特,其中单位矩阵I实际上对应一个度为1的单校验比特。所以该结构等价于一个高码率LDPC码与多个单校验码串行级联,并且可以随着扩展矩阵行数和列数的增加来得到码率任意低的码率LDPC校验矩阵,从而NR LDPC码的校验矩阵可以支持IR-HARQ与灵活的编码码率。

通过进一步对比各个厂商所提矩阵的BLER,最终决定采用2个独立的BG。标准确定的BG2稍显特殊,可以通过删除Hcore中的部分列,实现BG大小随着信息块大小的变化而变化。具体来说,当信息块小于等于192时,Hore 的列数为10;当信息块大于192且小于560时, Hcore的列数为12;当信息块大于 560小于等于640 时,Hcore 的列数为13;当信息块大于640时,Hcore 的列数为14。

BG1 的大小是46x68,Hcore的大小为4x26,Hext的大小为42x26。支持的最低码率为1/3。主要用于对吞吐要求较高、码车较高、码长较长的场景。

BG2 的大小为42x52,Hcore的大小为4x14, Hext的大小为38x14。主要用于对吞吐量要求不高,码率较低,码长较短的场景。

5G NR LDPC码BG中前两列属于大列重,所谓大列重就是指这两列中1的数量明显大于其他列。这样做的好处是在译码过程中加强消息流动,增加校验方程之间的消息传递效率。右下角是对角阵,支持IR-HARQ,每次重传只需要发送更多的校验比特即可。

矩阵散列 & PCM

一个QC-LDPC 码由BG和相应的移位因子Z构成,即PCM定义:BG中的1替换为大小为ZxZ的循环移位矩阵,BG中的0被替换为ZxZ的全零矩阵。

循环移位矩阵的移位值Pij,表示BG中第(i,j )个非0元素对应的移位矩阵为ZxZ往右移位Pij次,它由Pij=mod(Vij, Z)计算得到,其中Vij是BG中第 (i, j)个非“0”元素位置对应的整数,mod(x,y)表示x对y取余。

为了支持不同的信息块长度,同时考虑描述复杂度和性能的折中,5G NR定义了8组扩展因子Z,即Z=ax2^j,其中a∈{2,3,5,7,9,11,13,15},j=0, 1…5。Z的取值是2≤Z≤384内的正整数。这些值分为8个集合,每个集合对应一个a。对于每个a,5G NR基于每个BG定义了一个PCM,对应这个集合中最大的Z。BG1和BG2分别对应8套PCM。

码块分段

码块分段是信道编码的重要一环。TB的大小往往远大于CB所能编码的最大信息比特数,所以需要吧一个TB分割成多个CB,然后分别对各个CB进行编码,得到对应的多个编码比特序列。

速率匹配

HARQ是提升系统吞吐量的一项关键技术,而5G NR系统中LDPC码的RL结构,可以增量生成校验比特,很好地支持IR-HARQ和不同的传输码率。另一方面,QC-LDPC码离散的移位因子大小等也对信息块大小和码长的支持提出一些限制, 需要通过额外的填充和打孔等实现速率匹配。

对速率匹配得到的编码比特进行交织后再调制,即比特交织编码调制是保证LDPC 码在高阶调制和衰落信道下性能稳定的另一个基本保障。

与LTE Turbo码类似,5GNR通过循环缓存实现HARQ和速率匹配:将编码比特存储在循环缓存中,每次传输时根据冗余版本从循环缓存中顺序读取,实现速率匹配。

另外,LDPC码支持有限缓存速率匹配(LBRM,Limited Buffer Rate Matching)。对于初传需要打掉的大列重对应的2Z个系统比特,标准规定不进入循环缓存,即永远不会传输。对于每次传输,速率匹配的读取位置由冗余版本rv决定,且是移位因子Z的整数倍。