状态机

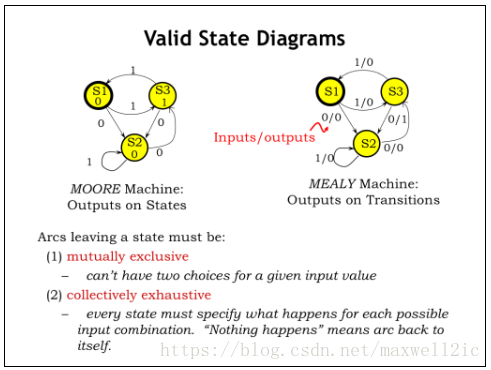

状态机分moore机和mealy机,其中:

- moore机的输出只与状态有关

- mealy机的输出与当前状态和输入都有关

- 体现在状态转移图上就是,moore机的输出在状态圆圈内,mealy机的输出在转移曲线上

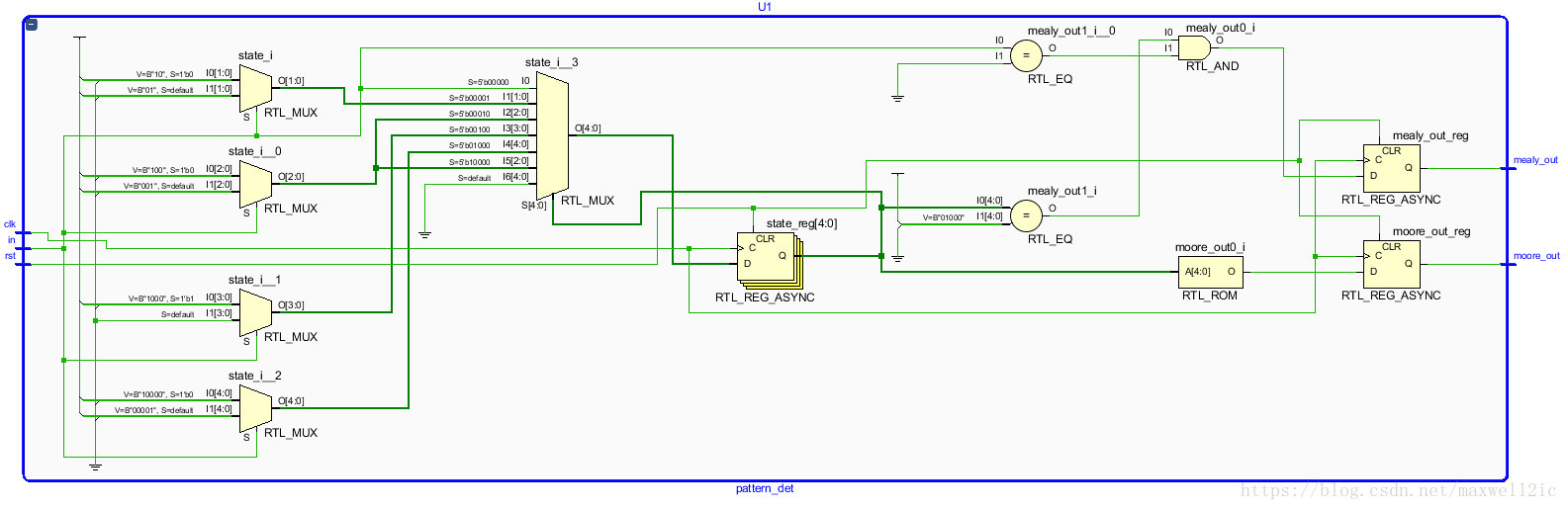

- 体现在verilog代码中就是,moore机的最后输出逻辑只判断state,mealy机的输出逻辑中判断

state && input

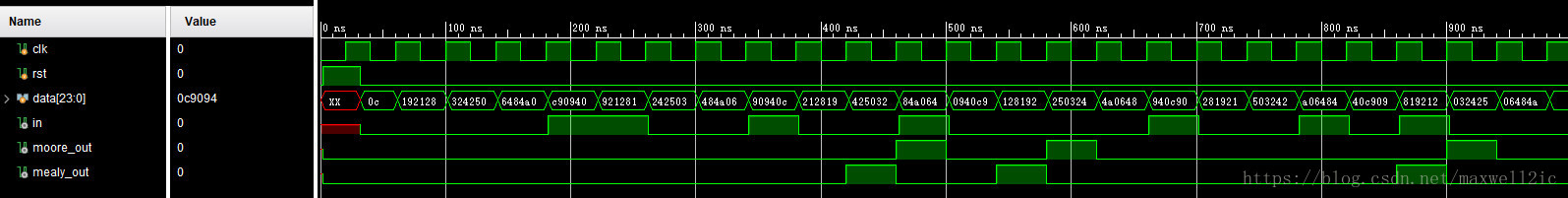

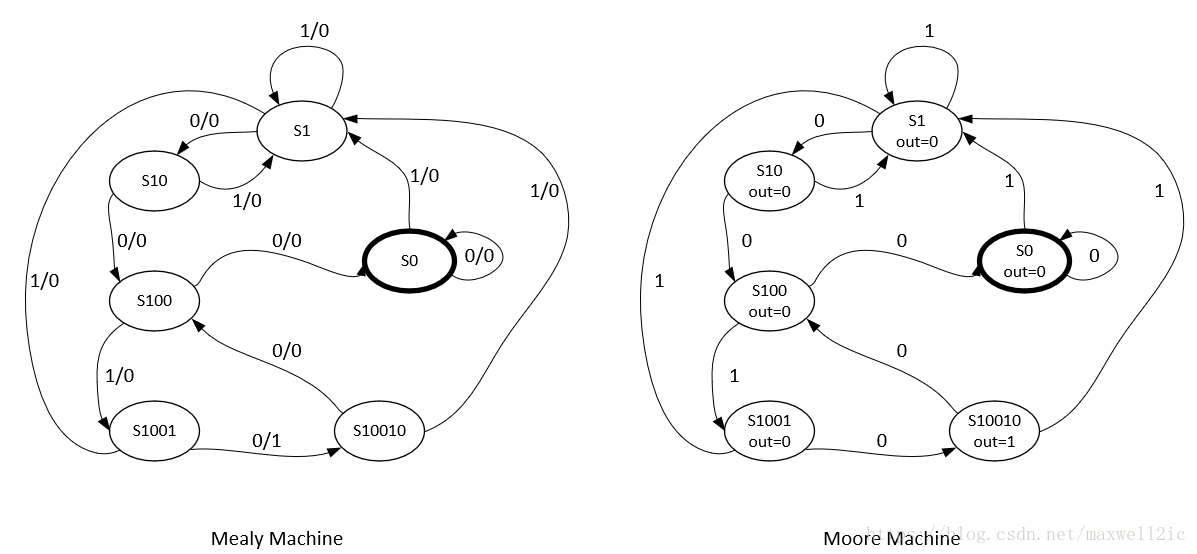

下面以检测10010序列为例说明。

状态转移图

测试代码

module pattern_det(

input in, clk, rst,

output reg moore_out, mealy_out

);

reg [4:0] state;

localparam S0 = 5'b00000;

localparam S1 = 5'b00001;

localparam S10 = 5'b00010;

localparam S100 = 5'b00100;

localparam S1001 = 5'b01000;

localparam S10010 = 5'b10000;

always @(posedge clk or posedge rst) begin

if (rst) begin

state <= S0;

end

else begin

case(state)

S0: if (in == 1) state <= S1;

else state <=S0;

S1: if (in == 0) state <= S10;

else state <= S1;

S10: if (in == 0) state <= S100;

else state <= S1;

S100: if (in == 1) state <= S1001;

else state <= S0;

S1001: if (in ==0) state <= S10010;

else state <= S1;

S10010: if (in == 0) state <= S100;

else state <= S1;

default: state <= S0;

endcase

end

end

//Moore Machine

always @(posedge clk or posedge rst) begin

if (rst) begin

moore_out <= 1'b0;

end

else begin

// moore_out <= (state == S10010) ? 1'b1 : 1'b0;

case(state)

S10010: moore_out <= 1'b1;

default: moore_out <= 1'b0;

endcase

end

end

//Mealy Machine

always @(posedge clk or posedge rst) begin

if (rst) begin

mealy_out <= 1'b0;

end

else begin

mealy_out <= (state == S1001 && in ==0) ? 1'b1 : 1'b0;

end

end

endmodule`timescale 1ns/100ps

module pattern_det_tb;

reg clk, rst;

reg [23:0] data;

wire in, moore_out, mealy_out;

assign in = data[23];

initial begin

clk = 1'b0;

rst = 1'b0;

#2 rst = 1'b1;

#30 rst = 1'b0;

data = 20'b1100_1001_0000_1001_0100;

#20000 $finish;

end

always #20 clk = ~clk;

always @(posedge clk)

#2 data = {data[22:0], data[23]};

pattern_det U1(

.in(in),

.clk(clk),

.rst(rst),

.moore_out(moore_out),

.mealy_out(mealy_out)

);

endmodule

可以看出综合出的电路中mealy机最后输出是input和state在做与运算。

moore机因为是到达S10010状态才输出,mealy机则是S1001状态下输入为0就输出,所以moore机的输出比mealy机输出慢一个周期。