оглавление

3.4 Подтверждение (ACK) и неподтверждение (NACK)

3.5 Адрес ведомого устройства и биты чтения и записи

2. Введение в EEPROM (AT24C64)

2. Время чтения и записи EEPROM.

1. Протокол связи I2C

1. введение шины I2C

Шина I2C - это простая двусторонняя двухпроводная синхронная последовательная шина, разработанная Philips . Для передачи информации между устройствами, подключенными к шине, требуется всего два провода.

Ведущее устройство используется для запуска шины для передачи данных и генерации часов, чтобы открыть устройство для передачи.В это время любое адресуемое устройство рассматривается как ведомое устройство. Отношения между ведущим и ведомым, отправка и прием по шине не постоянны, но зависят от направления передачи данных в это время. Если хост хочет отправить данные на подчиненное устройство, хост сначала обращается к подчиненному устройству, затем активно отправляет данные на подчиненное устройство, и, наконец, хост прекращает передачу данных; если хост хочет получить данные от подчиненного устройства, главное устройство сначала обращается к подчиненному устройству. Затем хост получает данные, отправленные с устройства, и, наконец, хост завершает процесс приема. при этих обстоятельствах. Хост отвечает за генерацию тактовых импульсов и завершение передачи данных.

Шина I2C является признанным мировым стандартом. Более 50 компаний производят интегральные схемы, реализованные в более чем 1000 различных местах. Кроме того, общая шина i2c используется в различных архитектурах управления, таких как шина системного управления (SMBus), шина управления питанием (PMBus), интеллектуальный интерфейс управления платформой (IPMI), канал данных дисплея (DDC) и расширенная архитектура телекоммуникационных вычислений (ATCA). ).

2. Характеристики шины I2C

- Требуются только две шины: линия последовательных данных (SDA) и линия последовательных часов (SCL);

- Каждое устройство, подключенное к шине, адресуется программным обеспечением с уникальным адресом и простыми отношениями ведущий / ведомый;

- Это настоящая шина с несколькими мастерами.Если два или более мастеров инициируют передачу данных в одно и то же время, она идет с обнаружением коллизий и арбитражем для предотвращения повреждения данных;

- Последовательная, 8-битная, двусторонняя передача данных, до 100 кбит / с в стандартном режиме, 400 кбит / с в быстром режиме и 1 Мбит / с в быстром режиме +. Кроме того, скорость может достигать 100 кбит / с в высокоскоростном режиме. До 3,4 Мбит / с;

- Последовательная, 8-битная, однонаправленная передача данных до 5 Мбит / с в сверхбыстром режиме;

- Встроенная фильтрация отклоняет выбросы на линии передачи данных шины для поддержания целостности данных;

-

Количество интегральных схем, которые могут быть подключены к одной шине, ограничено только максимальной емкостью шины. При определенных условиях может быть разрешена большая емкость.

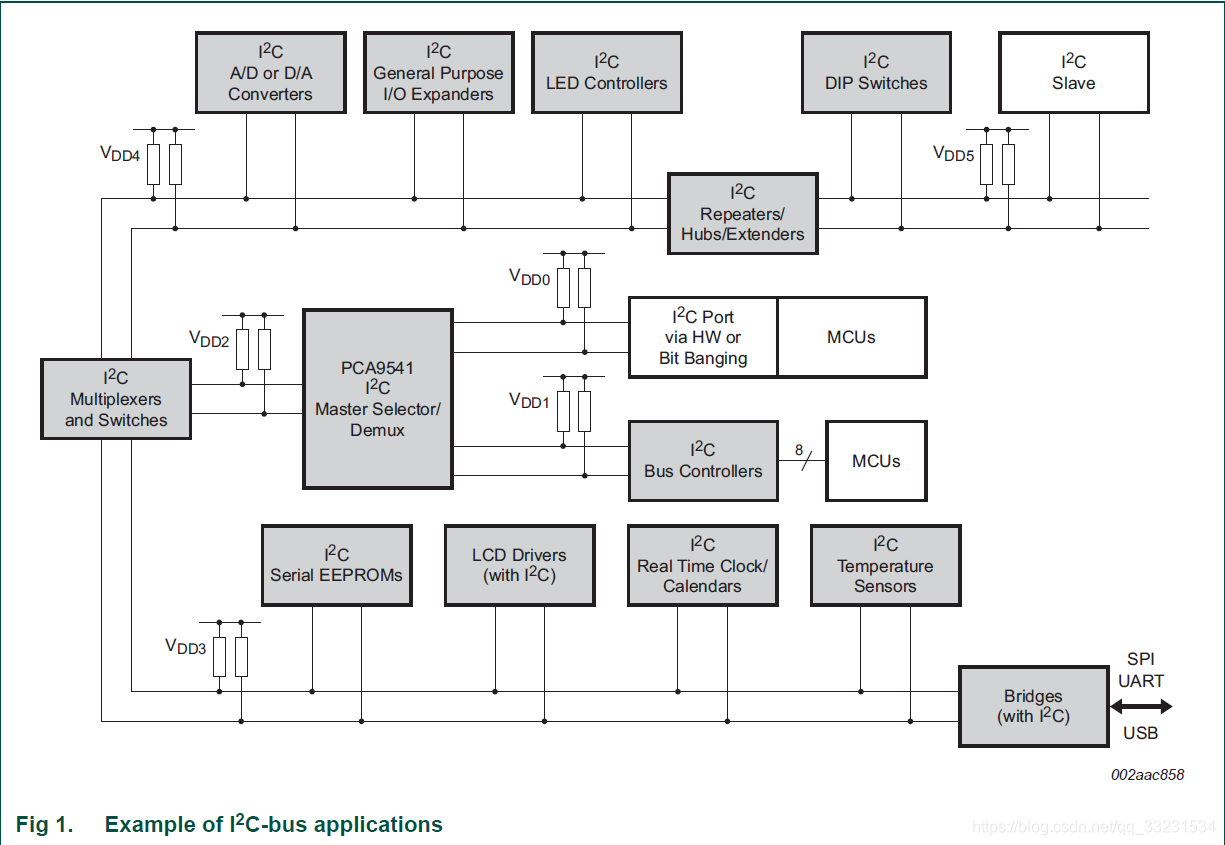

На следующем рисунке показан пример приложения шины I2C:

Можно видеть, что множество устройств шины I2C подключено к двум шинам SDA и SCL, и данные передаются по шине I2C одновременно. Схема топологии шины, подключенной к FPGA, выглядит следующим образом:

3. Протокол шины I2C

Двухпроводная последовательная линия данных (SDA) и последовательные часы (SCL) передают информацию между устройствами, подключенными к шине. Каждое устройство имеет уникальный адрес (будь то микроконтроллер, драйвер ЖК-дисплея, память или интерфейс клавиатуры), который может работать как передатчик или приемник в зависимости от функции устройства. Драйвер ЖК-дисплея может быть просто приемником, а память может принимать и передавать данные. Помимо передатчика и приемника, устройство также может рассматриваться как ведущее или ведомое устройство при передаче данных.

На рисунке ниже показан пример конфигурации шины i2c с использованием двух микроконтроллеров. В этом примере показаны отношения "главный-подчиненный" и "прием-отправка" на шине i2c. Обратите внимание, что эти отношения не являются постоянными, а зависят только от направления передачи данных в данный момент.

Ведущее устройство всегда отвечает за генерацию тактового сигнала на шине i2c; когда данные передаются по шине, каждое ведущее устройство генерирует свой собственный тактовый сигнал. Синхронизирующий сигнал шины будет изменяться только тогда, когда линия синхронизации будет отключена нижним ведомым устройством или подвергнута арбитражу другим ведущим.

3.1 сигналы SDA и SCL

И SDA, и SCL являются двунаправленными линиями, подключенными к положительному напряжению питания через источник тока или подтягивающий резистор (как показано на рисунке ниже). Выходной каскад устройства, подключенного к шине, должен иметь открытый сток или открытый коллектор для выполнения функции линейной суммы. Данные по шине I2C могут передаваться со скоростью до 100 кбит / с в стандартном режиме, со скоростью до 400 кбит / с в быстром режиме, 1 Мбит / с в быстром режиме + и до 1 Мбит / с в высокоскоростном режиме 3,4 Мбит / с. Емкость шины ограничивает количество интерфейсов, подключенных к шине.

3.1 Достоверность данных

Данные на линии SDA должны оставаться стабильными в течение высокого периода тактовой частоты. Только когда тактовый сигнал на линии SCL низкий, высокое или низкое состояние линии данных может быть изменено

(см. Рисунок ниже). Тактовый импульс генерируется для каждого переданного бита данных. Следовательно, при разработке сигнала наилучшая ситуация состоит в том, что данные на линии данных SDA изменяются, когда линия синхронизации scl находится в середине низкого уровня, а данные на линии данных SDA получаются, когда линия синхронизации находится в середине высокого уровня.

3.2 Стартовые и стоповые биты

Вся передача данных начинается с START (S) и заканчивается STOP (P) (см. Рисунок ниже).

I2C bus idle: SDA и SCL оба имеют высокий уровень;

Стартовый бит протокола I2C: когда SCL высокий, SDA имеет задний фронт;

стоповый бит протокола I2C: когда SCL высокий, SDA имеет передний фронт.

Условия запуска и остановки всегда генерируются ведущим устройством. После условия запуска автобус считается занятым. Автобус снова простаивает в течение определенного периода времени после условия остановки. Если вместо условия остановки генерируется повторный пуск (Sr), шина останется занятой. В этом отношении условия запуска (S) и повторного запуска (Sr) функционально одинаковы.

3.3 Формат передачи 1 байта

Длина каждого байта, передаваемого в строке данных SDA, должна составлять 8 бит. Количество байтов, которые можно передать за одну передачу, не ограничено. За каждым байтом должен следовать бит подтверждения (ACK). Данные передаются из самого старшего бита (MSB) байта (см. Рисунок ниже). Если ведомое устройство не может получить или отправить другой полный байт данных до тех пор, пока оно не выполнит некоторые другие функции, такие как обслуживание внутренних прерываний, оно может удерживать линию синхронизации scl на низком уровне и заставить ведущее устройство перейти в состояние ожидания. Когда ведомое устройство готово к получению другого байта данных, оно продолжает передавать данные и освобождает линию синхронизации SCL.

3.4 Подтверждение (ACK) и неподтверждение (NACK)

Ответ происходит после каждого байта. Бит подтверждения отвечает, указывая, что байт был успешно получен и можно отправить еще один байт. Ведущее устройство генерирует все тактовые импульсы, включая девятый тактовый импульс бита подтверждения. Ответный сигнал определяется следующим образом: во время ответа на тактовый импульс передатчик освобождает линию SDA, а приемник может подтянуть линию SDA к низкому уровню и поддерживать его на низком уровне во время высокого уровня тактовой частоты.

Когда SDA остается на высоком уровне в течение 9-го тактового импульса, это определяется как сигнал неподтверждения. Затем ведущее устройство может сгенерировать условие остановки, чтобы завершить передачу, или сгенерировать условие повторного запуска, чтобы начать новую передачу. Есть пять условий для генерации NACK:

- На шине нет приемника с переданным адресом, поэтому нет устройства, которое могло бы ответить.

- Получатель не может принимать или отправлять, потому что он выполняет некоторые функции в реальном времени и не готов начать связь с мастером.

- В процессе передачи приемник получает данные или команды, которые он не понимает.

- Во время передачи получатель не может получить больше байтов данных.

- Главный приемник должен послать сигнал конца передачи подчиненному передатчику.

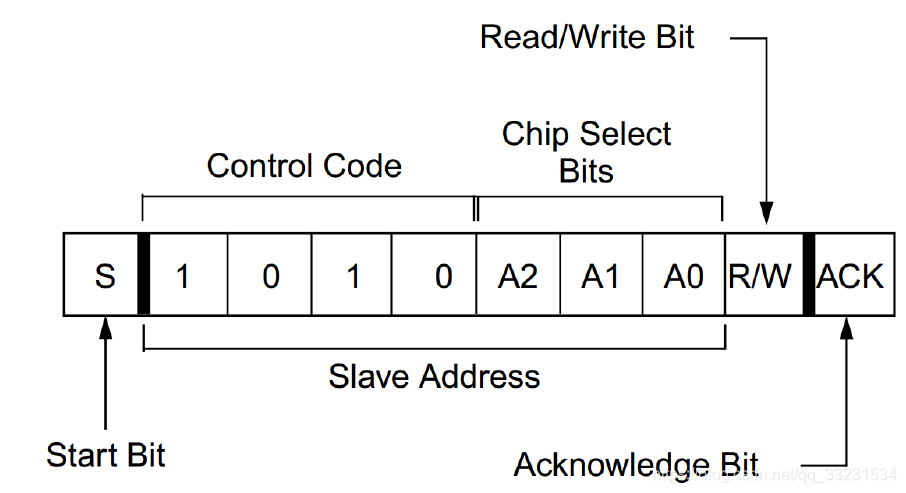

3.5 Адрес ведомого устройства и биты чтения и записи

Адрес ведомого устройства является основой протокола I2C для адресации устройств на шине при передаче данных. Передача данных осуществляется в формате, показанном на рисунке ниже. После условия запуска отправьте адрес ведомого устройства. Этот адрес имеет длину 7 бит, за ним следует бит направления данных (R / W) - «0» означает передачу (запись), а «1» означает запрос данных (чтение) (см. Следующий рисунок 2). Передача данных всегда заканчивается условием остановки (P), создаваемым ведущим устройством. Однако, если ведущее устройство все еще желает обмениваться данными по шине, оно может сгенерировать условие повторного запуска (Sr) и адрес без создания условия остановки.

Адрес ведомого устройства обычно представляет собой комбинацию фиксированных и переменных битов. Так называемое фиксированное положение - это устройство, которое определяется как неизменяемое и считается неуправляемым, в то время как переменный бит обычно является аппаратным обеспечением устройства, которое может использоваться для аппаратного подключения пользователем. Оно определяется в соответствии с аппаратным подключением пользователя. Например, 7-битное устройство на рисунке ниже В адресе первые четыре цифры 1010 зафиксированы на заводе, а последние три цифры - это аппаратные контакты устройства, которые пользователи могут изменить.

Для разных устройств формат передачи I2C немного отличается. Для запоминающих устройств он также имеет адресный номер памяти. После того, как ведущее устройство отправит адрес устройства и память ведомого устройства ответит, ведущее устройство должно отправить другие 8- или 16-разрядные данные адреса памяти. После выбора адреса памяти и ожидания ответа от ведомого устройства ведущее устройство отправляет данные или считывает данные из адреса памяти.

Приведенное выше описание протокола I2C относится к спецификации шины I2C UM10204 и руководству пользователя, версия 4-13 февраля 2012 г. ( спецификация шины i2c и руководство пользователя ) компании NXP Semiconductors . Адрес для загрузки руководства по данным: https://download.csdn.net/download/qq_33231534/12501985.

2. Введение в EEPROM (AT24C64)

1. Синхронизация шины EEPROM

AT24C32 / 64 обеспечивает 32 768/65 536-битную последовательную электрически стираемую и программируемую постоянную память (EEPROM), организованную в 4096/8192 слов по 8 бит каждое. Каскадная функция этого устройства позволяет до 8 устройств использовать общую 2-проводную шину. Устройство оптимизировано для многих промышленных и коммерческих приложений, где необходима работа с низким энергопотреблением и низким напряжением. Схема выводов микросхемы выглядит следующим образом:

Аппаратные функции следующие:

| Штырь | Описание |

| SCL | Последовательный вход синхронизации, вход SCL используется для синхронизации данных в каждое устройство EEPROM на переднем фронте и для синхронизации данных с каждого устройства на заднем фронте. |

| ПДД | Для линии последовательной передачи данных вывод SDA представляет собой двухстороннюю последовательную передачу данных.Этот вывод управляется открытым стоком и может быть подключен к любому количеству других устройств с открытым стоком или открытым коллектором. |

| A2, A1, A0 | Ввод адреса устройства.Когда эти контакты подключены жестко, к одной системе шины можно адресовать до 8 устройств 32K / 64K. Когда контакты не подключены жестко, значения по умолчанию A2, A1 и A0 равны нулю. |

| WP | Защита от записи: при подключении к GND вход защиты от записи позволяет выполнять нормальные операции записи; когда WP подключен к VCC, все операции записи в верхней части памяти (8 / 16K) ограничены; если не подключен, WP внутренне опускается К GND. |

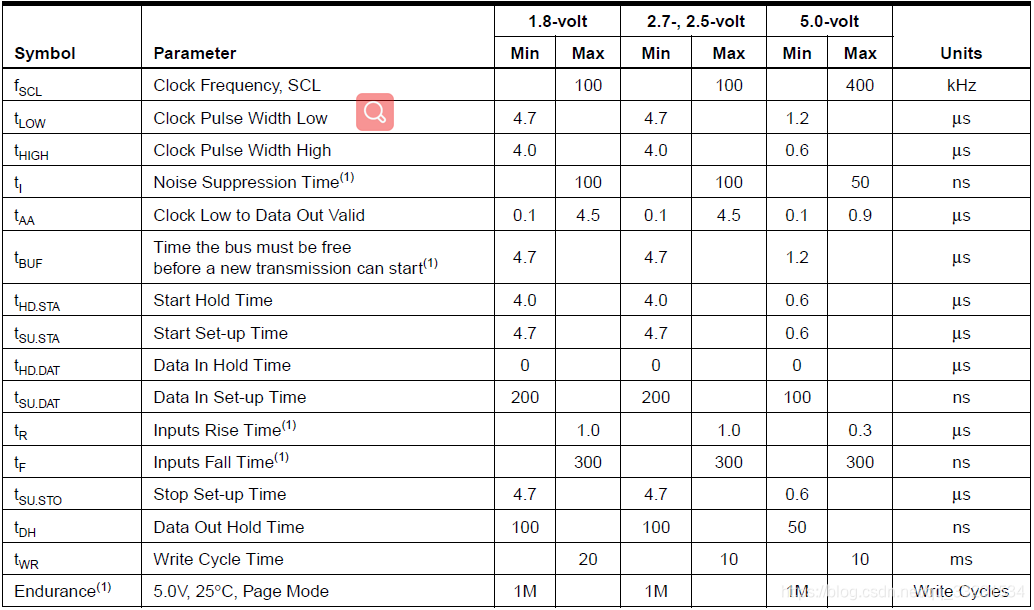

Расписание автобуса следующее:

Последовательность цикла записи показана на рисунке ниже: Время цикла записи - это время от эффективного останова последовательности записи до конца внутреннего цикла очистки / записи.

По сравнению с синхронизацией на двух вышеприведенных рисунках таблица характеристик переменного тока выглядит следующим образом:

Некоторые основные операции устройства следующие:

- Тактовая частота и преобразование данных: вывод SDA обычно подтягивается высоко с внешними устройствами. Данные на выводе SDA могут быть изменены только во время низкого уровня SCL (см. Временную диаграмму достоверности данных). Изменения данных SDA во время пиковых периодов вероятности нежелательной почты будут указывать на условия запуска или остановки, как определено ниже.

- Условие запуска: когда SCL высокий, SDA имеет задний фронт.

- Условие останова: когда SCL высокий, SDA имеет нарастающий фронт. После прочтения последовательности команда остановки переводит EEPROM в режим ожидания.

- Подтверждение (ACK): все адреса и слова данных последовательно передаются или принимаются из EEPROM в 8-битных словах. EEPROM отправляет 0 (низкий уровень) в 9-м тактовом цикле, чтобы подтвердить, что он получил каждое слово.

- Режим ожидания: AT24C32 / 64 - это режим ожидания с низким энергопотреблением, состояние включения: а) после включения питания; б) после получения стопового бита и завершения внутренних операций.

Допустимые биты данных, условия запуска и остановки и выходная реакция на приведенном выше рисунке такие же, как и в упомянутом выше протоколе I2C, поэтому я не буду вдаваться в подробности здесь.

2. Время чтения и записи EEPROM.

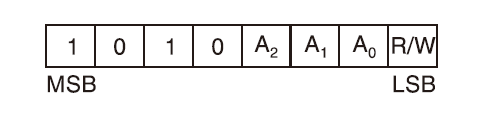

2.1 Адрес устройства

EEPROM 32K / 64K требует 8-битного адресного слова устройства, чтобы чип мог выполнять операции чтения или записи в условиях запуска. Адресное слово устройства состоит из принудительной последовательности первых четырех битов 1, 0, как показано на рисунке. Это общее для всех устройств с 2-проводным EEPROM. 32K / 64KEEPROM использует три бита адреса устройства A2, A1, A0, что позволяет подключать до 8 устройств к одной шине. Эти биты могут быть установлены с помощью проводных входных контактов. Выводы A2, A1 и A0 используют внутренние выделенные схемы.Если выводам разрешено плавать, они будут смещены на низкий логический уровень.

Восьмой бит адреса устройства - это бит выбора операции чтения / записи. Если этот бит высокий, инициируется операция чтения; если этот бит низкий, инициируется операция записи. Когда EEPROM сравнивает адрес, отправленный ведущим устройством, EEPROM выдаст 0. Если это не то, устройство вернется в режим ожидания.

2.2 Операция записи

2.2.1 Запись байта

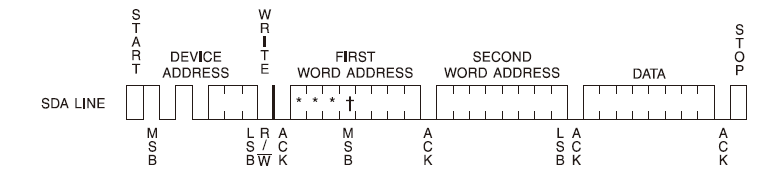

Для операции записи требуются два 8-битных адреса слова данных после адресного слова устройства и ответа (ACK). После получения адреса первого слова данных EEPROM снова ответит 0. После получения адреса второго слова данных EEPROM снова отвечает 0. Затем передайте данные для записи и прекратите чтение и запись после того, как EEPROM ответит 0. В это время EEPROM входит во внутренний цикл записи по времени энергонезависимой памяти . Все входы отключены во время этого цикла записи, и EEPROM не будет отвечать до конца записи.

2.2.2 Запись страницы

EEPROM 32K / 64K может выполнять операции записи 32-байтовых страниц. Метод начала записи страницы такой же, как запись байта, но микроконтроллер не войдет в условие остановки после отправки первого слова данных. И наоборот, после того, как EEPROM подтвердит, что он получил первое слово данных, микроконтроллер может передать еще до 31 слова данных. EEPROM ответит нулем после получения каждого слова данных. Микроконтроллер должен использовать условие остановки, чтобы завершить последовательность записи страницы (см. Рисунок выше).

Адрес слова данных ниже 5 бит (32) внутренне увеличивается после получения каждого слова данных. Биты адреса слова данных, превышающие 5 бит, не увеличиваются, и позиция строки страницы памяти сохраняется. Когда внутренне сгенерированный адрес слова достигает границы страницы, следующий байт помещается в начало той же страницы. Если в EEPROM передается более 32 слов данных, адрес слова данных будет "катиться", а предыдущие данные будут перезаписаны.

2.3 Операция чтения

За исключением того, что бит выбора чтения / записи в адресном слове устройства установлен в 1, режим начала операции чтения такой же, как и у операции записи. Есть три операции чтения: чтение текущего адреса, чтение случайного адреса и последовательное чтение.

2.3.1 Текущий адрес чтения

Внутренний счетчик адреса слова данных хранит последний адрес, к которому был осуществлен доступ во время последней операции чтения или записи, с приращением на 1. Пока мощность чипа остается неизменной, этот адрес остается действительным между операциями. Адрес "прокручивается" во время чтения - от последнего байта последней страницы памяти до первого байта первой страницы. Адрес "прокручивается" во время записи - от последнего байта текущей страницы до первого байта той же страницы.

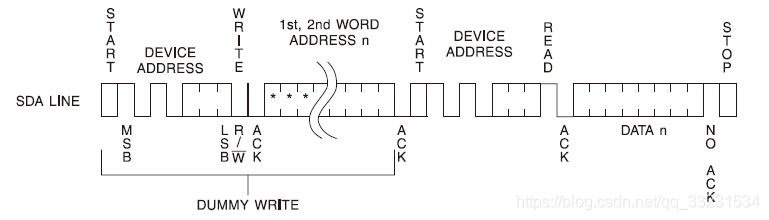

2.3.2 Чтение случайного адреса

Для случайного чтения требуется «псевдобайтная» последовательность записи для загрузки адреса слова данных. Как только адресное слово устройства и адрес слова данных записаны и подтверждены EEPROM, микроконтроллер должен сгенерировать другое условие запуска, а затем микроконтроллер начинает операцию чтения текущего адреса, отправляя адрес устройства и бит выбора чтения / записи в высокий уровень. EEPROM подтверждает адрес устройства и непрерывно считает слова выходных данных. Микроконтроллер не реагирует на ноль, но генерирует условие остановки (см. Рисунок выше).

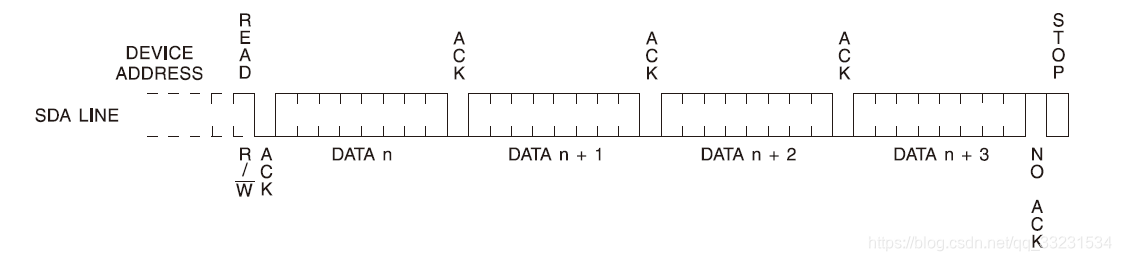

2.3.3 Последовательное чтение

Последовательное чтение начинается с чтения текущего адреса или чтения случайного адреса. После того, как микроконтроллер получает слово данных, он отвечает ACK. Пока EEPROM получает ответ, он будет продолжать увеличивать адрес слова данных и последовательные слова данных вывода тактовых импульсов. Когда предел адреса памяти достигнут, адрес слова данных будет "катиться", и последовательное чтение продолжится. Когда микроконтроллер не отвечает 0, но отправляет условие остановки, операция последовательного чтения завершается.

Приведенные выше объяснения EEPROM AT24C64 основаны на руководстве ATMEL по данным микросхем AT24C32 / AT24C64. Те, кому нужно посмотреть или загрузить, могут перейти на следующий веб-сайт: https://pdf1.alldatasheet.com/datasheet-pdf/view/56068/ATMEL/ AT24C64.html